计算机芯片的发展历程,以及所有架构的未来趋势(11)

电脑杂谈 发布时间:2019-04-27 20:29:13 来源:网络整理在百度百科中,对李世默的介绍是这样的:加州大学伯克利分校学士,斯坦福大学工商管理学硕士,复旦大学国际关系及公共事务学院博士,是一名风险投资家和政治学学者,春秋综合研究院研究员、中欧国际工商学院校董及中欧出版集团副,中欧创业营讲师、成为资本创始人及执行董事,美国阿斯本研究所研究员,美国卡内基和平基金会顾问,伯克利加州大学艺术博物馆董事,是纽约时报、南华早报、环球时报,外交事务杂志,基督教科学箴言报以及郝芬顿邮报撰稿人。双核架构,增加了一个risc核的高效协处理器,xgate模块,专门用于处理中断任务,可以将主核cpu从执行耗时的中断处理程序工作中解放出来,专注于执行与应用有关的任务,实现更好的实时事件处理,xgate采用risc指令核,代码高效,主频运行速率可达到主核的2倍。

RISC-V 是一个模块化指令集。一小部分指令运行完整的开源软件堆栈,然后是可选的标准扩展,设计人员可以根据需要包含或省略。该基础包括 32 位地址和 64 位地址版本。RISC-V 只能通过可选扩展来增长;即使架构师不接受新的扩展,软件堆栈仍然运行良好。专有架构通常需要向上的二进制兼容性,这意味着当处理器公司添加新功能时,所有未来的处理器也必须包含它。对于 RISC-V,情况并非如此,所有增强功能都是可选的,如果应用程序不需要,可以删除。以下是目前为止的标准扩展,使用代表其全名的缩写:

M. 整型数乘法/除法;

A. 原子内存操作;

F/D. 单/双精度浮点数;

C. 压缩指令。

更少指令。RISC-V 的指令少得多。base 中有 50 个指令,与原始 RISC-I 相近。高性能计算机发展历程剩余的标准扩展(M、A、F 和 D)增加了 53 条指令,再加上 C 又增加了 34 条,共计 137 条。ARMv8 有超过 500 条指令。

更少的指令格式。RISC-V 的指令格式非常少,只有六种,而 ARMv8 至少有 14 种。

简单性减少了设计处理器和验证硬件正确性的工作量。由于 RISC-V 的目标范围覆盖了数据中心芯片到物联网设备,因此设计验证可能是开发成本的重要组成部分。

RISC-V 是一种简洁的设计,诞生 25 年后,它的设计师从其前辈的错误中吸取了教训。与第一代 RISC 架构不同,它避免了微架构或技术依赖的功能(例如延迟分支和延迟加载)或创新(例如寄存器窗口),这些功能被编译器技术的进步所取代。

最后,RISC-V 通过为自定义保留大量操作码空间来支持 DSA。

安全专家不相信不可见的安全性,因此开放式实现很有吸引力,开放式实现需要开放式架构。

除 RISC-V 外,英伟达 2017 年还宣布一个免费开放的架构,称之为英伟达深度学习(NVDLA),这是一种可扩展的可配置 DSA,用于机器学习推理。配置选项包括数据类型(int8、int16 或 fp16)和二维乘法矩阵的大小。模具尺寸从 0.5 mm^2 到 3 mm^2,功率从 20 毫瓦到 300 毫瓦。ISA、软件堆栈和实现都是开放的。

开放的简单架构与安全性具有协同作用。首先,安全专家不相信安全性,因此开放式实现很有吸引力,而开放式实现需要开放式架构。同样重要的是增加可以围绕安全架构进行创新的人员和组织的数量。专有架构限制了员工的参与,但开放式架构允许学术界和工业界的所有最佳人才帮助提高安全性。最后,RISC-V 的简单性使其实现更容易检查。此外,开放式架构、实现、软件堆栈以及 FPGA 的可塑性意味着架构师可以部署和评估新颖的解决方案,并每周而不是每年迭代它们。虽然 FPGA 比定制芯片慢 10 倍,但这种性能仍然足以支持用户,同时带来安全创新,解决真正的攻击。我们希望开放式架构成为架构师和安全专家进行硬件/软件协同设计的典范。

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/jisuanjixue/article-94568-11.html

-

-

黄培泉

黄培泉#舞蹈担当易烊千玺#

-

萧楚材

萧楚材坚决击沉

我的diy之路篇十:618装一台RGB主机如何选?2080+9900K高性能游戏主机搭建

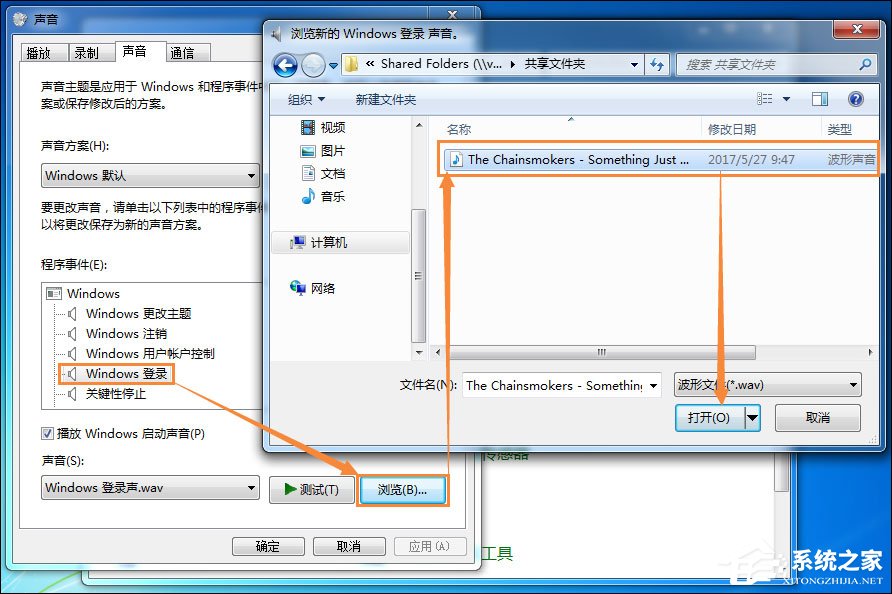

我的diy之路篇十:618装一台RGB主机如何选?2080+9900K高性能游戏主机搭建 操作方法:如何设置Windows启动音乐? Win7电脑启动音乐设置方法

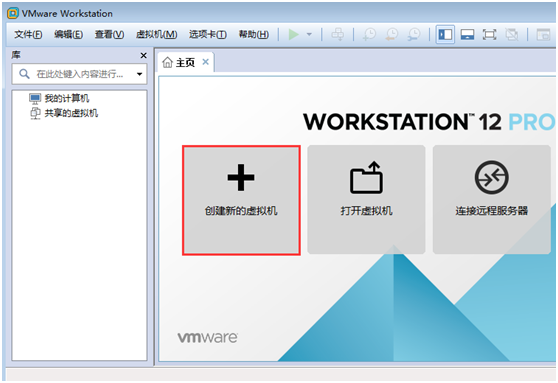

操作方法:如何设置Windows启动音乐? Win7电脑启动音乐设置方法 wmware虚拟机怎么安装win764位系统的方法分享分享

wmware虚拟机怎么安装win764位系统的方法分享分享 深层技术与雨林风之间的区别

深层技术与雨林风之间的区别

真正打海战是不行的