计算机芯片的发展历程,以及所有架构的未来趋势(5)

电脑杂谈 发布时间:2019-04-27 20:29:13 来源:网络整理据福克斯新闻报道,美国计算机学会(acm)宣布了 2016 年度图灵奖(turing award)得主:英国计算机科学家、万维网(world wide web)的发明者、mit 和牛津大学教授蒂姆·。#致敬赠书# @nlpjob 联合 @图灵教育 限时送出2本计算机科学巨著,算法领域经典《计算机程序设计艺术 卷1:基本算法(第3版)》,高德纳(donald ervin knuth),1938年1月10日生于美国,现代计算机科学先驱,1974年图灵奖得主。

VLIW、EPIC、Itanium

下一个 ISA 创新应该是对 RISC 和 CISC 的继承。超长指令字(VLIW)及其「表亲」显式并行指令计算机(EPIC)使用了宽指令,其中在每条指令中捆绑了多个独立操作。VLIW 和 EPIC 的拥护者当时认为,单个指令如果可以指定六个独立的操作(两个数据传输、两个整型操作和两个浮点操作),并且编译器技术可以有效地将操作分配到六个指令槽,则硬件可以变得更简单。与 RISC 方法一样,VLIW 和 EPIC 将工作从硬件转移到编译器。

通过合作,英特尔和惠普公司设计了一款基于 EPIC 理念的 64 位处理器来取代 32 位 x86。英特尔和惠普公司对第一款 EPIC 处理器(Itanium)的期望很高,但实际情况与开发商的早期声明并不相符。虽然 EPIC 方法适用于高度结构化的浮点程序,但它很难实现具有较少可预测的缓存丢失或较不可预测分支的整型程序的高性能。正如 Donald Knuth 后来指出:「Itanium 方法...... 原被认为非常赞,直到事实证明所希望的编译器基本上不可能写出来。」专家们注意到 Itanium 的延迟和表现不佳,并借鉴泰坦尼克号事件重新将其命名为「Itanic」。市场再次失去了耐心,导致 64 位版本的 x86 成为 32 位 x86 的继承者,而不是 Itanium。

好消息是 VLIW 仍然适用于较窄范围的应用程序、小程序、更简单的分支和省略缓存,包括数字信号处理。

PC 和后 PC 时代的 RISC vs. CISC

AMD 和英特尔使用了 500 人的设计团队和顶尖半导体技术来减少 x86 和 RISC 的性能差距。再次受到简单流水线 vs 复杂指令性能优势的启发,指令在运行中将复杂的 x86 指令转换为类似 RSIC 的内部微指令。然后 AMD 和英特尔将 RISC 微指令的执行流水线化。RISC 设计师关于性能分离指令、数据缓存、芯片二级缓存、深度流水线,以及同时获取和执行多个指令的任何想法,都可以用在 x86 的设计上。AMD 和英特尔在 2011 年 PC 时代的巅峰期出了大约 3 亿 5 千万个微处理器。PC 行业的高产量和低利润同样意味着比 RISC 计算机更低的价格。

鉴于每年全球销售的数亿台 PC,PC 软件成为一个巨大的市场。虽然 Unix 市场的软件提供商会为不同的商业 RISC ISA-Alpha、HP-PA、MIPS、Power 和 SPARC 提供不同的软件版本,但 PC 市场却享有单一的 ISA,因此软件开发商提供了「收缩包装」软件,只与 x86 ISA 二进制兼容。2000 年,更大的软件基础、类似的性能和更低的价格使 x86 在台式机和小型服务器市场中占据主导地位。

苹果公司在 2007 年帮助推动了后 PC 时代。智能手机公司不再购买微处理器,而是采用其他公司的设计(包括 ARM 的 RISC 处理器)构建自己的芯片系统(SoC)。移动设备设计人员对芯片面积和能效以及性能进行评估,表明 CISC ISA 设计的不足之处。此外,物联网的到来大大促进了处理器的数量以及芯片尺寸、功率、成本和性能所需的权衡。这种趋势增加了设计时间和成本的重要性,进一步使 CISC 处理器处于不利地位。在今天的后 PC 时代,x86 出货量自 2011 年达到峰值以来每年下降近 10%,而采用 RISC 处理器的芯片则飙升至 200 亿。如今,99%的 32 位和 64 位处理器都是 RISC。

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/jisuanjixue/article-94568-5.html

-

-

李从谦

李从谦外面的墙上都有

我的diy之路篇十:618装一台RGB主机如何选?2080+9900K高性能游戏主机搭建

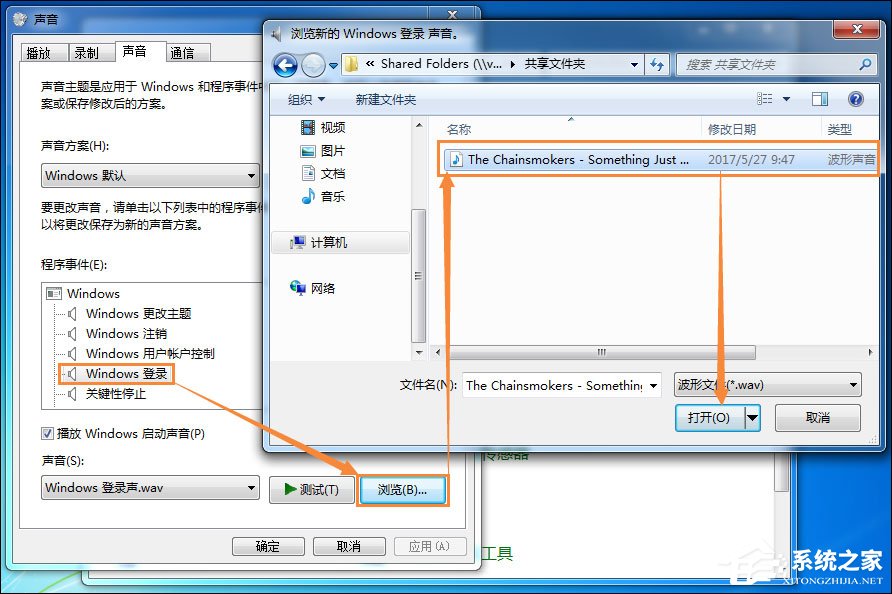

我的diy之路篇十:618装一台RGB主机如何选?2080+9900K高性能游戏主机搭建 操作方法:如何设置Windows启动音乐? Win7电脑启动音乐设置方法

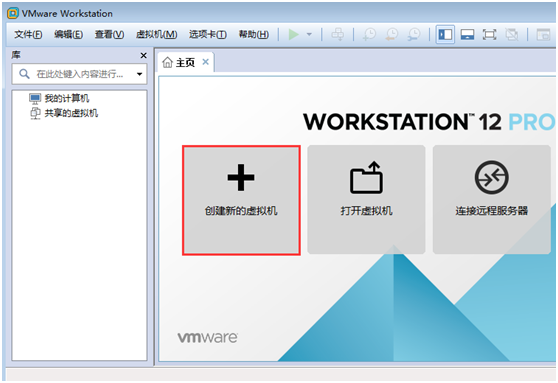

操作方法:如何设置Windows启动音乐? Win7电脑启动音乐设置方法 wmware虚拟机怎么安装win764位系统的方法分享分享

wmware虚拟机怎么安装win764位系统的方法分享分享 深层技术与雨林风之间的区别

深层技术与雨林风之间的区别

收入低的男人也是男人