计算机芯片的发展历程,以及所有架构的未来趋势(4)

电脑杂谈 发布时间:2019-04-27 20:29:13 来源:网络整理从复杂指令集到精简指令集计算机

1980 年代早期,人们对更大型控制存储器中大型微程序使用的复杂指令集计算机(CISC)进行了一些研究。Unix 表明即使操作系统也可以使用高级语言编写,关键问题随之变成了「编译器会生成什么指令?」,而不是「编程者会使用什么汇编语言?」。硬件/软件接口的显著改进为架构创新带来了机会。

图灵奖得主 John Cocke 与其同事为小型计算机开发了更简单的 ISA 和编译器。作为实验,他们将自己研究的编译器的目标重新设定为:仅使用 IBM 360 ISA 中简单的 register-register 操作和 load-store 数据传输,避免更复杂的指令。他们发现使用这个简单的子集时,程序运行速度可快达三倍。Emer 和 Clark 发现 VAX 指令中 20% 的指令需要 60% 的微代码(microcode),但仅占据 0.2% 的执行时间。

David Patterson 把在 DEC 的一次学术休假投入到了研究减少 VAX 指令中的漏洞上。他认为,如果微处理器制造商遵循更大型计算机的 CISC ISA 设计,则它们需要一种修复微代码漏洞的方法。他为此写了一篇论文,但期刊《Computer》却拒绝接收。审稿人认为,使用如此复杂以至于需要修补的 ISA 开发微处理器是很糟糕的。这次拒稿让人们质疑 CISC ISA 在微处理器方面的价值。讽刺的是,现代 CISC 微处理器确实需要包含微代码修复机制,但他被拒稿的主要结果是启发他为微处理器开发更简单的 ISA——精简指令集计算机(RISC)。

这些观察和向高级语言的转移为 CISC 向 RISC 的过渡带来了机会。首先,RISC 指令是经过简化的,因此无需微代码解释器。RISC 指令通常和微指令一样简单,硬件可以直接执行。第二,之前用于 CISC ISA 的微代码解释器的快速内存被用作了 RISC 指令的缓存。(缓存是小而快的内存,临时缓冲近期执行过的指令,因为这样的指令很可能很快就要重新使用。)第三,基于 Gregory Chaitin 图着色方案的寄存器分配器使编译器可以更加容易地有效使用寄存器,这对这些 register-register ISA 是有利的。最后,摩尔定律意味着 1980 年代单块芯片中已有足以包含完整 32 位数据路径的晶体管以及相应的指令和数据缓存。

在今天的后 PC 时代,x86 的出货量从 2011 年的顶峰每年都会下降约 10%,而 RISC 处理器芯片出货量已经激增到了 200 亿。

例如图 1 展示了 RISC-I 和 MIPS 微处理器,它们分别由 UC 伯克利和斯坦福在 1982 与 1983 年开发,它们展示了 RISC 的优势。这些芯片最终都展示在了顶尖电路会议上,即 1984 年的 IEEE 国际固态电路会议。高性能计算机发展历程当时是非常瞩目的成果,因为伯克利和斯坦福的一些能构建超越工业上能构建的微处理器。

图 1:加州大学伯克利分校 RISC-1 和斯坦福大学 MIPS 微处理器。

这些学术界做出的芯片激励了许多公司构建 RISC 微处理器,也是那之后 15 年内最快的芯片。下面的公式解释了处理器的性能:

Time/Program = Instructions / Program x (Clock cycles) / Instruction x Time / (Clock cycle)

DEC 工程师后来表明,更复杂的 CISC ISA 每个程序执行的指令数是 RISC 每个程序的 75%(上式第一项),在使用类似的技术时,CISC 执行每个指令要多消耗 5 到 6 个时钟周期(第二项),使得 RISC 微处理器的速度大约快了 3 倍。

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/jisuanjixue/article-94568-4.html

-

-

韩晓彦

韩晓彦这次的回归感觉都是超棒

-

王若一

王若一确实如此

-

我的diy之路篇十:618装一台RGB主机如何选?2080+9900K高性能游戏主机搭建

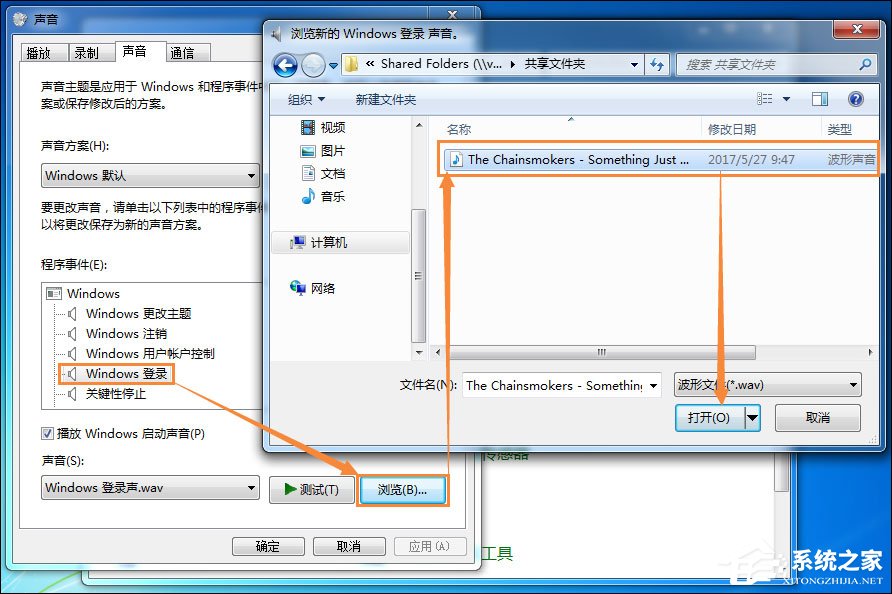

我的diy之路篇十:618装一台RGB主机如何选?2080+9900K高性能游戏主机搭建 操作方法:如何设置Windows启动音乐? Win7电脑启动音乐设置方法

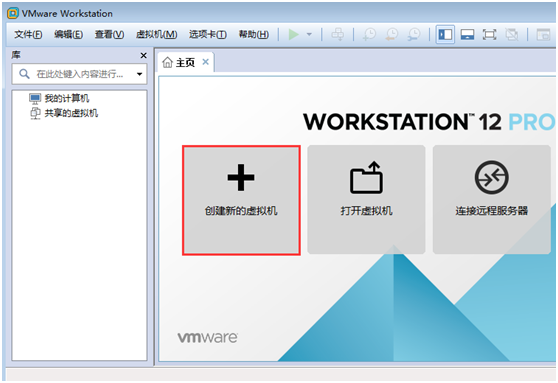

操作方法:如何设置Windows启动音乐? Win7电脑启动音乐设置方法 wmware虚拟机怎么安装win764位系统的方法分享分享

wmware虚拟机怎么安装win764位系统的方法分享分享 深层技术与雨林风之间的区别

深层技术与雨林风之间的区别

总局盯着小米电源查一段时间