文件系统转换 Bootloader之uBoot简介(转)(20)

电脑杂谈 发布时间:2018-02-07 22:32:44 来源:网络整理63 else if (pllreg == UPLL)

64 r = clk_power->UPLLCON;

65 else

66 hang();

67

68 m = ((r & 0xFF000) >> 12) + 8;

69 p = ((r & 0x003F0) >> 4) + 2;

70 s = r & 0x3;

71

72 /* 同时支持S3C2410和S3C2440, by */

73 if (gd->bd->bi_arch_number == MACH_TYPE_SMDK2410)

74 return((CONFIG_SYS_CLK_FREQ * m) / (p << s));

75 else

76 return((CONFIG_SYS_CLK_FREQ * m * 2) / (p << s)); /* S3C2440 */

77 }

78

由于分频系数的设置方法也不一样,get_HCLK、get_PCLK也需要修改。对于S3C2410,沿用原来的计算方法,else分支中是S3C2440的代码:

85 /* for s3c2440 */

86 #define S3C2440_CLKDIVN_PDIVN (1<<0)

87 #define S3C2440_CLKDIVN_HDIVN_MASK (3<<1)

88 #define S3C2440_CLKDIVN_HDIVN_1 (0<<1)

89 #define S3C2440_CLKDIVN_HDIVN_2 (1<<1)

90 #define S3C2440_CLKDIVN_HDIVN_4_8 (2<<1)

91 #define S3C2440_CLKDIVN_HDIVN_3_6 (3<<1)

92 #define S3C2440_CLKDIVN_UCLK (1<<3)

93

94 #define S3C2440_CAMDIVN_CAMCLK_MASK (0xf<<0)

95 #define S3C2440_CAMDIVN_CAMCLK_SEL (1<<4)

96 #define S3C2440_CAMDIVN_HCLK3_HALF (1<<8)

97 #define S3C2440_CAMDIVN_HCLK4_HALF (1<<9)

98 #define S3C2440_CAMDIVN_DVSEN (1<<12)

99

100 /* return HCLK frequency */

101 ulong get_HCLK(void)

102 {

103 S3C24X0_CLOCK_POWER * const clk_power = S3C24X0_GetBase_CLOCK_POWER();

104 unsigned long clkdiv;

105 unsigned long camdiv;

106 int hdiv = 1;

107

108 /* 同时支持S3C2410和S3C2440, by */

109 if (gd->bd->bi_arch_number == MACH_TYPE_SMDK2410)

110 return((clk_power->CLKDIVN & 0x2) ? get_FCLK()/2 : get_FCLK());

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/jisuanjixue/article-66092-20.html

-

-

傅羽檄

傅羽檄好帅

-

李衡

李衡你不能抱大腿

raspberry pi 当树莓派遇上NEC,物联网时代的显示器长什么样?

raspberry pi 当树莓派遇上NEC,物联网时代的显示器长什么样? 金山毒霸冲击波蠕虫特杀工具v1.1绿色版

金山毒霸冲击波蠕虫特杀工具v1.1绿色版 使用winrar自解压功能制作安装包

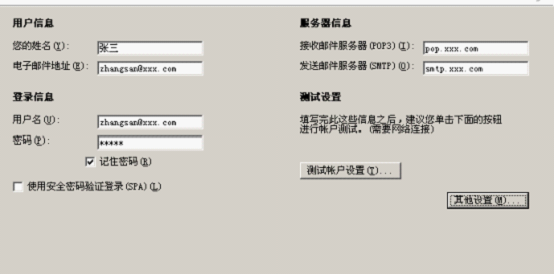

使用winrar自解压功能制作安装包 我的OUTLOOK2003,只能接受邮件不能发送.一群发就让输入网络密码.

我的OUTLOOK2003,只能接受邮件不能发送.一群发就让输入网络密码.

你出名了