十二进制计数器的设计方案摘要(五个模拟电路设计原理和过程的一部分)

电脑杂谈 发布时间:2020-04-19 15:20:12 来源:网络整理

本文为您带来了五种不同的12位计数器设计解决方案.

十二进制计数器的设计方案1: 设计74161的十进制计数器

1.74161是十六进制计数器. 设计十进制计数器时,一个芯片可以满足要求.

2. 创建一个新的BDF文件,然后像上一章一样保存项目.

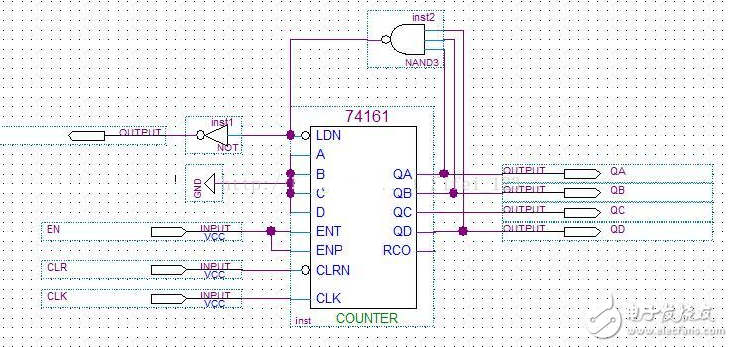

3. 将所需的组件和引脚拖到该区域中并完成连接,如图1所示.

图1十进制计数器的连接图

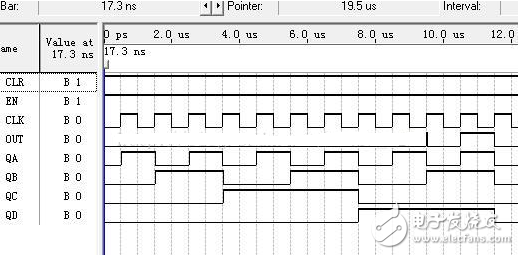

4. 创建VWF文件,仿真后结果如图2所示.

仿真波形图

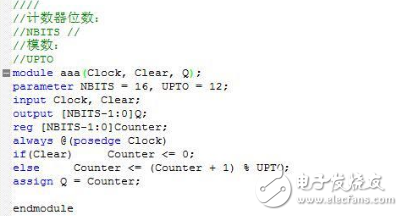

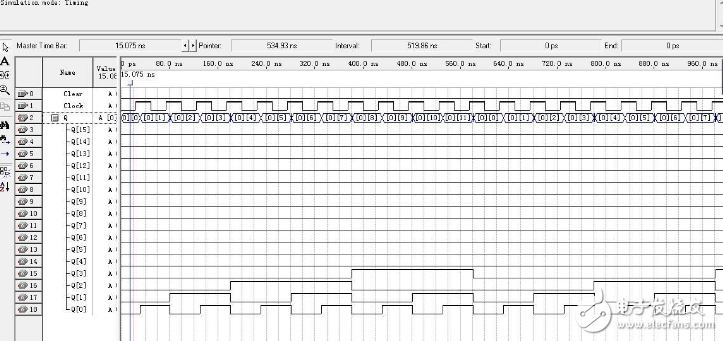

十二进制计数器的设计方案: 带有Verilog语言的十进制计数器的程序代码

模拟结果

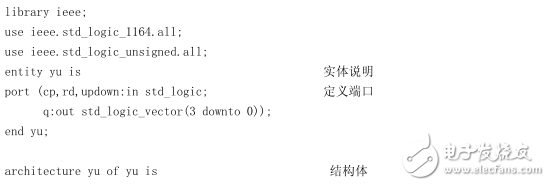

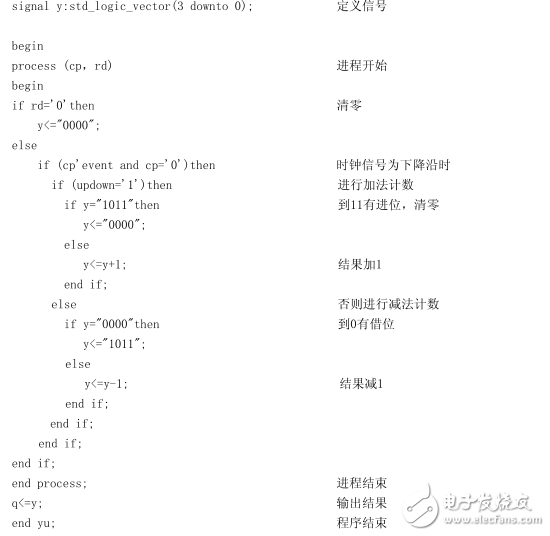

十二进制计数器的设计方案: 异步十进制加减计数器的1VHDl设计

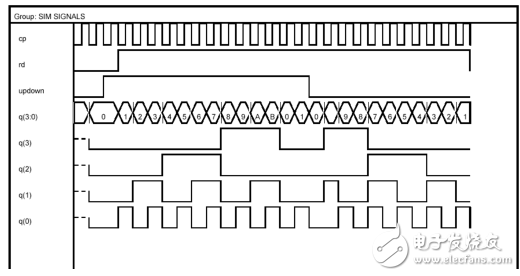

在设计中,CP为时钟输入端子,下降沿有效; Rd为清除控制端子,低电平有效. updown是计数模式控制端子,当updown =“ 1”,updown =“ 0”时,向上计数. 在计数操作之前,Rd给出一个清除信号,因此四个数据输入值都为``0''. y3,y2,y1,y0是四个数据输出端子,可以实现异步清除. 当Rd =“ 1”时,计数器向上计数,即从“ 0000”到“ 1011”依次计数;当up =“ 0”,up =“ 1”,Rd =“ 1”时74161计数器设计,计数器向下计数

程序设计

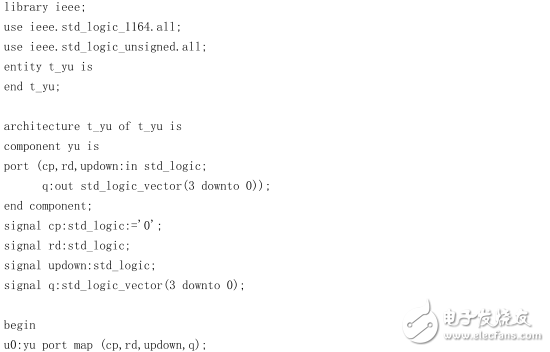

模拟测试程序

仿真图

12进制计数器的设计方案4: 异步十进制加减计数器2VHDl的设计思想

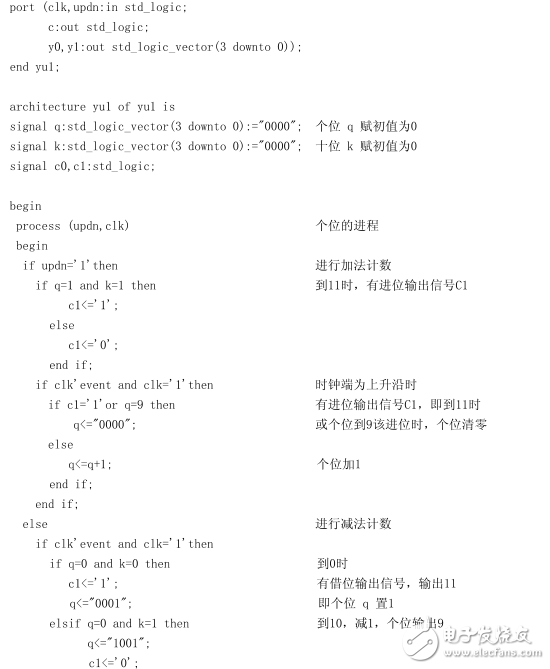

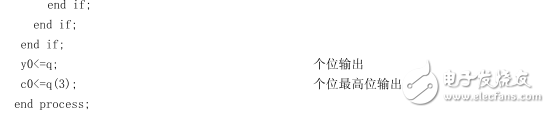

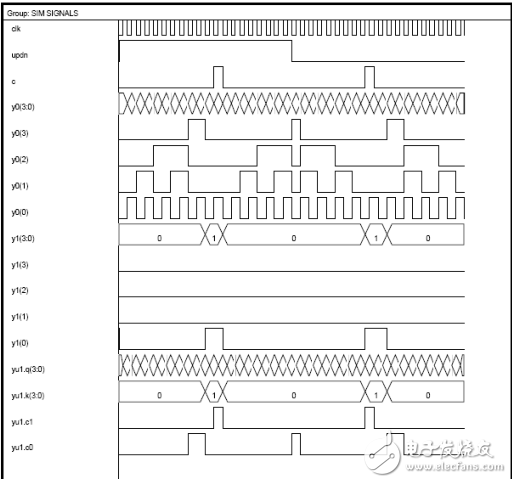

在设计中,clk是时钟输入端子,上升沿有效; updn是计数模式控制终端. 当updn =“ 1”时,它开始计数;当updn =“ 0”时,它递减计数; c是进位/借位输出. 结束; c0是单元的最高位输出. 在计数之前,第q位和第10位k均设置为零. 一位由时钟的上升沿加减-1触发,十位由一位的进位/借位触发,从而实现十位的变化,即异步可逆计数. 当updown =“ 1”时,计数器开始递增计数,单位数字从“ 0”到“ 9”依次计数,进位数字74161计数器设计,十位数字从“ 0”变为“ 1”,并在出现以下情况时清除计数达到11;当updown =“ 0”时,计数器递减计数.

程序设计

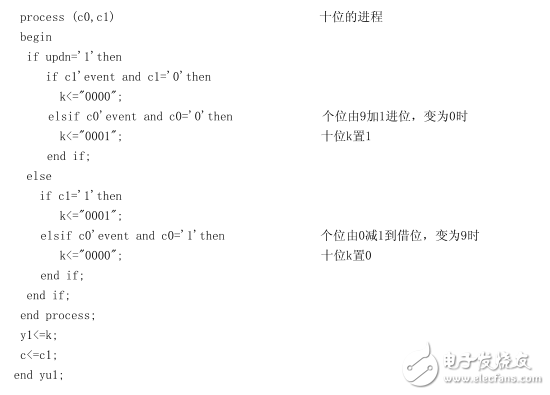

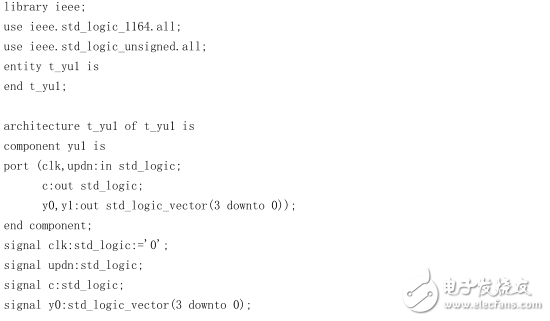

模拟验证程序

仿真图

12进制计数器的设计方案5: 使用两个74LS160设计十进制计数器

两个芯片之间的级联;将上层芯片的进位端连接到下一层的高端. 这是一个由两个74LS160连接而成的12位计数器,低位连接成一个十进制计数器,其clk Terminated是低位进位脉冲. 高位数字连接到十进制计数器. 当输出端子为1010时,在下一个时钟的上升沿将数据设置为0000. 它形成一个十六进制计数器,甚至级联也变成一个十六进制计数器,可以用作秒和分钟.

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/jisuanjixue/article-181318-1.html

-

-

元武宗海山

元武宗海山中国捍卫自身主权和海洋权益的立场坚定不移

windows7 64位旗舰版

windows7 64位旗舰版 详细解释无代码开发与低代码开发(低代码≠无代码)之间的本质区别

详细解释无代码开发与低代码开发(低代码≠无代码)之间的本质区别 大神教您如何使系统最简单,最实用.

大神教您如何使系统最简单,最实用.

我终于醒了