verilogreset_十进制计数器 verilog_74ls161十进制计数器

电脑杂谈 发布时间:2017-02-19 18:27:19 来源:网络整理

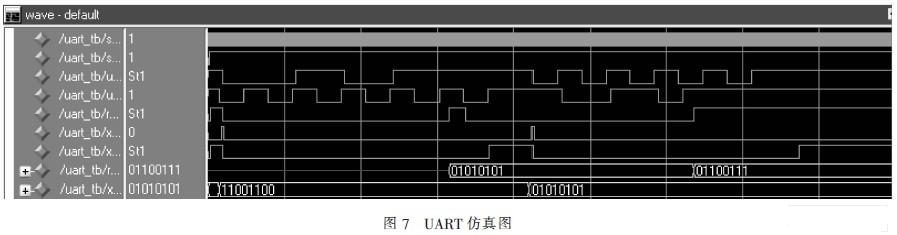

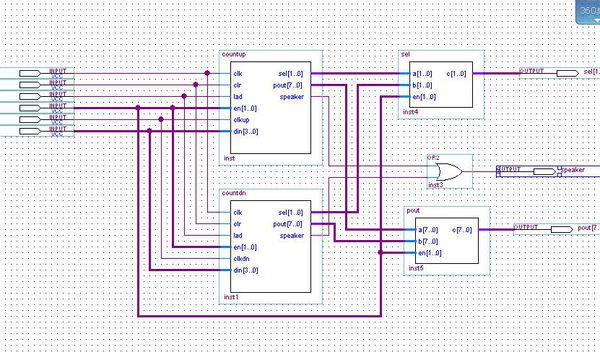

拨动复位信号时,无视WE信号,直接复位。仿真结果:当输入reset信号时波形变化如下当达到一个扫描信号的周期时的波形如下当达到一个以上计数信号的周期时的波形实验分析:实验总体结构和模块间关系如图所示:(其中还需要补上使能信号)实验原理:由于要求实现数码管和LED灯的显示,先考虑LED灯,可以直接由8位输出信号控制,而数码管需要同时显示两个不同的数字,需要时分复用,即快速的交替显示十位和个位,利用人眼的视觉暂留来达到同时显示。这样就需要两种不同的频率信号。一种是每0.5s一次,作为计数信号,用脉冲生成,另一种是1ms一次的扫描信号,用降频器生成,将计数信号输入计数器来计数,并将计数的值和扫描信号同时输入扫描显示模块。十进制计数器 verilog在扫描显示模块里用一个变量值在0和1间交替来指导选择信号选择数码管的不位数。交替的条件是收到扫描信号。7段数码管和LED灯都与计数值的变量相连即可实现。实现细节首先写一个脉冲(div.v),每0.5s输出一次计数脉冲cnt写一个计数器(cnt.v)设置一个8位计数变量,分成两个4位变量dnum(十位)和num (个位)。如果接受到rst信号,则将计数变量置成x90.否则每次接受到计数信号,将计数变量的值增1,(同时考虑进位和回到x00的情况)写一个扫描信号(scan.v),每1ms生成一次扫描信号写一个显示器(display.v),设置对数码管位数的4位选择信号sel和led灯的控制变量dnum(高4位)和num(低四位)。

设置seg作为7段数码管的控制变量。设置一个中间变量a(初值0),如果接受到scan信号,将a 0变1或1变0.如果a为0,sel为x1101,显示数码管十位,如果a为1,sel为x1110,显示数码管个位。以上各个模块均由时钟信号控制。十进制计数器 verilog写一个top模块综合以上模块。附录(源代码):Div.v模块:module div( input clk, input rst, output reg cnt ); reg [25:0] cnt_div;always@(posedge clk or posedge rst)beginif(rst)cnt_div<=26'b0;else if(cnt_div==26'd49_999_999)cnt_div<=26'b0;elsecnt_div<=cnt_div+26'b1;endalways@(posedge clk or posedge rst)beginif(rst)cnt<=1'b0;else if(cnt_div==26'd49_999_999)cnt<=1'b1;elsecnt<=1'b0;endendmodulecnt.v模块:module cnt( input clk, input WE, input rst, input cnt, output reg [3:0] dnum, output reg [3:0] num );always@(posedge clk)beginif(rst)begindnum<=4'h9;num<=4'h0;endelse if(WE && cnt)beginif(num==4'h9)beginnum<=4'h0;if(dnum==4'h9)dnum<=4'h0;elsednum<=dnum+4'h1;endelsenum<=num+4'h1;endendendmodulescan.v模块:module scan( input clk, output reg scan_sgn );reg [16:0] scan_cnt;initial scan_sgn=0;initial scan_cnt=0;always@(posedge clk)beginif(scan_cnt==17'd99_999)scan_cnt<=17'd0;elsescan_cnt<=scan_cnt+17'b1;endalways@(posedge clk)beginif(scan_cnt==17'd99_999)scan_sgn<=1'b1;elsescan_sgn<=1'b0;endendmoduledisplay.v模块:module display( input clk, input scan_sgn, input [3:0] num, input [3:0] dnum, output reg [7:0] seg, output reg [3:0] sel ); reg a=0;//initial a =0;always@(posedge scan_sgn)beginif(a==1'b0)a=1'b1;elsea=1'b0;endalways@(posedge clk)beginif(a==1'b0)beginsel=4'b1101;case(dnum)4'h0:seg=8'b0000_0011;4'h1: seg=8'b1001_1111; 4'h2: seg=8'b0010_0101;4'h3: seg=8'b0000_1101;4'h4: seg=8'b1001_1001;4'h5: seg=8'b0100_1001;4'h6: seg=8'b0100_0001;4'h7:seg=8'b0001_1111;4'h8: seg=8'b0000_0001;default: seg=8'b0000_1001;endcaseendelsebeginsel=4'b1110;case(num)4'h0:seg=8'b0000_0011;4'h1: seg=8'b1001_1111;4'h2: seg=8'b0010_0101;4'h3: seg=8'b0000_1101;4'h4: seg=8'b1001_1001;4'h5: seg=8'b0100_1001;4'h6: seg=8'b0100_0001;4'h7:seg=8'b0001_1111;4'h8: seg=8'b0000_0001;default: seg=8'b0000_1001;endcaseendendendmoduletop模块:module top( input clk, input rst, input WE, output [7:0] seg, output [3:0] sel, output [3:0] dnum, output [3:0] num ); wire[3:0] dnum; wire [3:0] num; wire cnt; wire scan_sgn;divu_div(.clk(clk),.rst(rst),.cnt(cnt));cntu_cnt(.clk(clk),.rst(rst),.WE(WE),.cnt(cnt),.dnum(dnum),.num(num));scanu_scan(.clk(clk),.scan_sgn(scan_sgn));displayu_display(.clk(clk),.sel(sel),.seg(seg),.dnum(dnum),.num(num),.scan_sgn(scan_sgn));endmoduleucf文件:Net "seg<7>" LOC = T17;Net "seg<6>" LOC = T18;Net "seg<5>" LOC = U17 ;Net "seg<4>" LOC = U18 ;Net "seg<3>" LOC = M14 ;Net "seg<2>" LOC = N14;Net "seg<1>" LOC = L14;Net "seg<0>" LOC = M13;Net "sel<0>" LOC = N16;Net "sel<1>" LOC = N15;Net "sel<2>" LOC = P18;Net "sel<3>" LOC = P17;NET "WE" LOC=T9;NET "rst" LOC=T10;NET "clk" LOC=V10;Net "num<0>" LOC = U16;Net "num<1>" LOC = V16;Net "num<2>" LOC = U15;Net "num<3>" LOC = V15;Net "dnum<0>" LOC = M11;Net "dnum<1>" LOC = N11;Net "dnum<2>" LOC = R11;Net "dnum<3>" LOC = T11;仿真代码:module test5;// Inputsreg clk;reg rst;reg WE;// Outputswire [7:0] seg;wire [3:0] sel;wire [3:0] dnum;wire [3:0] num;// Instantiate the Unit Under Test (UUT)top uut (.clk(clk), .rst(rst), .WE(WE), .seg(seg), .sel(sel), .dnum(dnum), .num(num));initial beginclk = 0;#100;WE = 1;rst = 1;#10;rst=0; end always #1 clk=~clk; endmodule対本实验的总结和体会;要仿真正确是烧写的前提,先仿真正确再烧写要给每个模块定义的变量一个initial语句,否则在仿真中会出现变量的值未定义的xxxx的情形实验时仿真一直出现的一个问题是没有写initial语句,导致各个模块的中间变量没有初值,而很多输出变量的变化条件都是根据中间变量的上升沿河下降沿来触发的,这样中间变量即使有值也不会产生电平变化,导致仿真时输出没有变化(虽然烧写到板子上没有问题)理解了仿真的原理是将整个project当成一个黑匣子,在isim的仿真程序中需要写语句模拟整个project的输入信号比如clk(用forever语句),rst和WE变量(在程序中赋值)为了能使仿真时各个变量异步的变化,比如在时钟变化的过程中使rst等其他输入变量变化,但是initial语句又是顺序执行的,此时可以写多个initial语句来并行得是变量变化。

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/dianqi/article-33365-1.html

-

-

穆君宇

穆君宇任何东西都要一分为二看问题

精密钢管高性价比的选择「多图」

精密钢管高性价比的选择「多图」 继电器电磁阀 兰溪电热鼓风干燥箱高效

继电器电磁阀 兰溪电热鼓风干燥箱高效 夏普led电视怎么样 8K OLED?LG DiSplay将量产

夏普led电视怎么样 8K OLED?LG DiSplay将量产 冰箱食物的恰当存放方式 每个人都必须清楚

冰箱食物的恰当存放方式 每个人都必须清楚

干嘛不和叙利亚比啊