LED大屏幕显示系统由上位机之间的FPGA控制模块

电脑杂谈 发布时间:2021-05-19 22:03:28 来源:网络整理简介

只要您在当前市场中四处走动,就会发现大多数中小型LED显示系统都使用传统的单片机作为主要控制芯片。但是,内部系统资源少,运行速度较慢的单片机难以满足LED大屏幕显示的需求,因为该系统需要大量的数据传输和较快的扫描速度。一方面,以FPGA为控制器,FPGA通过软件编程实现硬件功能,可以有效提高运算速度;另一方面,它具有丰富的引脚资源和强大的可扩展性。因此,一个FPGA和一个简单的电路就可以实现大屏幕LED显示屏的控制,具有集成度高,稳定性好,设计灵活,效率高的优点。

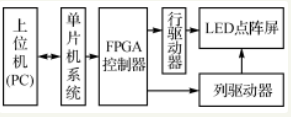

1系统的总体结构

LED大屏幕显示系统由主机(PC),单片机系统,FPGA控制器和LED显示器的行和列驱动电路组成,如图1所示。上位机负责收集和传输汉字和汉字等数据。单片机系统和主计算机以异步串行通信模式工作。格式转换后要显示的图形点阵数据是通过串行端口从主机获得的,并存储在EEPROM存储器中。然后,通过FPGA控制器,将存储器的显示数据恢复到LED显示屏。扫描控制电路采用可编程逻辑芯片Cyclone EP1C6,通过VHDL语言编程实现,采用1/16扫描方式,刷新频率在60Hz以上。本文重点介绍256×1024单形显示器的FPGA控制模块。

图1系统总体结构框图

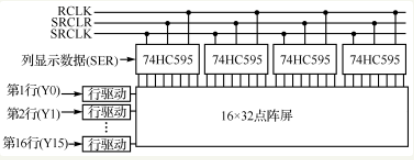

2 LED显示屏的基本工作原理

对于大屏幕LED显示器,列显示数据通常采用串行传输方法,而行则采用1/16扫描方法。图2显示了16×32点矩阵屏幕单元模块的基本结构。列驱动电路由4个74HC595级联组成。在移位脉冲SRCLK的作用下,串行数据从74HC595的数据端口SER逐位输入。当发送一行中的所有32列数据时,输出锁存信号RCLK并选择行信号Y0,然后可以根据需要显示该行每一列的第一个数据。以相同的方式显示剩余的行。扫描完16行数据一次(即完成一个周期)后,下一个扫描周期从第一行开始。只要扫描周期小于20 ms,显示就不会闪烁。

图2 16×32点矩阵屏幕的基本结构

通过级联16×32 16×32点矩阵屏幕形成256×1024大屏幕显示器。为了缩短从控制系统到屏幕的信号传输时间,将显示数据划分为16个区域,每个区域由16×1024点矩阵组成,每行数据为1024/8 = 128字节,并且显示屏的像素信号由LED显示屏的右侧组成并向左侧移动,并将16个分区的数据存储在同一存储器中。一个屏幕的显示数据为32 KB。为了准确地读取16个分区的数据,存储器的读取地址由16位组成。由于数据只有32 KB,因此最高的可以设置为0。其余的15位地址从高到低分别是:行地址(4位),列地址(7位)和分区地址(4位)。 4位分区地址的解码信号(Y0〜Y1 5))用作锁存器的锁存脉冲。在16个读取地址生成周期内,第1至16个分区的第一个字节数据依次锁存到对应的在移位锁存信号的上升沿,同时将16字节数据锁存到16个8位并行/串行移位寄存器组中,一方面,在接下来的16个读地址时钟周期中,并行- to-serial移位寄存器将8位数据移位为串行输出,移位时钟为频率除以读取地址生成时钟的两倍;另一方面,读取16个分区的第二个字节数据并将其锁定到相应的,根据该规则,依次读取所有分区的所有第一行数据后,将在数据有效脉冲信号的上升沿输出所有串行移位数据,并驱动LED显示器。在此期间,第二行的数据将保持显示在第一行上;第二行移入后,第二行将被驱动显示,第三行将移入第三行……用这种逐行扫描每个分区的方式完成整个LED大屏幕扫描并显示。

3基于FPGA的显示控制器的设计

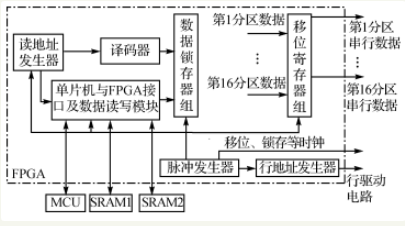

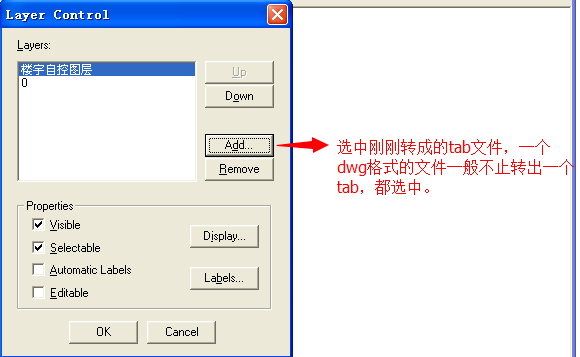

3. 1 FPGA控制模块的总体方案

如图3所示,FPGA控制模块主要由MCU和FPGA接口以及数据读写模块,读取地址,,行地址,数据锁存器组,移位寄存器组,脉冲组成。发电机和其他模块。

图3 FPGA控制模块总体结构框图

读取地址主要生成读取地址信号,将其发送到MCU接口和数据读写模块,读取外部SRAM1或SRAM2中已处理的LED显示数据,并将该数据发送到分区的数据中。方式闩锁组被闩锁。锁存器输出16个分区数据,显示屏所需的串行数据通过移位寄存器组通过并行到串行转换获得,并发送到LED显示列驱动电路。脉冲发生器为每个模块提供相应的同步时钟,行地址发生器产生相应的行信号并将其发送到显示屏的行驱动电路。

3. 2 MCU和FPGA接口以及数据读写模块

单芯片READ_END为低电平时,它将进入ST1状态。

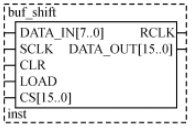

在ST1状态下,如果未写入任何新数据,则E将保持高电平。 FPGA读取SRAM1的数据,这是一个静态显示;仅当单片机的读入控制信号E为低电平且READ_END为低电平时,才进入ST2状态。在ST2状态下,如图6所示。其中,DATA_IN [70]是每个分区的8位并行数据输入,SCLK是移位时钟,CLR是清除信号,LOAD是数据锁存信号,CS [150]是16个分区的输入信号(连接到解码输出),DATA_OUT [150]是16通道串行数据输出。

图6并行-串行转换组件符号图

3. 6脉冲发生器

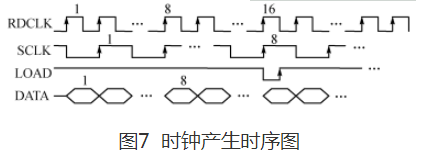

系统使用1/16扫描方法将数据划分为16个分区,并同时传输16个分区的数据。假设刷新频率为60 Hz(即周期为1 6. 67 ms),则每行的显示时间约为1 6. 67 ms / 16 = 1. 04 ms。每行有1024位,移位脉冲周期为1. 04/1024 =102μs,即移位频率为0. 983 MHz或更高才能满足要求。由于移位脉冲被数据读取模块时钟的2分频,所以系统时钟至少在97 MHz以上1.,并且该系统使用50 MHz时钟源。时序图如图7所示。

其中,RDCLK是FPGA的读取数据时钟。 SCLK是串行输出的移位时钟,由RDCLK的2分频; LOAD是数据锁存器信号,每次在数据DATA之后都会在16个分区中读取某个字节,然后生成锁存器信号,并将数据锁存在数据锁存器组中。时钟被RDCLK的16分频。

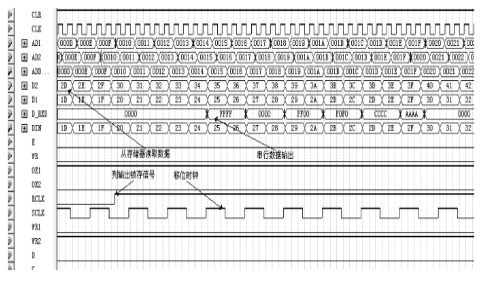

4 FPGA控制模块的仿真测试

在QuartusII 5. 1中创建一个项目,并创建一个原理图文件,以将微控制器与FPGA和数据读/写模块,读地址,,行地址,数据锁存器接口,并生成模块组件符号通过将移位寄存器和脉冲发生器等单元模块连接起来,形成整体控制模块的逻辑图并模拟其功能。仿真结果如图8所示。从存储器读取16个字节的数据,并通过并行到串行转换输出16个通道的串行数据。从波形图分析来看,该功能是正确的,每个输出端口的信号均满足时序要求。

图8 FPGA控制模块仿真图

5结论

FPGA是一种可编程芯片,可以根据不同的用户要求进行编程,从而缩短了系统开发周期并节省了硬件开发成本。本文以FPGA为主要芯片,对大屏幕LED单形显示控制系统进行了较为完整的设计。随着LED显示技术的发展,FPGA与ARM或DSP芯片的结合必将在两色显示和彩色显示领域得到广泛应用。

关键字:MCUFPGALED编辑:什么鱼参考地址:

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/tongxinshuyu/article-376657-1.html

当年我们玩过的塞班游戏《三国猛将传》系列,诺基亚最佳动作游戏

当年我们玩过的塞班游戏《三国猛将传》系列,诺基亚最佳动作游戏 富寿康(上海)家庭服务

富寿康(上海)家庭服务 飞利浦超窄边框显示屏呈现出无缝外观(组图)

飞利浦超窄边框显示屏呈现出无缝外观(组图) mapxtreme_mapxtreme 2008破解_arcgis engine

mapxtreme_mapxtreme 2008破解_arcgis engine

象是给美国出一出气