testbench_testbench如何加载_vhdl testbench reset(5)

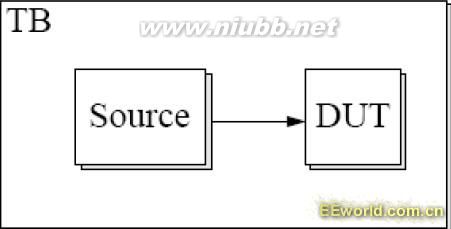

电脑杂谈 发布时间:2017-03-09 10:04:50 来源:网络整理二、DUT的输入由单独的一个文件产生,在testbench中实例化两上entity,可以复杂输入,简单输出的模块。模型如图2所示

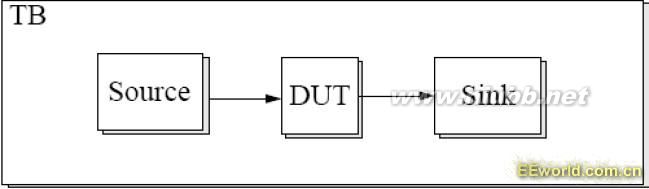

三、DUT的输入与测试输出各由单独文件产生,在testbench由三个实例化模块产生,用于具有复杂输入以及输出的模块,模型如图3所示。

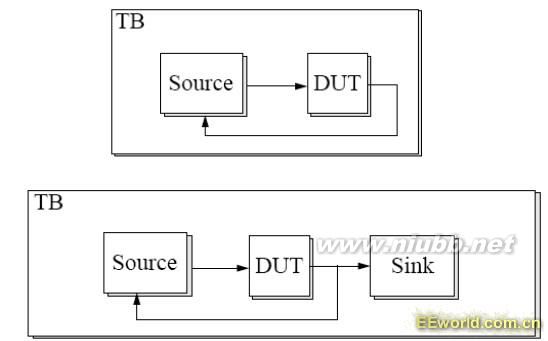

四、可以根据仿真输出来修改输入激励的,可以自动通过输出来修改输入,使验证更加准确。如图4所示的模型

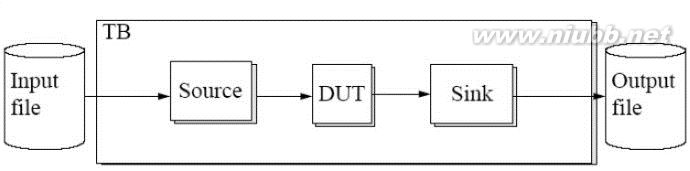

五、有文件做为testbench的输入,输出的模型。testbench仿真中需要顺序的输入大量数据,以及接收相应的数据,可以通过从文件中读入数据,然后将产生的数据存入文件,使复杂系统验证更加方便。模型如图5所示。

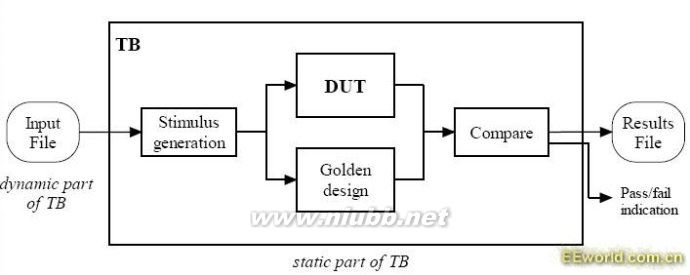

六、可以将激励同时输入自己设计的模块和已经验证了相同模块,比较二者输出。模型如图6所示。

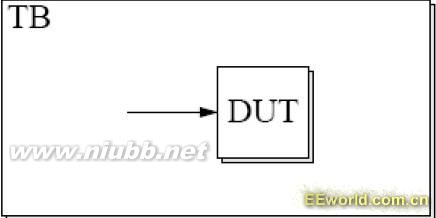

图1

图2

图3

图4

图5

图6

Testbench写法简要介绍

描述测试信号的变化和测试过程的模块叫做测试平台(Testbench),它可以对电路模块进行动态的测试。通过观测被测试模块的输出信号是否符合要求,可以调试和验证逻辑系统的设计和结构是否正确,便于发现问题并修改。

Testbench用于测试模块的如图所示:

由可知,Testbench要对被测模块进行测试,需要产生被测模块所需的激励信号(比如时钟信号,复位信号等),这个就像我们用Quartus波形仿真时拖波形一样,只是Testbench里需要我们用代码来实现波形的变化。

产生的激励信号需要与被测模块对口(比如产生的时钟信号要送入时钟输入口,产生的复位信号要送入复位输入口等),如何实现对口,这就需要对被测试模块的例化来实现。例化的写法如下:

被测模块名例化进Testbench后的模块名

(

.被测模块输入口Testbench产生的激励信号,

.被测模块输出口Testbench里用来显示输出的信号

);

上面的对应的例化写法为:

被测模块名例化进Testbench后的模块名

(

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/tongxinshuyu/article-36621-5.html

-

-

汉武帝刘彻

汉武帝刘彻美国有点气急败坏

-

吕素涛

吕素涛再个地方政府保护当地企业也很正常

中国也俱战