testbench_testbench如何加载_vhdl testbench reset

电脑杂谈 发布时间:2017-03-09 10:04:50 来源:网络整理Testbench学习笔记(一)

书写testbench是数字电路设计中不可或缺的一项设计方法,主要是提供的是激励。尽管现在各种开发工具都通过绘制波形图的方法生成测试激励,测试书写的代码,但是其不可移植性,不可通用性,还有有些功能无法是实现,如监视变量的值的变化,显示数据的状态等。

一个完整的testbench包含下列几个部分:

(1)module的定义,一般无输入输出端口。

(2)信号的定义,定义哪些是你要输入,输入的定义为reg类型,输出的定义为wire型

(3)实例化待测试的模块

(4)提供测试激励

1.如何书写测试激励;

(1)时钟信号的产生

initial

begin

clk=0;

forever

#clk_period/2clk=~clk;

end

或者是

always

begin

#clk_period/2clk=0;

#clk_period/2clk=1;

end

产生时钟的原理,是利用always或者是initial+forever产生不断重复的信号,构成时钟信号。

(2)复位信号的产生

复位信号就是在复位电平下延时一段时间,然后再将复位电平信号取反即可。如:

initial

begin

rst=0;

#100;

rst=1;

end

在实际应用将其封装为task,使用时掉调用即可。

调用如下:

initial

begin

sys_time(100);//复位100个时间单位

.....

end

任务的定义如下:

tasksys_rst;

input[10:0]rst_time;//调用task的时候,将参数赋值给rst_time

begin

rst=0;

#rst_time;

rst_time=1;

end

endtask

(3)产生一种复杂的信号。如下面的实例产生一个vs和hs信号

//-------------------------------------------------------------------------------------

parametern=10;

//-------------------------------------------------------------------------------------

initial

begin

cmos_hs=1'b0;//time0时刻

cmos_vs=1'b0;

repeat(n)//重复n次

begin

#200cmos_vs=1'b1;//time200

repeat(10*n)

begin

#100cmos_hs=1'b1;//time300

#100cmos_hs=1'b0;//time700

end

#100cmos_vs=1'b0;

end

end

该程序段可以生成10个vs信号,每个vs信号下有100个hs信号。由于initial信号只能执行一次,所以为了得到有限的重复信号,可以采用repeat关键词得到。

这样基本上就可以完成一些简单的测试testbench了。

2.如何将我们的测试尽可能的简单明了化

用Modelsim对VerilogHDL进行仿真的人都会知道,看一大堆波形会很麻烦,如果代码变量很多,很复杂,出了问题都不知道问你在哪里,或者看了半天,发现图形是个错的。运用合适的方法将自己需要的变量以文本方式显示,监视变量的变化不很好嘛?

下面介绍几种常用的系统函数

(1)$time

作用:返回所在模块的仿真时间,可以查看信号的出现的时间,用来把握信号的时序。

如:$display(''thetimeis%t'',$time);//显示当时的时间

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/tongxinshuyu/article-36621-1.html

-

-

桑万鹏

桑万鹏也不是

-

西村朋纮

西村朋纮有多少项多少项成果

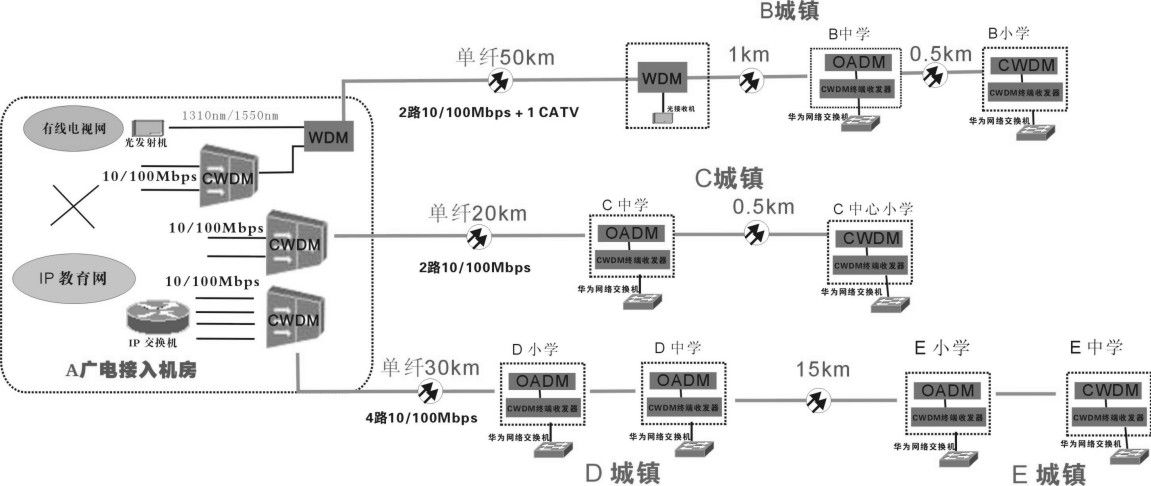

传输 oadm_oracle oadm_什么是oadm

传输 oadm_oracle oadm_什么是oadm Aoc显示器19英寸二手价格

Aoc显示器19英寸二手价格 arp static和am user-bind 区别

arp static和am user-bind 区别 移动设备功能_移动手机钱包功能_移动开通gprs功能

移动设备功能_移动手机钱包功能_移动开通gprs功能

&