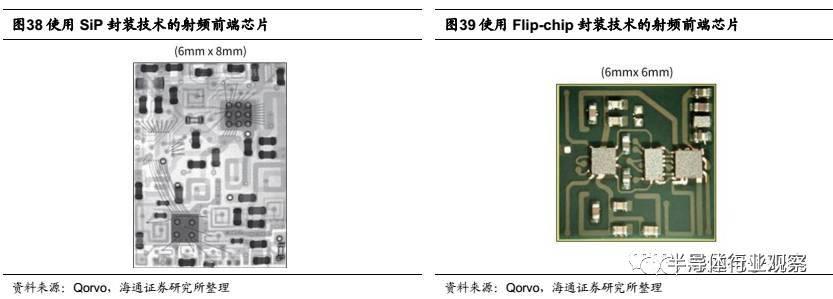

射频包装系统SIP(包装中的系统)

电脑杂谈 发布时间:2020-05-16 16:18:03 来源:网络整理

2} s“ v(_8 J $ e $ [8 |; X; l” S * y- J8 o5 ^ 2 P

$ s4 u: 〜6 X1 e + t#u

j)t#a2? 7我*?. H3 P,B / i2 G! W“ v6 I)n / J!L

/ R0 N- g;] 3 U(s / z4 wSiP设计比板级方法更短. 互连线的缩短一方面可以提高电路性能(减少互连损耗和延迟以及寄生效应) ;另一方面,它可能会增加互连-互连,元素-元素与任何“相邻”元素之间的耦合/串扰. 对于板级应用,这些交互不是问题,因为板级组件包装被安排得相对较远.

1} 9 N! S7 O7 b0 F2 L)k5 F%N

3 e! W2 _: b,j. J /`8 s3 M4 jr! S4 E,e4 b和W0 a $ g

在通过芯片堆栈结构垂直安装多个IC的3D封装中,RF SiP应用还需要考虑不同芯片之间的串扰. 具有电磁屏蔽(EMI)功能的功率放大器通常单独包装以确保良好的隔离. 通常情况下,它们未集成在SiP中,因此本文将不进行讨论. 接下来,我们将重点介绍SiP产品中的常见问题. Q * N和n4 y6 v5 a7 C + m1 ob

7 A'〜. _: X0〜'h $ H + |

&i2 C6 @! T4 M“ T; ZR)u)t3 G2SMD电容焊盘和互连线效应

'z“〜2 A / N#u; z: 〜4 J5 R#X

(E + H. b!u8 k9?3 V; |

2 e $ _2 C; U)L%B! D6 o#z5 C8 j4 | 'Q $ S2 P! r2 z%o

尽管01005 SMD电容器已经上市了一段时间,但由于高昂的组件价格和组装成本,它们尚未成为RF SiP的流行选择. 我们研究了具有焊盘分布和互连的0201 SMD电容器. 4 ^ 3 j $ n,W8 z0 F!是

+ s0 S + f2 a +K. L $ ^ o#D'x!?

. v4 k $ m2 S1 F! | 4克m4 D

我们可以从不同的SMD供应商那里获得0201电容器的S参数. RF SiP设计人员可以从供应商的产品目录中选择所需的SMD电容器(例如10pF). 此外,供应商还提供了SMD组件的低频(接近DC)电容值. 由于寄生效应,在不同频率下获得的等效电容与在接近直流频率下获得的电容不同. 因此,RF SiP设计人员必须测试电容器是否可以满足其应用频段(例如2.4GHz). 最好的检测方法是使用供应商提供的S参数值进行系统级仿真过程以识别它. ; mT1 l! m + r

'_ 4? + V7 {7 _&b + J3 W

8 s“ @. q. 〜(U(?: F电路图和与其对应的实际电路). 主要区别在于,实际电路/布线显示了SMD焊盘(附加部件)的互连和支撑. 在RF频率(例如2.5GHz)下,这些额外的部分可能会对电容器产生“偏移”效应,这一点不能忽略. 图2显示了这种现象的示例. 0201组件焊接磁盘位于顶层( M1),比固有的0201稍大,从而确保更高的组装成品率. 第二层(M2)通常是固体接地层,并且M1和M2之间的介电层是其厚度. 当介电层厚度从150.0μm变为100.0μm和60.0μm时,焊盘电容将从77.8fF变为90.6fF和113.0fF. 如果这些焊盘用于1.0pF SMD电容,则包括焊盘电容将增加11 .3%(使用60.0μm的电介质). 增加的电容足以微调RF电路的功能.

1个问题: B8 | 2 h5 _6 T2 E)hr

7 D,X7 X5 \. | 6 J $ \! q

. G. S“ l1 n'_'G4 O,〜

“〜. t(O2 A0?%N- w + W8 i

; f&J7 l $ k9 e#I'A2 I'X

&x. {'f3 a4 m + z. X&_1 J0 v. _1 lx! w

互连线的长度不会对BBIC封装或大多数低频应用产生重大影响,但会对RF应用产生更大影响,因此在RF SiP设计中需要考虑这一重点. 在电磁(EM)模拟过程中,应注意互连线的电效应(长度和宽度). 但是对于SiP产品,由于使用了大量的焊盘和互连,因此在整个封装仿真中,所有焊盘都用作总端口. 这种多端口仿真通常需要大量内存,并且需要很长时间才能完成.

6 f#i * b2 d0 I0 Z / n#k5 c'C: t0 \&} 7〜

图3是单个SMD焊盘的互连长度对电容RF频段的影响的简单示例. 连接到M2层以形成接地电容器,宽100.0μm的互连线连接到另一个电极.

,o- _,x. @ -g2 B $ R! C \. O9 _

-} 5 Z&_6 v2 _; B&yW在2.5GHz频带中,1.0mm长的互连线可以将SMD电容器的等效电容增加到4.9pF(增加了63%). 当然,互连线越短,等效电容就越接近本征电容(3.0pF)的值. 但是,通常不可避免的是使用长互连来连接SMD组件. 在这种情况下,考虑互连线对电容的影响(有时称为这种微调电容的方法)非常重要,否则SiP将无法正常工作. * [)Z: 〜5 O)o,C

“ L4 f6 p6 D / t; D%IE

&a)N $ Y'| 1 s {3 Y

,p + [7 \; L; T4 G: X-? 7我

,v7 x“ j $ zF. t'](H8 X

. j6 z)? 1 j5 H / S5 G- e

+ s(e6?/ | t0 K除互连的长度外,互连的宽度也会影响RF电容. 在基板制造过程中,线宽通常会发生变化(例如,即,与设计宽度相比,实际线宽在±10.0μm到±15.0μm之间,如图4所示,如果设计的互连线长1.0mm,宽60.0μm,则实际上达到40.0μm宽,等效在2.5GHz时,电容变化将达到5.3%(以3.0pF接地SMD电容器为例),如果将此SMD电容器用于滤波器,则对于RF应用,电容值的变化为5.3%,这导致频移为大约2.7%. 我们必须仔细研究RF应用中包含SMD电容器的RF SiP模块的基板制造公差. ,L0 Y!J0] 1 m&J: @&z

&M $ Q6 W#O,m8 K + w: N2 k

$ d / _){: h%L. L / W8 U7 U

-C1]#^ 3 Y3 Pm! @ 5 {

1`9 w2 V5 R7 x3 G $} 1 N9 e5 I

/ o#i6 o9 j. F. G“ Q!l. } 6 y: D / Y. T $ Q- x3 | 5 o; R

3具有互连线公差的阻抗特性和引线键合电感. S·J·^. E&a'H8 K

+ w“ o(}&U!〜$ ^ 4 J: S!J8 J8 [0 C2 s

在RF SiP中,通常在RF通道中使用差分方法. 大多数和LNA使用差分输入/输出信号模式以获得更好的噪声抑制特性. 由于需要额外的空间来确保某些互连线的宽度和间距并保持互连线与接地屏蔽/平面之间的距离,因此在包装产品中这些平行互连线的布置极具挑战性. 线宽/间距公差对差分对的阻抗特性有很大的影响. 如果不能很好地控制此容差,结果仍将显示差分信号特性,但是回波损耗和插入损耗将大大增加,因此不再具有良好的匹配特性.

)K#q0 y'fD- o4 x6 L8 @ $ q- I1 F,V $ X + T $ O

3 N,p. A.})t2 s6 D / U,b

%v0 j. }-n: z

图5显示了键合线电感如何影响差分对连接的插入损耗. 在该示例中,100.0Ω差分对的长度为2.0mm. 假设差分对的一端通过引线键合连接到RFIC,并且与引线长度直接相关的电感(L)设置为可变值. 如回波损耗图所示,引线键合电感会导致差分对偏离匹配条件100.0Ω,从而导致插入损耗增加. 6 h0 i: Q(H. _ @ 4 D“ d7 I / D1 ['X)u

5 {! a3 H4 @)V3 b

0 L1 q $ G * Z; |,u在5.0GHz,0.5nH,1.0nH和1.5nH引线电感的插入损耗分别为0.2dB,0.5dB和1.2dB. 即使在极高的频率下,堆叠本身的差分对仍然具有良好的阻抗匹配特性. 这也显示在图5中(在L = 0nH的情况下). 回波损耗在高达10.0 GHz的频率上仍然保持良好状态,这表明100.0Ω差分对本身具有良好的匹配性和低损耗特性. 显然,在高频RFIC应用中,引线键合损耗成为一个重大问题. 为了克服此阻抗失配问题,RFIC和封装设计人员应共同努力,找到与特定芯片阻抗匹配的封装形式. 这可能会导致非标准差分对设计,但该设计将紧密匹配引线键合芯片.

| &W $ f(T%D'^ 6 V0 l5 I. P“ I6 n” j. b- K

-t9 o + y)J: h; \ 1 a + o0 F

5 X'{: S / _#t#t4 Ay“ J * V- M9]” O

/ I / \; q * U5 b: O * D + N

/ s3 q,j + V4 h4 Z + m

&x'Y + K,T $ {0〜对于高频RF封装,倒装芯片解决方案可以实现最小的互连电感sip射频封装技术,从而获得所需的出色性能(低损耗,良好匹配). 但是,即使使用RDL(再分布层),引线键合结构中使用的RFIC设计也不能直接用于倒装芯片产品中,这主要是由于倒装芯片结构中RFIC电感的环境条件所致. 它与引线键合结构完全不同. 9 O: F4〜! V7 b + C2 E5 S,M%u

'H4 J4 j * b! O0 u#{/ U.〜

(W!q5 v“ | * V9 k / U” J

4BBIC和RFIC主时钟线之间的串扰

/ H,{/ I3 h)i + W

9 {&| (Jw +`/ e $ R $ J3 z: J- C2 _'e6 P

当BBIC和RFIC封装在单个封装系统(SiP)中时,BBIC和RFIC信号可能会相互干扰. 根据傅立叶分析,BBIC中的主时钟信号线(如果时钟速度为20.0MHz或40.0MHz)将产生一个高频信号. 以40.0MHz时钟速率为例,傅立叶级数到第60位的频率为60×40 = 2400MHz,这与WiFi RFIC(2.4GHz-2.5GHz)通带的范围一致. 由于主时钟线通常为了功能而连接到BBIC中的几个电路元件,因此很可能靠近RF电路. 在这种情况下,RF电路可能成为主时钟信号的牺牲品,并且时钟线产生的耦合信号将成为噪声,这不仅可能会增加RF电路的噪声系数,而且可能会降低RF电路的选择性. 射频电路.

5 t8 V9 {“ k- \

. r'T + l3 H6 L- t. e $ D&X1 k“ n#s: h7 Z)a / P#o0?8〜; a

“ c6 f%C9 F(\ 1 f)为了分析主时钟线和RF组件之间的相互作用,将压控振荡器(VCO)中使用的RF电感器(6.0nH)放置在穿孔机中,在时钟互连附近穿过层基板(图6),我们在本研究中使用的互连长度为2.0 mm,当VCO电感和互连之间的横向距离(d)大于0.5 mm时,它将产生耦合信号小于-80.0dB. 耦合信号的实际要求由SiP系统级电气设计确定8 I)[4 s; i.?3}

6 I / K2 r“] $ g / Cc,e9 D

)o“ Bv3 O7 K4 y + H'?

5 m8 b- z#I2 f6 o,P“ M'C7 X

“ S(R&Z. [$ P;] + y)s + x

“ C#p4 s!q + W: C- v)x

/ _)M(l1 ^ 1 K: a53D堆叠芯片解决方案中主时钟线与RFIC之间的串扰Q!z#\ 6 {#J

+ v4 P'〜#Z&y- | -E1 w: V(q1〜!_“ H1?)S〜-E1 e)o

堆叠芯片方法可以减小封装的总面积. 此方法已广泛用于多种复合设备包中: 存储器和控制器,存储器和DSP,以及其他数字应用. RF SiP封装中可以使用这种方法吗?在回答这个问题之前,我们应该首先了解RFIC的特殊性. 5 {. A“ K: J(E(_ + P(w;`

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/tongxinshuyu/article-212074-1.html

-

-

申二官人

申二官人她168啊

这两种“黑技术”将陪伴小米净水器的秘密

这两种“黑技术”将陪伴小米净水器的秘密 10086江西移动网上营业厅 手机新闻早晚报|早报:OPPO新机亮相 国礼手机中国发布

10086江西移动网上营业厅 手机新闻早晚报|早报:OPPO新机亮相 国礼手机中国发布 室内光纤交接箱fc光纤法兰耦合器_光纤耦合器_fc光纤法兰手册

室内光纤交接箱fc光纤法兰耦合器_光纤耦合器_fc光纤法兰手册 58. 我爱我的狙击手链家.

58. 我爱我的狙击手链家.

桌子乱成那样