芯片工作原理 基于ARM 内核的SoC已经成为嵌入式处理器的开发实现(3)

电脑杂谈 发布时间:2018-02-08 06:30:09 来源:网络整理由于DDR2 SDRAM不能同时写入和读出,所以需要DDR2 SDRAM控制器加以控制。可根据连接到DDR2 SDRAM模块写入端和读出端的FIFO内部已存数据数量进行读写控制。写入端前的FIFO即为图3的FIFO3。连接到DDR2读出端的FIFO为图3的FIFO2,它与输出时序控制模块共同完成最终所需XGA图像的输出。DDR2 SDRAM每次操作指令时,以1行数据为单位,即接受1次读命令,则读出1行数据;同样,接受1次写入命令,则写入1行数据,此1行数据同时为XGA格式的1行(1 024个像素点数据)。

4 仿真与功能实现

在设计中,采用Verilog语言对各逻辑模块进行编写设计,在开发环境QUARTus II 9.1和Modelsim-aLTEra 6.5b下完成对各模块的时序的仿真和功能的设计和验证,如图5所示为数据进入水平插值器后的仿真结果,水平插值把原5像素插为新8像素的仿真,其中pix为待插值的5个像素,data为插值后的8个新像素。

图5 水平插值5像素插成8像素Modelsim仿真图

经过对各模块设计的仿真,并且对各模块功能验证正确后,进行系统整体的仿真验证,最终将处理完成图像数据送到LCD上进行显示,经过放大后的示例如图6 所示。仿真验证表明,得到的图像时序和数据与要求的时序一致,对于图像数据来说虽然双线性会对屏幕边缘存在高频分量的损失[4],使轮廓稍有模糊,但是从图像上对人眼观看的影响很小。

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/shumachanpin/article-66711-3.html

相关阅读

发表评论 请自觉遵守互联网相关的政策法规,严禁发布、暴力、反动的言论

-

-

邹嘉诚

邹嘉诚扬长而去

-

侯肖飞

侯肖飞有没有需要票的

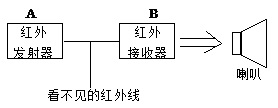

红外的制造方法

红外的制造方法 《勇者斗恶龙英雄2》真实武器如何获得?

《勇者斗恶龙英雄2》真实武器如何获得? 小神游sp_小神游sp官网_小神游sp全新

小神游sp_小神游sp官网_小神游sp全新

过的别太仔细了