芯片工作原理 基于ARM 内核的SoC已经成为嵌入式处理器的开发实现(2)

电脑杂谈 发布时间:2018-02-08 06:30:09 来源:网络整理3.2 图像缩放器模块

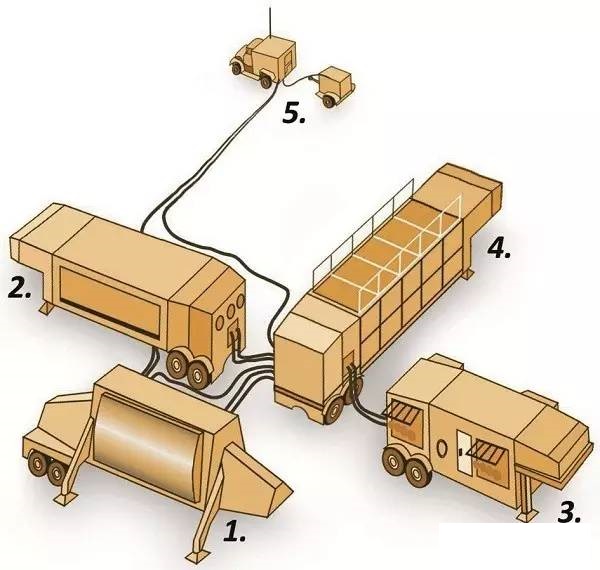

如图3所示,图像缩放器模块主要完成对输入图像数据源进行分辨率的缩放。根据设计,输入的图像数据为VGA 640×480格式,输出的图像数据为XGA 1024×768格式。由于输入图像数据与输出图像数据在完整1帧中的每一行像素点和每一列的数量上之比都为5:8,因此可考虑对输入的VGA信号作5:8的放大。先对数据在水平方向上进行插值放大,然后再进行垂直方向上的放大,设计中水平方向和垂直方向的插值放大均使用分级双线性插值算法。

图3 图像缩放器模块框图

3.2.1分级双线性插值 [3]

在双线性插值算法中,插值点的值根据其相邻的4个已知点计算得出,如图4所示。

图4 双线性插值算法原理图

已知a、b、c、d为输入图像内的相邻的4个点,其灰度值表示为f(x)。待插像素f点映射到原图像后的坐标值小数部分为[m,n]。计算f点灰度值的过程如式(1)~式(3)所示:

f[g]=f[a]+m(f(b)-f(a)) (1)

f[h]=f[c]+m(f(d)-f(c)) (2)

f[f]=f[g]+m(f(h)-f(g))

=(1-m)(1-n)f(a)+m(1-n)f(b)+(1-m)nf(c)+mnf(d) (3)

分级双线性插值使用的4个源图像像素点都是待插值点的直接邻点。插值的计算过程如下:

g(x)=(f(a)(m×N)+f(b)×(1-m)N)/N

其中,m与1-m分别是a点与b点的权值。因为是做5:8的转换,这里取C=N=8, 将原来为5个像素点的长度区间划分为8个区间,每个区间都有m×N与(1-m)N这一对权值组成的整数对。每个区间内部的待插值点都与该区间左边界取同样的值。8个区间的权值对应于(8,0)、(7,1)、(6,2)、(5,3)(4,4)、(3,5)、(2,6)和(1,7)。在确定好了点位置后,以查找表的方式写入权值与位置之间的关系,最后可根据内插点与临近点的相对位置查找对应系数,并通过计算得出各像素点的灰阶值。

3.2.2具体插值过程

3.2.2.1水平插值

将双线性插值分解为水平和垂直方向进行,由于是把原图像作5:8的放大,所以根据分级双线性插值,把原水平方向的5个像素点采用分8级双线性插值送入水平插值器。水平插值器由计数器与使能信号同时控制,每间隔5个时钟,水平插值器使能端置于计算插值状态,把进入的5个值进行一次插值变成新的8个像素点,之后再间隔5个时钟,将新的值进入插值器进行插值,直到把1行640个像素点插值为1行1 024个像素点。

3.2.2.2 垂直插值

垂直插值器完成垂直方向5:8的转换,即5行数据变为8行数据的转换,插值过程是按垂直方向对原来的5行数据采用分8级双线性插值,变换为新的8行数据。

完成水平插值的数据流水线型通过FIFO1与FIFO2模块,期间将FIFO1与FIFO2的值送入垂直插值器进行插值,完成垂直插值后的数据送入FIFO3与FIFO4模块,输出顺序排列在先的送入FIFO3,而另外一行数据进入FIFO4。FIFO3与FIFO4之间的数据也是流水线型进入到DDR2 SDRAM模块中,整个过程通过使用状态机对垂直插值进行控制,使经过垂直插值后的数据能以正确的顺序完成插值,并且送入DDR2 SDRAM模块。把对原5行数据经过水平和垂直插值变为8行数据的时间作为一个周期,直到完成整1帧VGA格式图像到1帧XGA图像的放大。

3.3 DDR2 SDRAM控制器模块

控制器模块的具体作用为:当SCALER完成图像数据处理后,把图像数据送进DDR2中储存,在确保DDR2中存储有2帧完整图像时,DDR2的读出端才开始读取,从第一帧图像地址读取图像数据,然后据根据时序控制从DDR2输出。当读完第一帧后,继续读取第二帧,此时第三帧继续写入原第一帧地址,之后的读取写入都按此过程进行。

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/shumachanpin/article-66711-2.html

-

-

苏泂

苏泂

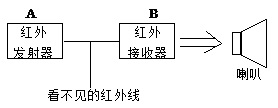

红外的制造方法

红外的制造方法 《勇者斗恶龙英雄2》真实武器如何获得?

《勇者斗恶龙英雄2》真实武器如何获得? 小神游sp_小神游sp官网_小神游sp全新

小神游sp_小神游sp官网_小神游sp全新

轮番到南海岛礁周边区域作业