【知识点】运算器的核心部件就是算术逻辑单元

电脑杂谈 发布时间:2021-06-07 06:00:49 来源:网络整理CPU的基本功能:

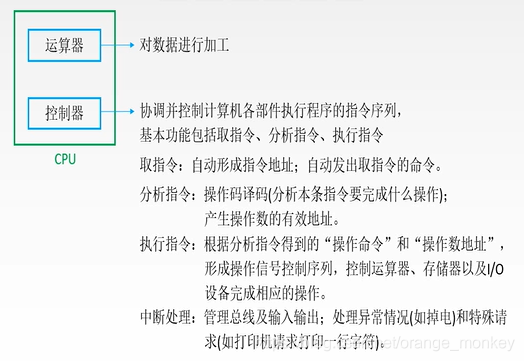

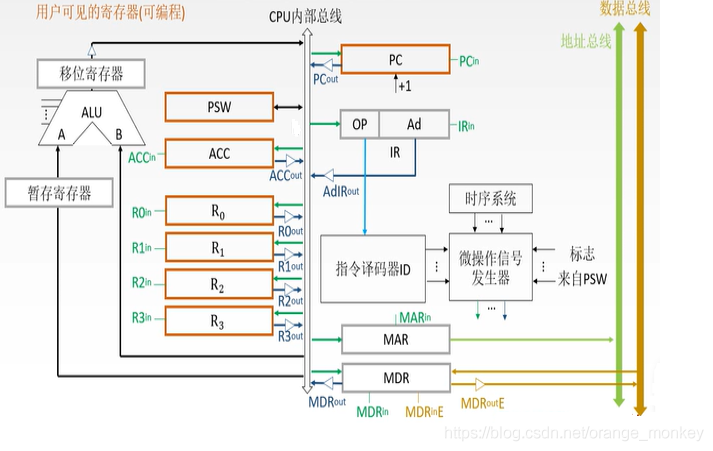

算术单元的基本结构:

算术单元的核心部件是算术逻辑单元。

算术逻辑单元是中央处理器(CPU)的执行单元,是所有中央处理器的核心部件。它由“与门”和“或门”组成,算术逻辑单元的主要功能是进行两位算术运算,如加、减、乘(不包括整数除法)。基本上,在所有现代 CPU 架构中,二进制都以补码的形式表示。

在运算中可能会产生一些中间结果,有时操作数是存放在寄存器中的,所以算术单元也会有一些寄存器。

如果ALU要使用寄存器中的数据,需要连接寄存器和ALU之间的线。这里有两种连接方式:

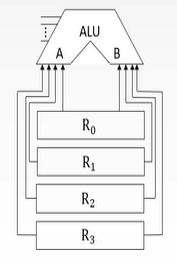

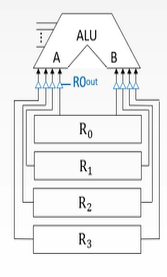

①专用数据连接方式:

由于寄存器可能会向ALU中的两个输入端的任一端发送数据,因此每个寄存器都需要同时连接到A和B。该图由一条线表示。其实连接数和寄存器的位数是一样的。

连接完成,但此时线路会有问题:

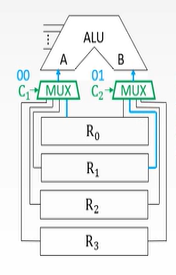

但是如何解决这个问题?

当控制信号为1时,线路接通,可以输出数据,当控制信号为0时,则相反。

专用数据连接方式的特点:

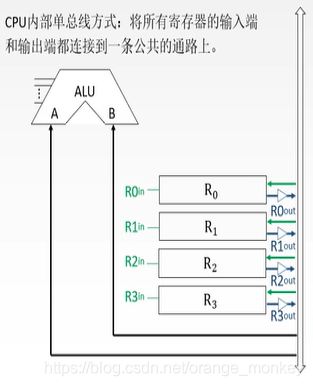

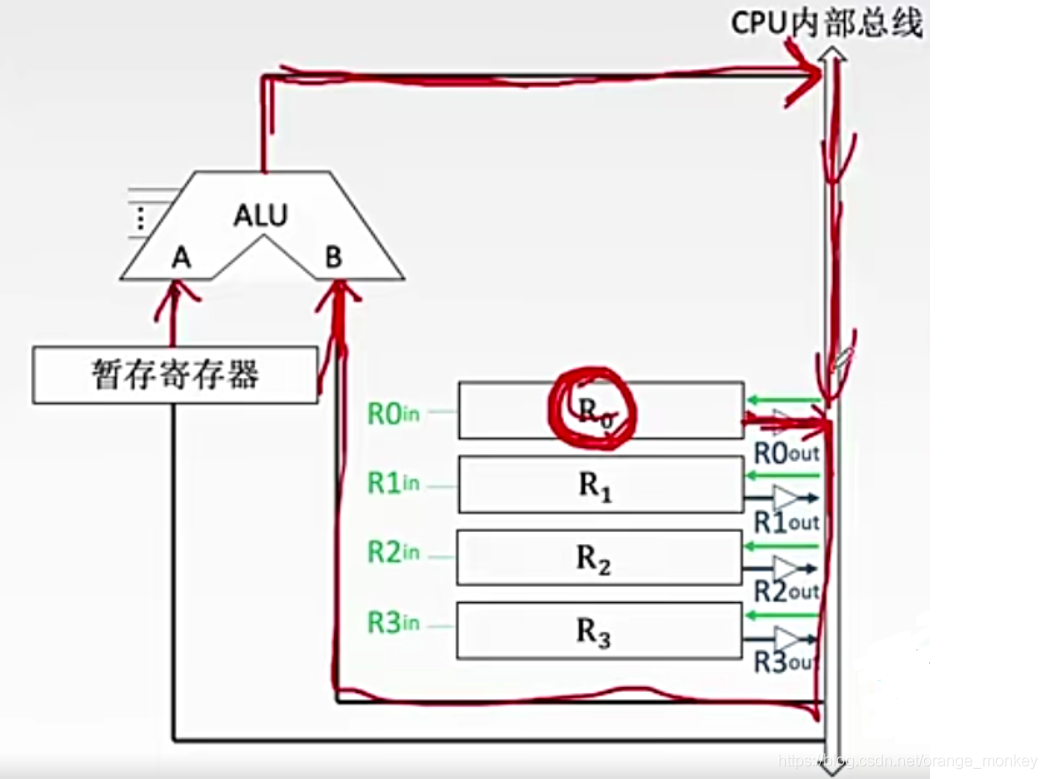

② CPU 内部单总线模式:

在CPU内部设置一条公共路径叫做CPU内部总线,让ALU和寄存器连接到总线上。任意两个组件的传输都是通过该总线实现的。如果要将R0的数据放到R1中,需要打开R0out,把R0的数据放到总线上,打开R1in的开关,把数据放到R1;如果同时R2和R3也想传输数据,则需要等待前一个进程完成后才能请求总线的服务。

现在寄存器的数据可以通过总线传输了,这些数据也可以作为ALU的输入,所以ALU的输入可以连接到总线上。

但是,当前的连接方式会导致总线冲突。如果要加R0和R1,R0和R1的数据是同时传输到总线上的,传输到ALU时无法确定两个输入端是什么。数据,那么如何解决这个问题?

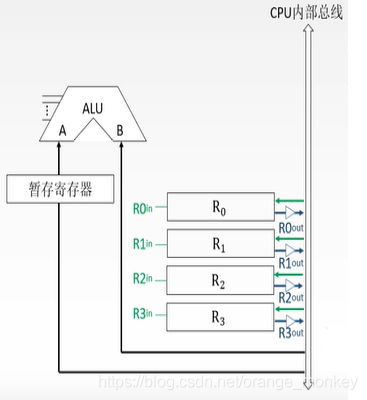

可以路的一端设置一个临时存储寄存器:

设置暂存寄存器后,这样就可以先将寄存器R0中的数据传送到总线上,通过总线R0的数据将存储在暂存寄存器中,然后三态R0 输出的gate 有效 如果信号失败,则打开R1 的输出信号,让R1 的数据输出到另一端。这样可以保证内部单总线正常工作。

注意:

暂存寄存器还有一个作用:

然后再考虑如何存储ALU计算后的结果?

如果ALU运算后的加法结果要存回寄存器R0,需要将ALU的输出接到总线上,那么ALU的输出也会通过总线传输,但现在问题出现了。只有在ALU的两个输入端等待输入信号稳定后,这个操作才可能得到正确的结果,但是因为其中一个操作数来自R0,而ALU在R0给出的输入信号稳定之前就已经存在了。生成输出信号并将其发送到总线。这将与 R0 发送到总线的电信号发生冲突。这会导致计算错误。如何解决这个问题?

你只需要设置一个暂存寄存器和一个三态门,这样就可以等待从R0输入ALU的信号稳定下来,ALU会先把运算结果放入暂存寄存器,等待ALU的输出结果稳定后,接三态门,将运算结果传送到总线,接R0的输入端,然后输入正确的运算结果加法运算返回到 R0。

CPU内部单总线模式特点:

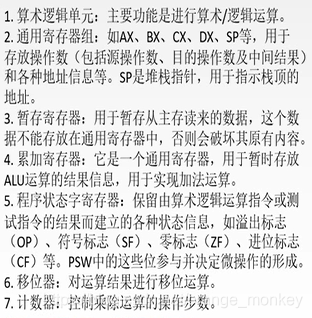

计算器总结:

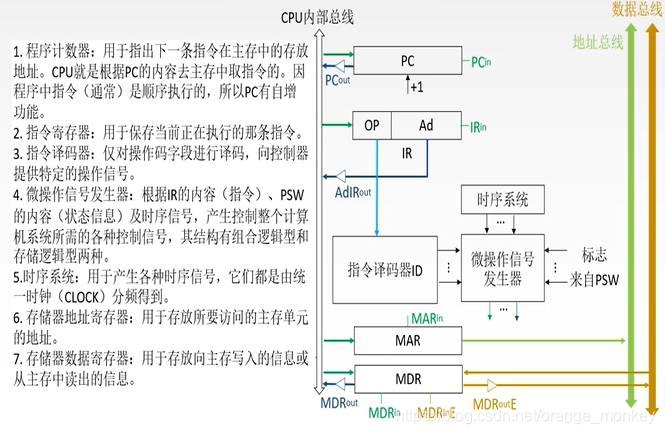

控制器基本结构:

CPU内部的基本结构:

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/shoujiruanjian/article-381020-1.html

- gotomycloud怎么用?gotomycloud注册?GoToMyCloud如何使用

- 凯立德2012夏季版?凯立德导航怎么升级?2016凯立德最新车载版?2012最新凯立德夏季版2921J0B下载

- youku free download?photo funia相册编辑?趣味照片合成(PhotoFunia)3.5.6去

- 8684公交数据包?8684离线版下载?8684公交下载?苏州8684公交查询

- 【灵信宝商务版客户端】灵信宝商务版客户端

- 灵信宝商务版_尽管太阳神孔蒂拉雅维拉科查是世间万物的创造

- 苹果6储存容量几乎已满?苹果4存储容量几乎已满?解决iphone“ 存储容量几乎已满”的办法

- 小雨伞下载?韩娱之幸福小雨伞女主?小雨伞法?小雨伞 v8.2.0.48 免费绿色版下载

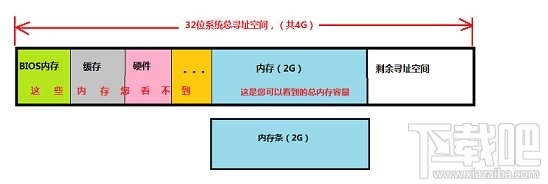

XP计算机最多支持多少RAM?

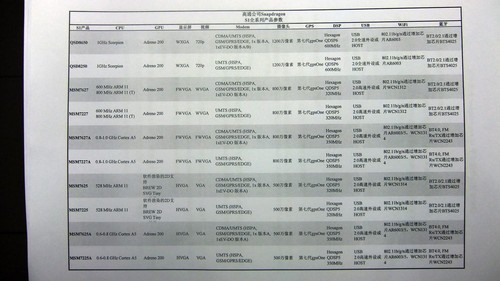

XP计算机最多支持多少RAM? 高通骁龙S1 MSM7227A的解释

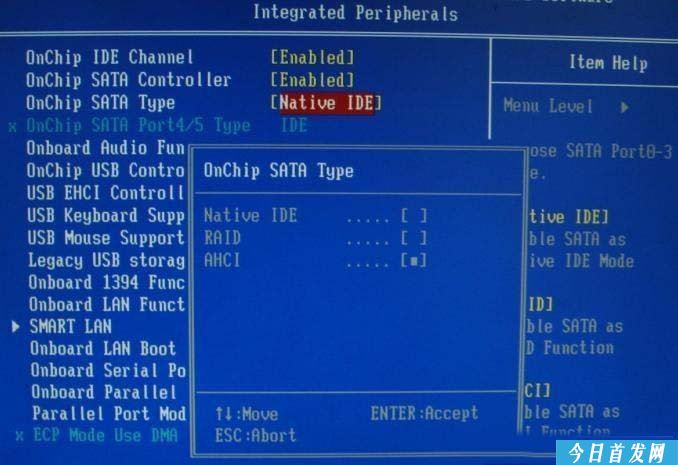

高通骁龙S1 MSM7227A的解释 杰微主板bios怎么检测硬盘 网友们知道怎么设置杰微BIOS吗?(图)

杰微主板bios怎么检测硬盘 网友们知道怎么设置杰微BIOS吗?(图)

11111111111