专家详细讲解:内存的工作原理和开发过程阅读后,重点总结和理解

电脑杂谈 发布时间:2020-12-19 19:06:00 来源:网络整理专家解释:记忆的工作原理与发展

基本内存存储原理:

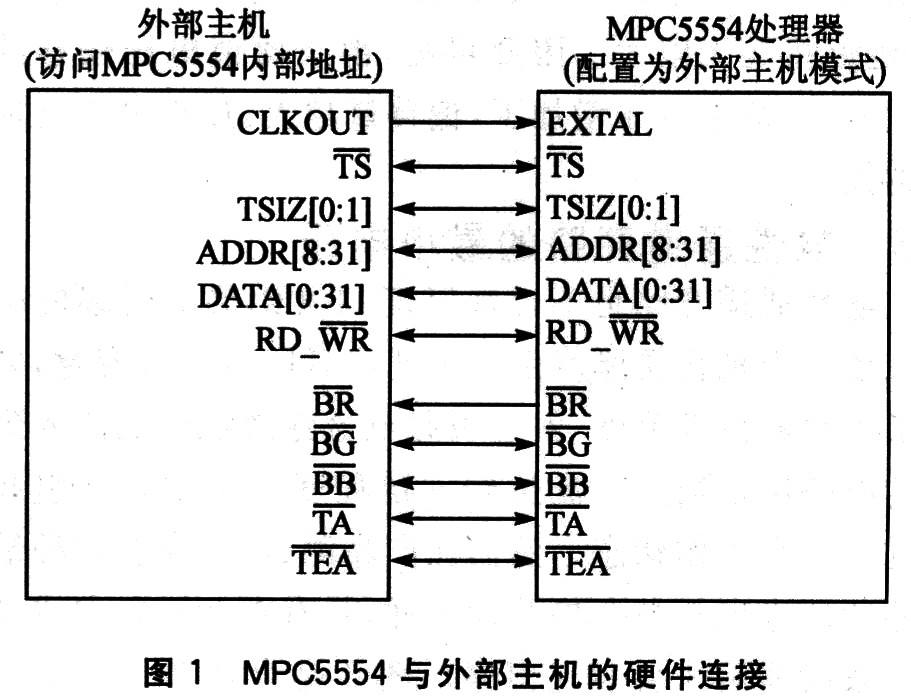

CPU首先需要从RAM中获取数据,并且它首先需要将数据的位置地址传输到地址总线。几个时钟周期后,数据总线会将数据传输到CPU。当地址接收到地址数据后的地址总线时,它将根据该地址数据找到相应的存储单元,然后数据总线会将数据传输到CPU。

在上图中,如果CPU每次调用都需要64位数据(数据总线为64位),则CPU一次将访问8个字节的数据,但是由于每次数据仍然访问1个字节,因此64位总线在这种使用中不会带来任何优势。

从“行”到“矩阵”

在制造实际芯片时,尤其是在大容量RAM(当前似乎具有64GB内存)的情况下,RAM被制成一条线或成阵列,这在设计上是不可能实现的。因此,我们可以将其排列成一个数组。当存储1024位(寻址单位是字节)时,我们需要一个32 * 32的矩阵来实现这一点。一个32 * 32的二维矩阵比一维的1024位元更紧凑。

在二维数据存储中,对于x86处理器,要读取的数据地址(22位二进制数字地址代码,11位行地址,11位列地址,寻址范围为4M ,2在传递到地址总线后,通过RAM地址接口(信号分隔符)进行分隔,行地址首先确定行地址,而列地址确认列地址,以便唯一的数据位置可以确定后,再通过RAM数据接口将其传输到数据总线,实际上RAM的内部存储数据不是正方形的(行小于列,易于刷新)。

SRAM:采用4-6晶体管实现,速度快,数据存储稳定,无泄漏,但价格昂贵,通常用于CPU辅助缓冲区。

DRAM:1个电容器+ 1个晶体管,但是由于漏电,它会在64ms的周期内刷新并充电。同时,读取数据需要放电,因此需要在特定时刻充电。充电和放电带来延迟,同时放电电流太小,需要信号放大器处理。

RAM封装技术

16K x 1bit SRAM芯片的引脚功能图:

早期的SRAM芯片采用20线双列直插式封装技术。针脚之所以如此多是因为:每个地址信号需要一条信号线,一条数据输入线和一条数据输出线,一部分控制线,电源线。

A0-A13是地址输入信号引脚,而CS是片选引脚。在实际的系统中,必须有许多SRAM芯片,因此您需要选择要从中写入或读取数据的SRAM芯片。 WE是写使能引脚。当SRAM获取地址时,它需要知道该做什么。无论是写入还是读取,WE都告诉SRAM写入数据。 Vcc是电源引脚。 Din是数据输入引脚。 Dout是数据输出引脚。 GND是接地引脚。

启用(OE):某些SRAM芯片也具有此引脚,但未在上图中。该引脚的功能与WE引脚的功能有关。让SRAM知道需要进行读操作。这不是写操作。从Dout引脚读取1位数据需要执行以下步骤:

SRAM读取操作:

1)通过地址总线将要读取的位的地址传输到相应的读取地址引脚(此时不应该激活/ WE引脚,因此SRAM知道不应执行写操作)

2)激活/ CS选择SRAM芯片。

3)激活/ OE引脚,让SRAM知道这是读取操作。第三步之后,要读取的数据将从Dout引脚传输到数据总线。

SRAM写操作:

1)使用地址总线来确定将信息写入何处(确保未激活/ OE引脚)。

2)通过数据总线将要写入的数据传输到Din引脚。

3)激活/ CS引脚以选择SRAM芯片。

4)Activation / WE引脚通知SRAM必须写。

经过上述四个步骤,需要写入的数据已经放置在需要写入的位置。

由于DRAM的数据刷新过程,设计更加复杂。以下是DRAM芯片引脚的功能。

下图显示了Intel的2188芯片使用16K * 1 DRAM 16行DIP封装。 16K * 1表示该芯片可以存储16 * 1024字节,并且可以同时读取或写入1个字节。Enter操作。

尽管该芯片只有7个地址引脚,但它使用多路复用技术通过DRAM接口将地址分为两个,然后使用两个连续的时钟来传输地址数据,其中一半的引脚用于获得所有地址位。转移。

为什么需要减少地址引脚?由于DRAM的成本比SRAM低,并且尺寸比SRAM小,因此它用于内存中并且具有大的存储容量。因此,它需要更多的地址线,并且需要在芯片中增加。引脚数,但是芯片的引脚是非常宝贵的资源。这无疑会增加芯片的生产成本,因此需要多路复用技术。

使用多路复用技术使读写过程更加复杂。

在上面的中,您可以看到与SRAM相比,DRAM结构中还有两个部分:由/ RAS(行地址选通)引脚控制的行地址锁存电路(行)。地址锁存器)和列地址锁存电路(列地址锁存器)由/ CAS(列地址选通:列地址脉冲选通)引脚控制。

DRAM读取过程:

1)通过地址总线将行地址发送到地址引脚。

激活2) / RAS引脚,以便将行地址传输到行地址锁存电路。

3)行地址根据接收到的数据选择相应的行。

确定4)/ WE引脚未激活,因此DRAM知道它将不执行写操作。

5)列地址通过地址总线传输到地址引脚。

6)/ CAS引脚被激活,因此列地址被传输到列地址锁存电路。

7)/ CAS引脚还具有/ OE引脚的功能,因此这次Dout引脚知道需要输出数据。

8)/ RAS和/ CAS被禁用,因此可以在下一个循环中执行数据操作。实际上,DRAM的写入过程和读取过程基本上是相同的,因此,如果您真的了解了上述过程,就可以知道写入过程,因此在此不再赘述。 (只需将第4步更改为/ WE引脚即可。)

DRAM用于定期读取DRAM的内容。优点如下:

1.仅使用/ RSA激活每一行,以达到刷新所有内容的目的。

2.DRAM控制器控制刷新,以防止刷新操作干扰常规的读写操作。因此,DRAM芯片的行数多于列数。

寻址单元(库)的实现和扩展

RAM单元只能存储一位数据,但是CPU访问和地址寻址是基于寻址单元(8位)的。 RAM如何实现CPU读写地址单元的实现? ?

最简单的事情是,我们需要8个1位RAM基本存储单元并行堆叠在一起,这8个芯片使用相同的地址。下图中仅显示了4个。

通常,这8个1bit芯片通过地址总线和数据总线连接到PCB(印刷电路板)上。对于CPU,它是8位RAM芯片,而不是8个独立的芯片。 1位芯片。上图所示的地址总线的位宽为22bit,因此该地址总线可以控制的内存模块的容量应为2 = 4194304bit的22倍,即4Mb * 8(4MB)容量;数据总线的位宽为8bit,这是通过将刚才提到的8个1bit基本存储单元的Dout并行实现的,这也可以满足CPU的要求。 (对于这种存储粒子,我们将其称为4194304 x 8模块或4Mx8。请注意,此处的“ M”不是“ MByte”,而是“ Mbit”)。为了说明这一点,我们以TI(Texas Instruments)生产的TM4100GAD8 SIMM存储器为例,因为该存储器的结构相对简单,每个人都易于理解。 TM4100GAD8基于4M x 8个模块制造,容量为4MB,具有30行SIMM封装。如果您了解我之前所说的内容,那么您应该知道该内存使用4Mx1 DRAM颗粒。可在TI的官方网站上找到以下数据(当前,很少有公司网站仍提供其先前产品的数据):结构:4194304×8。工作电压:5V。 30行SIMM(单行内存模块:SIMM)。采用8个4Mbit DRAM内存颗粒,塑料SOJs封装。长刷新周期为16毫秒(1024个周期)。

在上图中,A0–A10是地址输入引脚。 / CAS:行地址脉冲选通引脚。 DQ1-DQ8:数据输入/数据输出引脚。 NC:空信号引脚。 / RAS:列地址脉冲选通引脚。 VSS:接地引脚。 / W:写使能引脚。 VCC 5V电源引脚。

上面的电路图应该可以使我们更清楚地了解这个问题。 TM4100GAD8由8个4096x1bit芯片组成。 VCC和VSS为所有芯片提供5v电压。每个芯片都有/ RAS,/ CAS,/ W引脚与存储器的相应引脚连接。每个芯片都有一个不同的数据输出/输出接口。这样,我们应该能够知道RAM如何满足CPU访问数据的需求。

上面实现了8bit读取,但是在32bit和64bit读取中,这种方法还不够,我们需要扩展。这里我们介绍银行的概念。

此处,将4M * 8视为存储体,并并联连接4个存储体以形成位宽为32bit的存储体。对于64位存储库,需要8个存储库。在存储数据时,首先存储第一个存储体。第二个存储区存储第二个字节,这是相似的。每个存储体的容量为4M字节。

有两种方法可以增加这种类型的内存的容量,第一种是增加每个存储体的容量,第二种是增加存储体的数量。

上面的内存用于486级计算机,奔腾系列的内存与486不同。

SIMM和DIMM包装

SIMM(单个嵌入式内存模块,单个嵌入式内存模块)

由于内存颗粒无法直接连接到计算机并与计算机通信,并且由于数据位传输宽度和其他原因,内存制造商通过包装将它们组织在一起。

下图显示了30线DIMM和72线DIMM。

DIMM内存中的颗粒以DIP(双列直插式包装。PCBA过程中有DIP)包装。 SIMM存储器根据引脚分为30行和72行。

SIMM中一般容量为1,4,16MB的SIMM内存是单面的。当SIMM的容量为双面时。

72行SIMM存储器的数据总线宽度为32bit,因此大大提高了数据传输容量。

DIMM是当前内存的主要包装方式。如SDRAM,DDR SDRAM,RDRAM,其中SDRAM具有168个引脚并提供64位数据寻址功能。现在,高密度DRAM可以具有多个Din和Dout引线引脚,并且可以根据需要在DRAM芯片上制造4、8、16或64个数据引脚。

上图中的上部存储器是168行SDRAM,下部存储器是72行SIMM。

如果DRAM芯片具有8个数据引脚,那么当我们要实现4MB内存时,我们以前的方法是将4M * 1 8个芯片并行连接。但是现在我们可以通过4个1M * 8芯片实现。减少筹码数量。 4M寻址空间需要11个地址线引脚来复用地址数据。

FPM DRAM(不再使用现代内存)

了解FPM DRAM和EDO DRAM对于理解后续延迟非常有帮助

FPM DRAM是一种优先于动态随机存取存储器(DRAM)的新形式,而快速页面模式动态随机存取存储器(快速页面模式DRAM,FPM DRAM)是动态随机存取存储器。它是486时期常用的一种记忆。有30条线和72条线,电压为5V,带宽为32bit,基本速度为60ns以上。

页面模式动态随机存取存储器可以直接访问RAM行,而无需频繁重新指定该行。当列地址控制器(CAS)信号更改为读取一系列相邻的存储单元时,行地址控制器(RAS)信号保持有效。这减少了访问时间并降低了电源需求。 FPM DRAM的典型时序为6-3-3-3.

之所以称为快速页存储器,是因为它以4字节突发模式传输数据。这4个字节来自同一列或页面。如何理解这种阅读方式?如果FPM DRAM要突发4个字节的数据,它仍然需要依次读取每个字节的数据。例如,它需要读取数据的第一个字节。此时的情况与前面所述的DRAM相同。方式相同(通过阅读下面的FPM读取时序图,我们仍然了解其工作原理):

1、首先,将行地址传输到行地址引脚。在激活/ RAS引脚之前,RAS处于预充电状态,CAS也处于预充电状态。当然,/ WE此时仍然很高。 FPM至少知道它不会写。

2、/ RAS引脚被设置为低电平并被激活,将行地址发送到行地址选通,然后选择正确的行并将其发送到读出放大器,仅当/ RAS引脚被激活时同时,tRAC开始计时。

3、CAS一直处于预充电状态,直到将列地址传输到列地址引脚并且/ CAS引脚变为低电平并被激活(tCRC时间开始计数),然后我们还应该following很明显,列地址被发送到列地址选通,然后要读取的数据位置被锁定。此时,Dout引脚被激活,并且第一组数据被传输到数据总线。

4、对于先前介绍的DRAM,此时的读取周期已结束,但对于FPM,则有所不同。在传输第一组数据期间,CAS被禁用(RAS仍处于活动状态)并进入预处理。在充电状态下,等待第二组列地址传输到列地址引脚,然后传输第二组数据,依此类推,直到找到所有四组数据并完成传输为止。

5、当第四组数据开始传输时,RAS和CAS依次被停用,并进入预充电状态,因此完整的FPM读取周期结束。 FPM之所以能够实现这种传输模式,是因为需要读取的4个字节的行地址相同,但列地址不同,因此不必重复工作即可获得相同的列地址。

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/shoujiruanjian/article-341722-1.html

-

-

鲍靓

鲍靓来了

-

周映雪

周映雪大喊被美国人欺负了

- gotomycloud怎么用?gotomycloud注册?GoToMyCloud如何使用

- 凯立德2012夏季版?凯立德导航怎么升级?2016凯立德最新车载版?2012最新凯立德夏季版2921J0B下载

- youku free download?photo funia相册编辑?趣味照片合成(PhotoFunia)3.5.6去

- 8684公交数据包?8684离线版下载?8684公交下载?苏州8684公交查询

- 【灵信宝商务版客户端】灵信宝商务版客户端

- 灵信宝商务版_尽管太阳神孔蒂拉雅维拉科查是世间万物的创造

- 苹果6储存容量几乎已满?苹果4存储容量几乎已满?解决iphone“ 存储容量几乎已满”的办法

- 小雨伞下载?韩娱之幸福小雨伞女主?小雨伞法?小雨伞 v8.2.0.48 免费绿色版下载

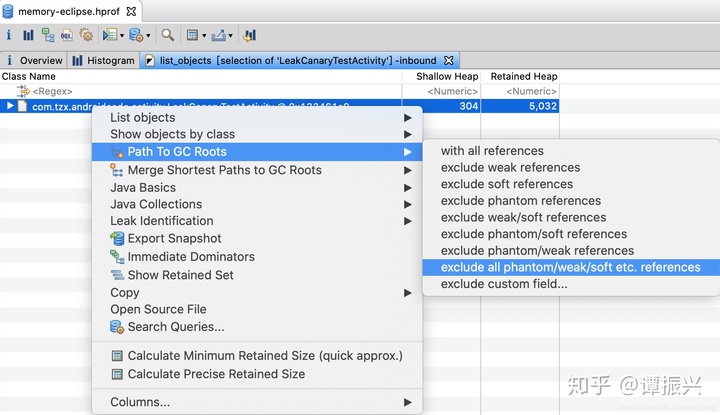

手动删除定时器和DOM的内存泄漏原因是什么?

手动删除定时器和DOM的内存泄漏原因是什么? 歌的大小看它所战的内存,和格式没关系

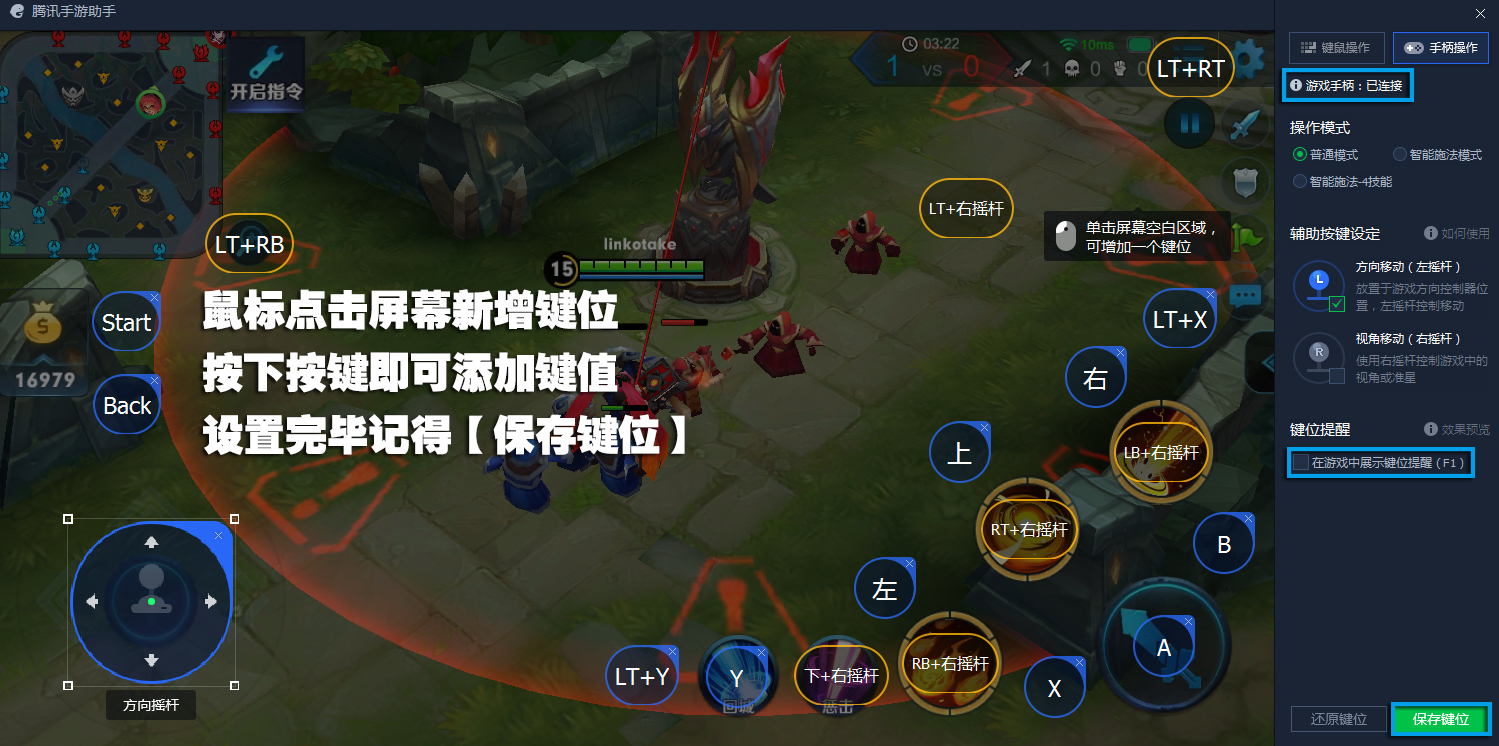

歌的大小看它所战的内存,和格式没关系 逍遥安卓模拟器《王者荣耀》专属功能键设置教程

逍遥安卓模拟器《王者荣耀》专属功能键设置教程 英特尔cpu风扇怎么拆下来?详细方法步骤及步骤介绍

英特尔cpu风扇怎么拆下来?详细方法步骤及步骤介绍

日本伤亡比俄军多几万人