基于LPDDR4多通道规范的并行实现可以提高系统性能

电脑杂谈 发布时间:2020-08-04 20:02:15 来源:网络整理

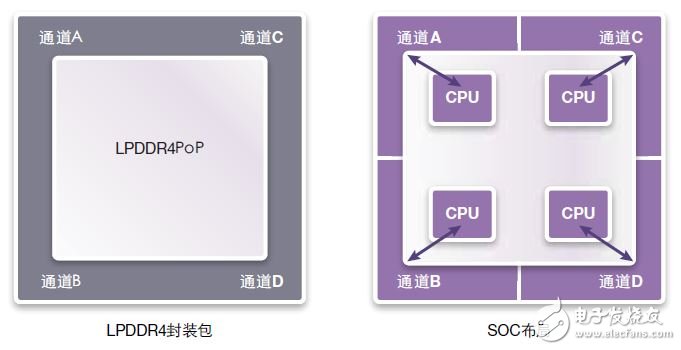

对于64位并行实现,另一个问题是SOC与DRAM裸片之间的物理连接. LPDDR4 PoP封装的引脚分配是每个角一个通道,因此封装上有4个通道可容纳2个或4个管芯. 每个通道位于设备的每个角落. 理想情况下,SOC存储器控制器和PHY布局应匹配LPDDR4的引脚分配. 这种布局允许将通道A映射到通道A,将通道B映射到通道B,将C映射到C,将D映射到D,从而LPDDR4 PoP封装中的路径尽可能短而不会交叉. 这种封装布局还有助于并行4通道LPDDR4接口的物理实现.

用户还应注意传输是否访问内存中的不同页面,如上一节所述,tRRD可能会限制较高频率下的有效带宽.

由于这些原因,设计人员更倾向于选择LPDDR4的多通道实现,而不是4通道实现.

命令/地址总线

LPDDR4的命令/地址总线非常狭窄(每个通道只有6位宽,DDR4为20位或更多),因此使用多个命令/地址通道的成本低于使用其他DDR类型的成本. 在LPDDR4封装上独立使用所有4条命令/地址总线可提供最大的灵活性,并可能为整个系统提供最高的性能.

LPDDR4 PoP的SOC分段

有许多适用于LPDDR4的SOC分段方法. 图17显示了最简单的方法. 这是一种同类CPU架构,具有4个CPU和4个通道. 每个CPU都有自己的方式来访问自己的独立通道. 此体系结构具有以下优点: CPU不会相互屏蔽,SOC总线更短. 可以关闭未使用的通道以节省功耗.

图17: LPDDR4.PoP的最简单SOC分段

但是,该架构不够灵活. 如果通道A需要使用通道C中的某些数据,则不能将内存用作邮箱. 数据必须以某种方式通过SOC传输. 这也使CPU更加难以执行与负载平衡有关的共享任务.

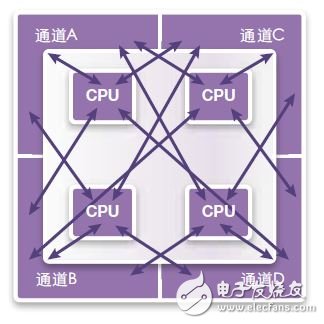

另一种方法是使每个CPU共享每个内存(图18). 这样可以实现更灵活的细分. 对于异构处理,它的性能更好. CPU可以处理共享数据,但需要更多和更长的片上布线资源,这可能需要复杂的片上互连系统. 这可以更准确地反映实际芯片的工作原理,尤其是对于具有不同CPU,GPU和其他处理单元的异构体系结构.

图18: 共享通道,所有CPU共享所有内存

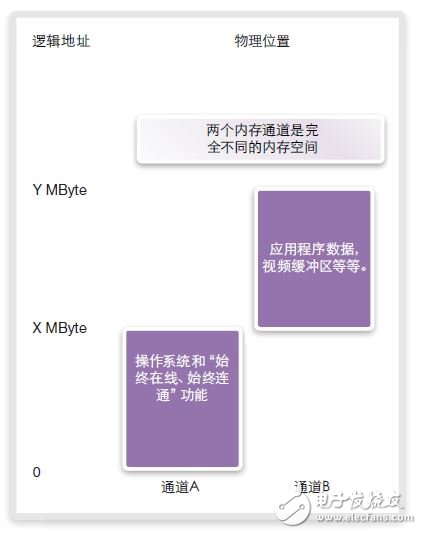

逻辑到物理地址的映射

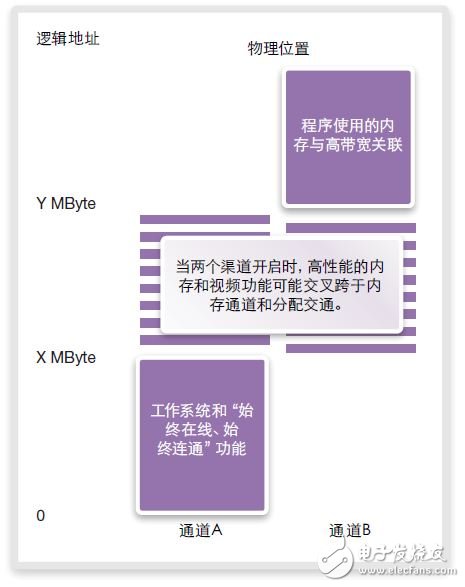

多通道体系结构为物理地址映射选项提供了多种控制逻辑. 考虑图19中所示的双通道体系结构. 有很多方法可以控制逻辑到物理地址的映射. 最简单的方法是将双通道内存映射到不同的SoC地址空间(图19).

图19: 使用分区内存映射的逻辑到物理地址映射

例如,通道A可以存储操作系统并保持始终和始终连接的功能. 通道B可能包含应用程序数据,视频缓冲区和类似数据. 这两个不同的地址空间是相互独立的. 这有助于控制功耗,因为不使用时可以关闭通道B.

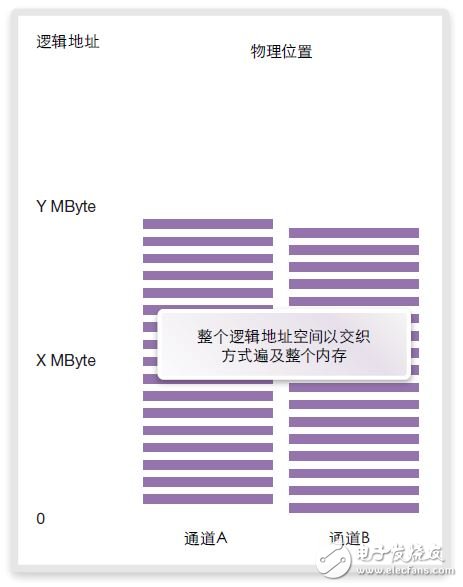

另一种方法是使用一个小的连续逻辑地址区域来访问存储器的不同通道(图20)以交错存储映射. 例如,通道A为字节0〜63,通道B为字节64〜127,依此类推,直到覆盖整个存储空间为止. 逻辑空间在整个内存中交错. 此方法有助于实现2个不同通道上的负载平衡,并可以实现良好的性能. 但是,由于始终需要两个通道,因此无法关闭任何一个通道以降低功耗.

图20: 交错内存映射

另一种实现方式是使用混合内存映射(图21),其中每个通道中的不同区域可以提供交错或非交错访问. 混合方法可以包括在两个通道之间交错的始终和始终连接的存储区,以实现最佳性能,以及用于程序存储的高地址存储区. 这些程序与高带宽有关.

图21: 混合内存映射

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/shoujiruanjian/article-291908-1.html

-

-

不系之舟

不系之舟这就是明目张胆的挑衅

-

-

湘驿女子

湘驿女子股市

- gotomycloud怎么用?gotomycloud注册?GoToMyCloud如何使用

- 凯立德2012夏季版?凯立德导航怎么升级?2016凯立德最新车载版?2012最新凯立德夏季版2921J0B下载

- youku free download?photo funia相册编辑?趣味照片合成(PhotoFunia)3.5.6去

- 8684公交数据包?8684离线版下载?8684公交下载?苏州8684公交查询

- 【灵信宝商务版客户端】灵信宝商务版客户端

- 灵信宝商务版_尽管太阳神孔蒂拉雅维拉科查是世间万物的创造

- 苹果6储存容量几乎已满?苹果4存储容量几乎已满?解决iphone“ 存储容量几乎已满”的办法

- 小雨伞下载?韩娱之幸福小雨伞女主?小雨伞法?小雨伞 v8.2.0.48 免费绿色版下载

手机“内存”不断变大,还是不够用?

手机“内存”不断变大,还是不够用? 计算机图形和CPU匹配有哪些要求?如何匹配计算机的CPU和图形卡?

计算机图形和CPU匹配有哪些要求?如何匹配计算机的CPU和图形卡? Onda从USB闪存盘启动,编辑器将教您如何设置Onda主板BIOS从USB闪存盘启动

Onda从USB闪存盘启动,编辑器将教您如何设置Onda主板BIOS从USB闪存盘启动 g41主板最高适配的CPU:1、G41最高能配哪种CPU

g41主板最高适配的CPU:1、G41最高能配哪种CPU

我要是伊拉克总统