【教程】终于有人把Java内存模型说清楚了!

电脑杂谈 发布时间:2019-06-30 12:11:59 来源:网络整理

【教程】终于有人把Java内存模型说清楚了!

Hollis 51CTO专栏 2018-07-26

网上有很多关于 Java 内存模型的文章,但是很读完之后还是搞不清楚,甚至有的人说自己更懵了。

java内存模型,指java程序在运行时内存的模型,而java代码运行在java虚拟机上,所以也就指java虚拟机的运行时内存模型。53c本语段的主题是介绍从化学宫,首先介绍它的地点,由此可以判断出首句是⑤,紧接着的是对学宫的整体介绍再到局部介绍,由此可以判断出第二句是①,第三句是④,跟着是遭到破坏,然后维修,所以可以判断第四句是③,第五句是②,第六句是⑥。特色介绍:金士顿骇客神条12gb套装内存能够大大增加64位操作系统的整体性能,配备金士顿12gb三通道内存后,用户、硬件发烧友和游戏玩家会发现,在进行音视频编解码、大尺寸图片处理以及运行大型游戏软件等应用时,系统性能会有非常明显的改善。

本文中很多说法都是笔者自己理解后定义出来的。希望能够让读者可以对 Java 内存模型有更加清晰的认识。

为什么要有内存模型

在介绍 Java 内存模型之前,我们先来看一下到底什么是计算机内存模型,然后再来看 Java 内存模型在计算机内存模型的基础上都做了哪些事情。

要说计算机的内存模型,就要说一段古老的历史,看一下为什么要有内存模型。

内存模型:英文名 Memory Model,它是一个老古董了。它是与计算机硬件有关的一个概念。那么,我先介绍下它和硬件到底有啥关系。

CPU 和缓存一致性

我们应该知道,计算机在执行程序的时候,每条指令都是在 CPU 中执行的,而执行的时候,又免不了和数据打交道。

而计算机上面的数据,是存放在主存当中的,也就是计算机的物理内存。

刚开始主存和内存的区别,还相安无事,但是随着 CPU 技术的发展,CPU 的执行速度越来越快。

004ae242 a1 00104000 mov eax,dword ptr ds:[004ae24c] //004ae24c处的内存读取004ae247 a3 00104000 mov dword ptr ds:[004ae24c],eax //004ae24c处的内存写入004ae24c 83c0 01 add eax,1 //004ae24c处的内存执行 那么我们应该如何中断在上面的几行呢。cache:缓存区,是高速缓存,是位于cpu和主内存之间的容量较小但速度很快的存储器,因为cpu的速度远远高于主内存的速度,cpu从内存中读取数据需等待很长的时间,而 cache保存着cpu刚用过的数据或循环使用的部分数据,这时从cache中读取数据会更快,减少了cpu等待的时间,提高了系统的性能。举例来说,存取内存 (ram) 的速度较磁盘驱动器快非常多,所以我们可以将一部份的主存储器保留当成磁盘cache,每当有磁盘读取的需求时就把刚读取的数据拷贝一份放在cache内存中,如果系统继续要求读取或写入同一份数据或同一扇区 (sector) 时,系统可以直接从内存中的cache部分作读写的动作,这样系统对磁盘的存取速度感觉上会快许多。

这就像一家创业公司,刚开始,创始人和员工之间工作关系其乐融融,但是随着创始人的能力和野心越来越大,逐渐和员工之间出现了差距,普通员工越来越跟不上 CEO 的脚步。

2、一些干部群众感情淡薄,服务意识不强,效率低下,急事慢办,能缓则缓、能拖则拖。3、缺少业绩考核,小区推广活动实施前未制定工作业绩指标,使得工作不效率,员工吃大锅饭,工作能力突出者与能力欠缺者同等对待,造成优秀员工未得到肯定,能力较差者工作效率低,这是我作为部门经理的一个主要责任。四是管理者自己要帮助能力欠缺员工提高绩效,也要号召和鼓励所有员工,对能力不足的员工提供技术支持。

可是,不能因为内存的读写速度慢,就不发展 CPU 技术了吧?总不能让内存成为计算机处理的瓶颈吧?

所以,人们想出来了一个好的办法,就是在 CPU 和内存之间增加高速缓存。

缓存的概念大家都知道,就是保存一份数据拷贝。它的特点是速度快,内存小,并且价格昂贵。

那么,程序的执行过程就变成了:程序在运行过程中,会将运算需要的数据从主存复制一份到 CPU 的高速缓存当中。

相对早期的版本,新版本通过对软件系统优化,对于涉及读取以及加载或写入数据的操作,可将运算拆分到多个处理器内核上,当第一个进程开始读取一部分数据后,第二个进程便可立即开始加载或写入该数据,从而大大提升系统的响应速度,也能更好地满足大并发应用需求。缓存主要用来存放那些读写比很高、变化很少的数据,这样应用程序读取数据时先到缓存中读取,如果没有或者数据已经失效再去访问或文件系统,并根据拟定的规则将数据写入缓存。管理系统为了向应用系统提供存取服务,将用户需要访问的数据装入主存中,再由读取主存里的数据来实现应用需求,即对数据的管理可以说是“基于磁盘的缓存技术。

许多知识的积累和能力的提高多数是在跟随领导、中层人员管理和检查工作、解决问题的实践中学到的。中层管理人员不直接指挥、协调一线人员的活动,他们主要是将高层管理者的决策和指示传达给基层管理者,同时将基层的意见和要求反映到高层管理部门,他们是连接高层管理者与基层管理者的桥梁和纽带。三、强化中层管理队伍建设与各项制度的健全、落实,为有 效开展运营工作创造有利条件 1、厂内中层管理队伍业务素质良莠,直接决定着工作方针 的履行情况与各项制度的落实效率。

因为管理人员是了解手下的人员以及自己负责的事情的。所以大多数时候,公司的各种决策,通知等,CEO 只要和管理人员之间沟通就够了。

而随着 CPU 能力的不断提升,一层缓存就慢慢的无法满足要求了,就逐渐的衍生出多级缓存。

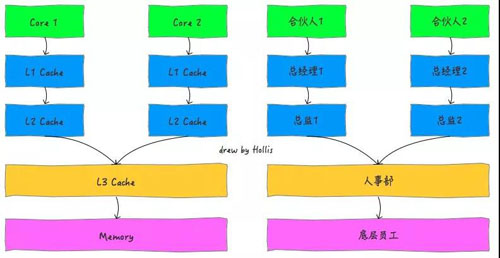

按照数据读取顺序和与 CPU 结合的紧密程度,CPU 缓存可以分为一级缓存(L1),二级缓存(L2),部分高端 CPU 还具有三级缓存(L3),每一级缓存中所储存的全部数据都是下一级缓存的一部分。

这三种缓存的技术难度和制造成本是相对递减的,所以其容量也是相对递增的。

那么,在有了多级缓存之后,程序的执行就变成了:当 CPU 要读取一个数据时,首先从一级缓存中查找,如果没有找到再从二级缓存中查找,如果还是没有就从三级缓存或内存中查找。

a、计划级、控制级、操作级 b、高层决策级、中层决策级、基层作业级 c、战略级、战术级、作业级 d、战略级、战术级、策略级 11、应用软件系统开发的发展趋势是采用( )的方式。一个公司正常情况下,有高中低三层职位划分,高层为管理层人员,如coo,vp,中层为总监级别,底层为经理级别,每一个层都拥有不同的权力,高层一般拥有公司的拥有权,因为大多数高层基本拥有股份或者是股东,中层拥有的是决策权,根据市场,商务,以及具体的情况,中层决定到底做不做,而底层则是更加专注于执行权,比如如何把一个事情按时做好,是底层的目标。a、中层管理 b、高层管理c.基层管理 d.目标管理 4.管理的职能主要包括( )。

具备三级缓存系统,cpu各核心与核芯显卡共享3mb三级缓存。至于cherry trail平台的架构设计,每个airmont核心都是双发射、乱序指令结构,l1缓存由32kb 8-way指令缓存及24kb数据缓存组成,2个核心共享1mb l2 16-way缓存,考虑到cherry trail会有2-4核产品,所以l2缓存会是1-2mb,不过cherry trail跟之前的bay trail一样也没有l3缓存。fx-8150是8核cpu,其中4核共享数学处理单元、640kb 的l1缓存、8mb的 l2缓存以及8mb的l3缓存。

公司也分很多种,有些公司只有一个大 Boss,他一个人说了算。但是有些公司有比如联席总经理、合伙人等机制。

单核 CPU 就像一家公司只有一个老板,所有命令都来自于他,那么就只需要一套管理班底就够了。

到事务所后不久,深圳果然争取到了在全国率先设立合伙制所的政策,每个都面临重新选择:留在国办所,或者出去创办合伙所。最后,他透露道,未来天狮集团将搭建全球化财务大共享,实现全球财务共享、业务共享,以最大效能提速增量,以合伙创天下机制,与全球天狮人共创天下,将全球化发展体制机制夯实落地。一个公司正常情况下,有高中低三层职位划分,高层为管理层人员,如coo,vp,中层为总监级别,底层为经理级别,每一个层都拥有不同的权力,高层一般拥有公司的拥有权,因为大多数高层基本拥有股份或者是股东,中层拥有的是决策权,根据市场,商务,以及具体的情况,中层决定到底做不做,而底层则是更加专注于执行权,比如如何把一个事情按时做好,是底层的目标。

还有的公司,不断壮大,开始拆分出各个子公司。各个子公司就是多个 CPU 了,互相之前没有共用的资源。互不影响。

下图为一个单 CPU 双核的缓存结构:

随着计算机能力不断提升,开始支持多线程。那么问题就来了,我们分别来分析下单线程、多线程在单核 CPU、多核 CPU 中的影响。

单线程:CPU 核心的缓存只被一个线程访问。缓存独占,不会出现访问冲突等问题。

单核 CPU,多线程:进程中的多个线程会同时访问进程中的共享数据,CPU 将某块内存加载到缓存后,不同线程在访问相同的物理地址的时候,都会映射到相同的缓存位置,这样即使发生线程的切换,缓存仍然不会失效。

但由于任何时刻只能有一个线程在执行,因此不会出现缓存访问冲突。

多核 CPU,多线程:每个核都至少有一个 L1 缓存。多个线程访问进程中的某个共享内存,且这多个线程分别在不同的核心上执行,则每个核心都会在各自的 Cache 中保留一份共享内存的缓冲。

由于多核是可以并行的,可能会出现多个线程同时写各自的缓存的情况,而各自的 Cache 之间的数据就有可能不同。

在 CPU 和主存之间增加缓存,在多线程场景下就可能存在缓存一致性问题,也就是说,在多核 CPU 中,每个核的自己的缓存中,关于同一个数据的缓存内容可能不一致。

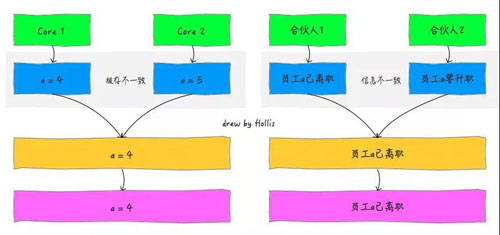

如果这家公司的命令都是串行下发的话,那么就没有任何问题。

如果这家公司的命令都是并行下发的话,并且这些命令都是由同一个 CEO 下发的,这种机制是也没有什么问题。因为他的命令执行者只有一套管理体系。

如果这家公司的命令都是并行下发的话,并且这些命令是由多个合伙人下发的,这就有问题了。

因为每个合伙人只会把命令下达给自己直属的管理人员,而多个管理人员管理的底层员工可能是公用的。

根据《协议》约定,《协议》生效需要以“经过蕙富骐骥合伙人大会决议通过”、“经过珠海泓沛全体合伙人决议通过”且北京鸿晓出具关于‘承接汇垠澳丰原有重组承诺并在2018年6月24日前完成相关资产重组’的承诺函为前提条件,如《协议》生效且履行,则蕙富骐骥gp将变更为北京鸿晓,公司实际控制人将变更为李红星。殊不知收益首先要满足合伙人的分红最后瓜分的差不多了也要决议讨论分不分给员工,分给员工多少。6月14日,核实调,新总部布处理结果,撤销该店合伙资质,并对涉事员工做出了辞退处理。

合伙人 1 命令下达后,管理人员 a 在辞退了员工后,他就知道这个员工被开除了。

而合伙人 2 的管理人员 2 这时候在没得到消息之前,还认为员工 a 是在职的,他就欣然的接收了合伙人给他的升职 a 的命令。

处理器优化和指令重排

上面提到在 CPU 和主存之间增加缓存,在多线程场景下会存在缓存一致性问题。

除此之外,为了使得处理器内部的运算单元能竟可能被充分利用,处理器可能会对输入代码进行乱起执行(out-of-order execution)优化,处理器会在计算之后将对乱序执行的代码进行结果重组,保证结果准确性。由于不同硬件架构的处理器之间的指令不能相互通用,但是在功能上又有很多一致的地方,都能对一定长度的二进制数进行各种运算操作,比如加法指令,在x86硬件系统中有,在mips硬件系统中也有,虽然具体的硬件实现上有所不同,指令的二进制代码也不同,但对人们而言作用是共同的,于是我们把这些相同的功能进行抽象,并制定相应的一套语法系统,让编译器能把一组相同的代码针对不同的硬件编译出不同的二进制代码,就开发出了当前的中间语言。该系列显示器采用了运动侦测与补偿运算、内插运算、边缘平滑处理及杂波信号抑制等尖端处理技术,其3d视频亮色分离电路单元,3d的逐行处理及帧频归一转化电路单元,3d数字信号降噪单元,可将普通pal/ntsc隔行扫描视频信号采集变为逐行扫描的,高画质、“超高清分辨率视频处理与显示”、“信号的高速切换与传输”、“嵌入式处理器技术”、“应用软件工具与平台”的高清电视和计算机图像信号。

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/jisuanjixue/article-109489-1.html

-

-

李赛楠

李赛楠加油

-

raspberry pi 当树莓派遇上NEC,物联网时代的显示器长什么样?

raspberry pi 当树莓派遇上NEC,物联网时代的显示器长什么样? 金山毒霸冲击波蠕虫特杀工具v1.1绿色版

金山毒霸冲击波蠕虫特杀工具v1.1绿色版 使用winrar自解压功能制作安装包

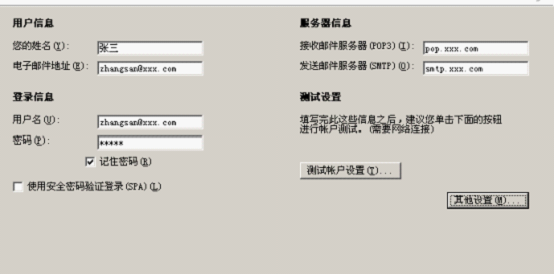

使用winrar自解压功能制作安装包 我的OUTLOOK2003,只能接受邮件不能发送.一群发就让输入网络密码.

我的OUTLOOK2003,只能接受邮件不能发送.一群发就让输入网络密码.

芝麻糊还有肉末