图像算法工程师笔试题 通过Viterbi译码算法实现译码器优化实现方案(2)

电脑杂谈 发布时间:2018-10-02 05:06:53 来源:网络整理每一种可能的状态转移都根据接收到的有噪声的序列r计算路径度量,然后选择出各个状态的最小度量路径(幸存路径)。

可以看出dfr计算的误差最小,所以dfr的计算较为准确。

大家知道吗,人们对于声音承受的能力是有一定限制的,所以,超过限制的就被称作是噪音。

4 FPGA实现及验证

4.1 FPGA实现的整体框架

采用Altera公司的QuartusⅡ为开发工具,以EPlS25的FPGA为验证平台,用于设计和验证本文提出的Viterbi优化译码算法,译码器整体设计框架如图2所示。译码器结构主要包括时钟单元、主控单元、全并行ACS单元、回溯单元及译码输出单元。

(1)时钟单元

用于把板级时钟经过锁相环分频获得译码器所需的工作时钟。

(2)主控单元

给出各种控制信号,控制其他各单元的工作时序,保证译码器各模块协调工作。

(3)支路度量与全并行ACS单元

对数似然比模块(llru)根据分支度量与状态度量值计算对数似然比与外信息,其基本运算也是类似smu中的加比选(acs)操作,相应的算法结构如下(转移路径按输入分别为0和1分为两组,状态从0~7排列):。

实用新型内容[0006]本实用新型的主要目的在提供一种有线电视调制解调器结构,包括电力转换单元、输出控制及盗接检知单元、上行控制单元、上行传送单元、混频单元、下行接收单元、下行控制单元及数据连接单元,其中电力转换单元将比如市电的输入电源转换成适当的输出电源以供其它单元使用,输出控制及盗接检知单元连接住户电视使用端,可产生上行信息, 比如可包含盗接状态,并以振幅位移调变(ask)方式经上行控制单元、上行传送单元、混频单元及数据连接单元传送至计算机,同时,数据连接单元可将计算机的下行信息经混频单元、下行接收单元及下行控制单元,而以频率位移调变(fsk)方式传送至输出控制及盗接检知单元。

专利摘要一种有线电视调制解调器结构,包括电力转换单元、输出控制及盗接检知单元、上行控制单元、上行传送单元、混频单元、下行接收单元、下行控制单元及数据连接单元,电力转换单元将输入电源转换成其它单元的所需电源,输出控制及盗接检知单元连接住户电视使用端,可产生上行信息,而以振幅位移调变方式藉上行控制单元、上行传送单元、混频单元及数据连接单元传送至计算机,且数据连接单元可将计算机的下行信息经混频单元、下行接收单元及下行控制单元,而以频率位移调变方式传送至输出控制及盗接检知单元以控制有线电视信号的播放,因此,本实用新型可达成及传播的功能。

3143表3-1 存储器的用途和特点名称简称用途特点高速缓冲存储器cache高速存取指令和数据存取速度快但存储容量小主存储器主存存放计算机运行期间的大量程序和数据存放系统程序和大型数据文件及存取速度较快存储容量不大外存储器外存存储容量大位成本低1533.1.3 存储器的技术指标1. 存储容量:指它可存储的信息的字节数或比特数通常用存储字数单元数 存储字长每单元的比特数表示。

(4)回溯单元

第4章信道编码k比特块 mk信息比特 n , k 分组 编码输出 1 复用 系统编码器 m n -k 校验比特块 1 长度n=mk n , k 分组 2 块交织器 系统编码器 m n -k 2 校验比特块 图4-14 并行级联分组码编码方框图 第4章信道编码4.6.2 串行与并行的级联卷积码 1. turbo码 带交织的并行级联卷积码pccc parallelly concatenatedconvolutional codes 也叫turbo码,turbo编码器的基本结构如图4-15所示, 它由两个并联的递归系统卷积码rsc recursivesystematic convolutional )编码器组成,并在第二个编码器前面串接了一个交织器。

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/jisuanjixue/article-89160-2.html

Win7wlan无线热点配置工具,适合需要共享网络的朋友

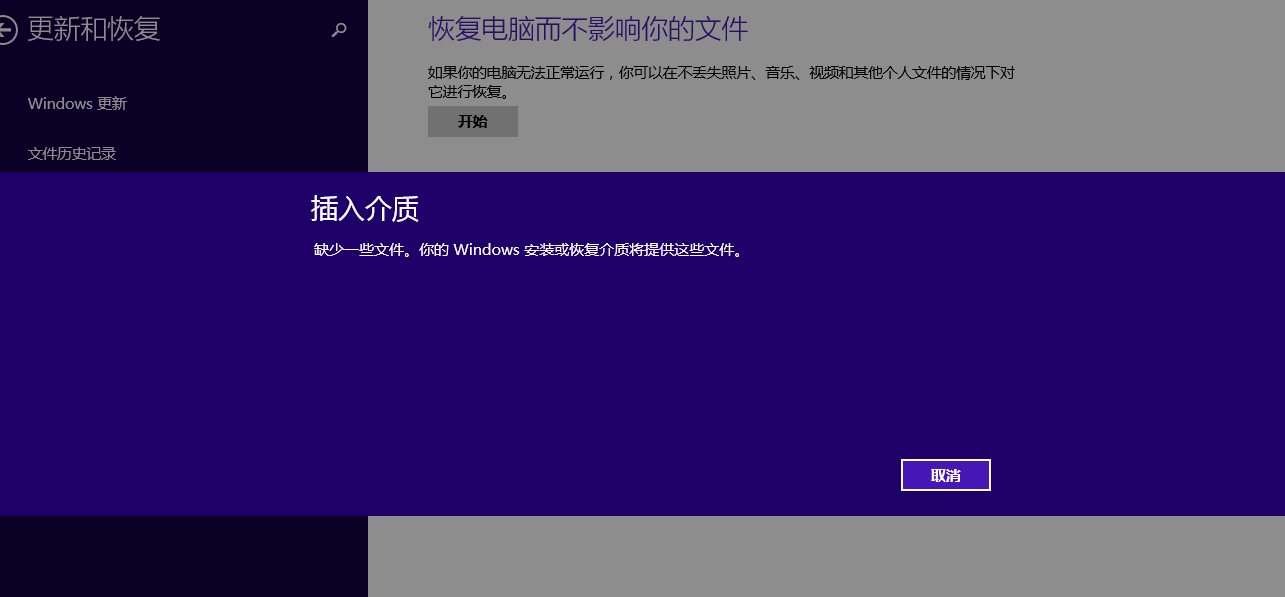

Win7wlan无线热点配置工具,适合需要共享网络的朋友 win8.1如何恢复出厂设置| win8如何恢复出厂状态而不会丢失

win8.1如何恢复出厂设置| win8如何恢复出厂状态而不会丢失 手机操作系统中包含什么

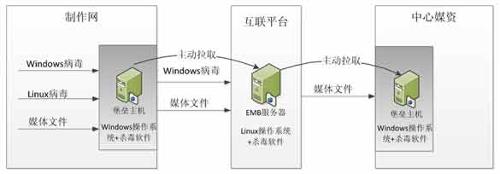

手机操作系统中包含什么 文件型病毒的存在方式_淘宝 手机存在木马病毒提醒_存在方式

文件型病毒的存在方式_淘宝 手机存在木马病毒提醒_存在方式

对于马云的讲话