数字钟电路设计与制作报告前言_数字钟报时电路_数字钟电路图(3)

电脑杂谈 发布时间:2017-05-28 23:08:30 来源:网络整理如果严格按照仿真图的标号联线则不会出现上述问题。(6)调试基本功能电路电路焊接完成并不意味着就会出现正确结果。连接完成通电之后往往还是会出现很多的问题。数字钟电路设计与制作报告前言这时候要首先要从硬件连接上检查,排查有没有引脚接错位置,同时使用万用表测量是否连接完好。在我的电路板调试过程中,不管是分位还是秒位的十位都是在各位为跳到9的同时跳转,也就是提前1秒或者1分进行加一跳转,在确定硬件连接没有错误之后,从原理上寻找问题,发现multisim中的74ls160时钟脉冲信号是下降沿有效,实际中7474ls160的脉冲信号是上升沿有效,由于74ls160的进位信号是在第九个脉冲打来时出现高电平第十个计数脉冲来到的时候回到低电平,所以按照仿真电路连接的时候就会出现在各位跳到9的时候十位就同时跳转的情况,为了解决这一问题,让进位输出经过一个非门反向后接到十位计数脉冲,结果显示为理想结果。(7)拓展电路的设计与调试。由于实验室中没有蜂鸣器,所以用发光而接管代替蜂鸣器来进行整点报时。在第59分钟的51秒53秒55秒57秒59秒让发光二极管点亮,其余时间均为熄灭状态。整个调试过程主要是通过发光二极管的电流的控制。之前由于使用的电阻不够大,通过发光二极管的电流电路的电流过大以至于都影响到前一级的与非门以及其他与非门的工作,使整个电路的计时结果都受到影响,每当第一次点亮二极管之后,计数器都自动清零了。

思考许久之后试探着把分压电阻选成47k欧姆的,结果就实现了所需的现象。七、心得体会 整体规划很重要,同时必须要有足够的耐心,脚踏实地一点一点的完成。 在拿到课程设计题目的时候,第一步要根据设计要求,思考原理以及实现方案。第二步要根据自己所选定的方案确定选用那些元器件,然后查阅相应芯片的资料,掌握其引脚分布以及用法。第三部将整体的设计分成各个子模块,然后一个模块一个模块的进行设计,最后将各个子模块整合在一起进行整体仿真。数字钟电路设计与制作报告前言整个仿真过程中必须仔细认真,而且要有足够的耐心,不厌其烦的进行测量校正修改。直到得到预想的结果。焊接过程中,要严格根据自己的仿真图逐层逐步的进行,防止出现漏焊或者焊接混乱的现象发生。第一步要对整体的布局做规划,不仅要美观,更要方便焊接。第二步,焊接过程中必须小心谨慎,在讲求美观的同时,更要保证焊接点可靠。第三步便是调试过程了,调试过程中出现的问题,要从原理分析找出问题的大概位置,然后对电路连接进行仔细检查。 也许是自己对电子设计方面很感兴趣,整个都是轻松愉快的。同时在焊接过程中比较仔细认真所以出现的问题不多,每次出现了问题也都是很认真仔细的去排查,最终将整个数字钟的设计基本完成。

不过还是有部分问题没有得到很好的解决,按钮消抖部分做的不够好。在以后的相关设计制作中,必须更加仔细认真严谨的去对待。八、附录1、所用芯片及其参数:序号 名称 元件编号 参数 备注 1 数码管 BS202 4 2 十进制计数器 74LS160 4 3 译码器 74LS48 4 4 二输入非门 74LS00 3 5 四输入与非门 74LS20 1 6 非门 74LS04 1 7 三五定时器 NE555 1 9 轻触开关 1 10 电阻 47k\3.3 k\100 k 4\1\4 11 可变电阻 2k 1 12 发光二极管 红、绿 各1个 13 瓷片电容 0.01uF 2 14 点解电容 10uF 12.参考文献【1】数字电子技术基础(第五版) 高等教育出版社【2】74LS00、74LS04、74LS74、74LS153、74LS138、74LS160 NE555等芯片数据手册【3】互联网上的资料1校时脉冲+5VC1 C2 0.01 FC1 S1C2 S23.3K3.3K秒十位进位脉冲扩展 部分主体部分整点报时仿电台报时定时控制分频器振荡器校时电路秒计数器分计数器时计数器秒译码器分译码器时译码器秒显示器分显示器时显示器分十位进位脉冲至分个位计数器至时个位计数器图2 用整体置零法构成的12进制计数器11174LS160RD’LD’CQ0 Q1 Q2 Q3EPETCLKD0 D1 D2 D374LS160RD’LD’CQ0 Q1 Q2 Q3EPETCLKD0 D1 D2 D3CLK+5VQ0◇◇Q2Q0分十位Q3Q0分个位1KY时十位Q1Q2图5 定时控制电路

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/jisuanjixue/article-49803-3.html

-

-

曾协

曾协必须给他弄沉

-

王彪

王彪欧美发达国际同居制度正在取代婚姻制度

我可以感染乙肝多久?

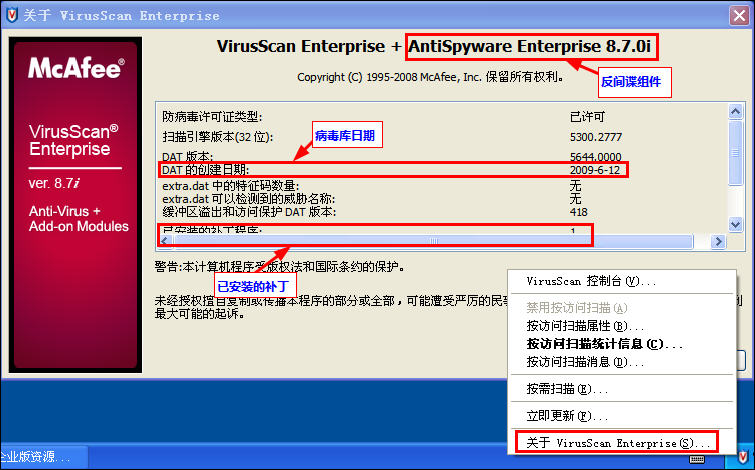

我可以感染乙肝多久? 四个个人防火墙软件评估的国际部分

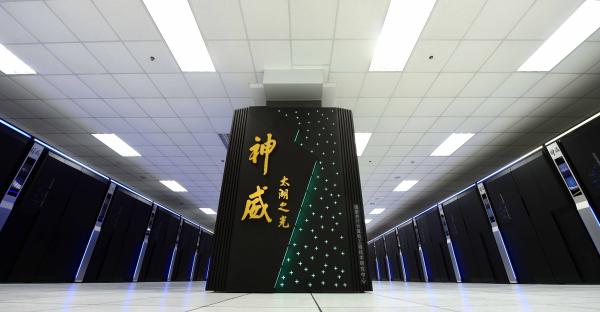

四个个人防火墙软件评估的国际部分 超级计算机“神威·太湖之光”是世界上最快的

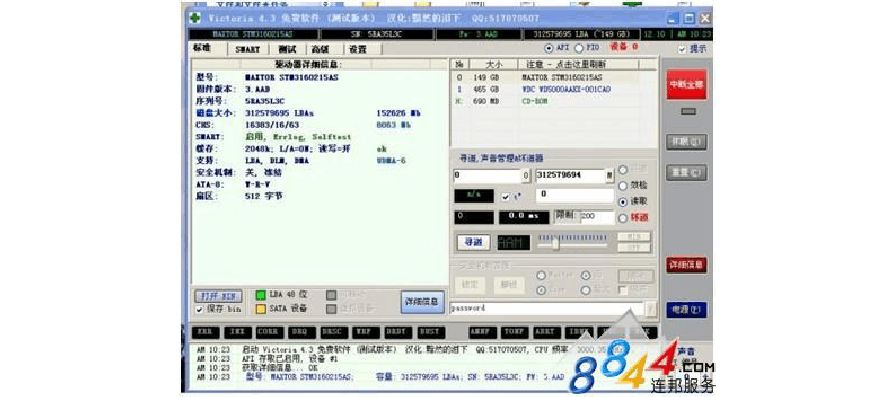

超级计算机“神威·太湖之光”是世界上最快的 硬盘修复_硬盘坏道屏蔽修复_硬盘坏道修复多少钱

硬盘修复_硬盘坏道屏蔽修复_硬盘坏道修复多少钱

又后悔更新了