数字钟电路设计与制作报告前言_数字钟报时电路_数字钟电路图

电脑杂谈 发布时间:2017-05-28 23:08:30 来源:网络整理《数字钟电路设计与制作》课程设计报告班 级: 建筑设施智能技术二班姓 名: ***** 学 号: ******** 指导教师: ***** 2010年 11月 19日目 录一、 内容摘要……………………………………………3二、 设计内容及要求……………………………………3三、 总设计原理…………………………………………3四、 单元电路的设计……………………………………61、 基于NE555的秒方波发生器的设计……………52、 基于74LS160的12\60进制计数器的设计……73、 校时电路…………………………………9五、 设计总电路图………………………………………10六、 主要仪器及其使用方法……………………………10七、 设计过程中的问题及解决方案……………………、 心得体会……………………………………………12九、 附录…………………………………………………13数字钟的电路设计与制作一、内容摘要:数字钟是一种用数字电路技术实现时、分、秒计时的装置,与机械式时钟相比具有更高的准确性和直观性,且无机械装置,具有更更长的使用寿命,因此得到了广泛的使用。数字钟从原理上讲是一种典型的数字电路,其中包括了组合逻辑电路和时序电路。

它可以实现数字电子时钟功能、仿电台整点报时功能、定时功能这三项基本功能。二、设计内容及要求:① 基本功能以数字形式显示时、分、秒的时间,小时计数器的计时要求为“12翻1”,并要求能手动快校时、快校分或慢校时、慢校分。②扩展功能定时控制,其时间自定;仿广播电台正点报时—自动报正点时数。(1)数字电子计时器组成原理图1数字电子计时器的结构框图(2)用74LS160实现12进制计数器(3)校时电路C1、 C2用于消除抖动。图3 校时电路4、时基电路图4 由555定时器构成的多谐振荡器6、仿电台正点报时电路仿电台正点报时电路的功能要求是:每当数字钟计时快要到正点时发出声响,通常按照4低音1高音的顺序发出声响,以最后一声高音结束的时刻为正点时刻。设4声低音(约500Hz)分别发生在59分51秒、53秒、55秒及57秒,最后一声高音(约1kHz)发生在59分59秒,它们的持续时间为1秒。根据以上设定可得到电台正点报时时的分十位状态Q2M2Q0M2 11(0101),分个位的状态为Q3M1Q0M1 11(1001),秒十位状态为Q2S2Q0S2 11(0101),秒个位的状态为Q0S1 1(1、3、5、7、9)。

而发低音还是高音只与秒个位有关,根据设定可列表如表1所示:由表中的状态可总结出如下结论:秒个位的第三位Q3S1可用来作为鸣低音或高音的控制信号,即Q3s1 0时,输入500Hz的低频信号至音响电路Q3S1 1时,输入1kHz的高频信号至音响电路。表1 正点报时状态功能表CP(秒) Q3S1 Q2S1 Q1S1 Q0S1 功能 CP 秒 Q3S1 Q2S1 Q1S1 Q0S1 功能 50 0 0 0 0 56 0 1 1 0 停 51 0 0 0 1 鸣低音 57 0 1 1 1 鸣低音 52 0 0 1 0 停 58 1 0 0 0 停 53 0 0 1 1 鸣低音 59 1 0 0 1 鸣高音 54 0 1 0 0 停 00 0 0 0 0 停 55 0 1 0 1 鸣低音 三、单元电路的设计:1、基于NE555的秒方波发生器的设计用NE555芯片以及电路搭建成一个多谐振荡器,通过设计电路的参数输出方波频率为1Hz,故称为秒方波发生器。由于脉冲的占空比对系统的影响不大,故把占空比设计为1/3。输出方波用作计数器及D触发器的clk信号。NE555定时器引脚图如图1所示,脉冲频率公式:f 1/(R1+2R2)C㏑2选择R1 47K,R2 47K,RV1 2K,C 10μF,形成电路图如图2所示:图6图7秒脉冲发生器(2)基于74ls160的12\60进制计数器的设计A、数字钟的秒和分位都是从0到60循环计数的,所以可以用用异步清零法设计60进制计数器作为秒和分的计数器。

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/jisuanjixue/article-49803-1.html

-

-

赵亚伦

赵亚伦列黑名单

-

田野

田野以前可以搜到多个系统更新到9

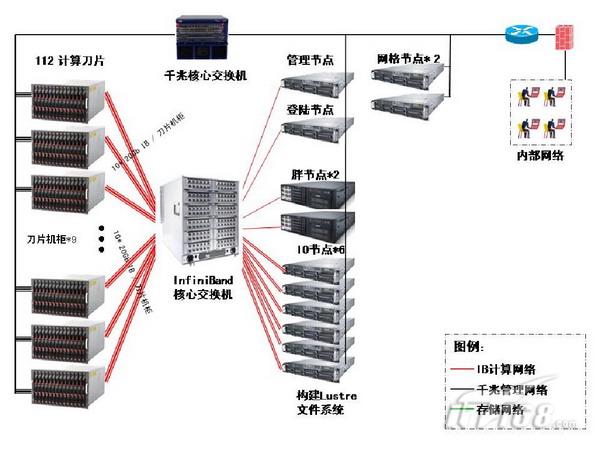

中国的超级计算机在做什么?

中国的超级计算机在做什么? 通过购买新的超级计算和高性能云计算系统,AMD EPYC处理器的部署得以扩展

通过购买新的超级计算和高性能云计算系统,AMD EPYC处理器的部署得以扩展 任天堂公司

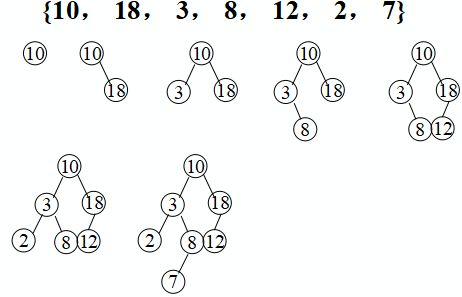

任天堂公司 第九组数据结构课程设计(二进制排序树的实现)

第九组数据结构课程设计(二进制排序树的实现)

越王苟剑