扩频时钟_时钟发生器_低频sscg架构

电脑杂谈 发布时间:2017-05-26 10:01:39 来源:网络整理

一、SSC(扩频时钟)的概念

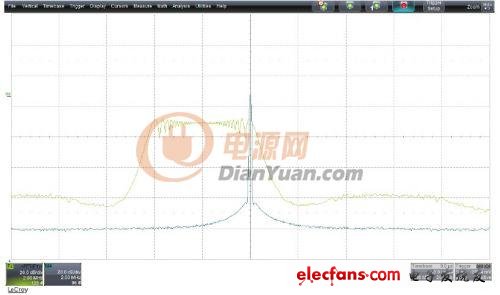

如下图1所示为一信号在是否具有SSC前后的频谱对比。图中蓝色曲线为没有SSC时候的频谱,浅色的为具有SSC时的频谱。从图中可见,未加SSC时,信号的能量非常集中,且幅度很大;而加了SSC后,信号能量被分散到一个频带范围以内,信号能量的整体幅度也有明显降低,这样信号的EMI辐射发射就将会得到非常有效的抑制。这就是通过使用SSC扩频时钟的方法抑制EMI辐射的基本原理。

使用SSC的方法能在多大程度上抑制EMI辐射和调制后信号能量在多宽频率范围内变化有关,频率变化范围越大,EMI抑制量越大。但这两者需要一个权衡,因为频率变化范围太大会使系统的时序设计带来困难。在Intel的Pentium4处理器中建议此频率变化范围要小于时钟频率的0.8%,如对于100MHZ的时钟,如果按照+/-8%来调制的话,频率的变化范围就是99.2MHZ-100.8MHZ。而对于100MHZ参考时钟的系统工作到100.8MHZ,可能会

图1 SSC扩频时钟的图示

导致处理器超出额定工作频率,带来其它系统工作问题。因此在实际系统工作中一般都采用负向调制(downspeading)以保证时序上的最小周期要求,因此图1中的具有SSC的信号能量变化范围主要集中在信号载频的左侧。当前高速串行数据中比较常用的SSC频率为30KHZ、变调深度为0.5%。扩频时钟为了保证SSC处在规定的工作范围以内,对SSC的测试是非常重要的。

二、SSC(扩频时钟)对信号的影响

SSC会导致信号的频率产生波动。如果以信号的某一个边沿为参考基准,无限的累加波形数据,则应可以观察到因频率的变化而导致的波形边沿位置的变化。如下图2所示的上侧波形为一串行数据的模拟余辉显示,从余辉图中可见,信号边沿随着时间的变化呈现不同程度的变化。图2所示的下侧波形为对上侧模拟余辉波形做水平余辉直方图的结果(F4=Phistogram(F1)),通过直方图的方法将频率的变化反应到纵轴上,可以进一步更加明显的看出信号边沿的变化情况。

图2 频率波动对信号边沿位置的影响(有SSC)

图3 频率波动对信号边沿位置的影响(无SSC)

图4频率波动对信号边沿位置的影响(有SSC)放大后的图示(时基起始点为-75ns)

图5频率波动对信号边沿位置的影响(无SSC)放大后的图示(时基起始点为-75ns)

从上图所示,带有SSC的余辉直方图逐渐呈现三角形的变化,而没有SSC时则理论上应趋于高斯分布。

三、SSC(扩频时钟)的测量

力科示波器中集成了两种常用的方法用于测量SSC。

一种是利用力科示波器中的抖动追踪(track)功能可以很方便的观察和分析信号中的SSC的频率、调制深度等参数,如下图6所示,F1为1Gbps的信号波形,F2为对F1波形频率的追踪,F3是对F2波形的滤波;另外一种是直接利用力科示波器中的SSCTrack函数分析功能,如下图6中的F5是直接用力科示波器中的函数SSCTrack功能进行SSC波形追踪的结果,此功能和对频率进行追踪的功能很类似,相当于将频率追踪、滤波的功能集成到一起,因此F5的运算对象是数据波形F1,且该功能还将信号的频率1GHZ作为一个基准,因而测量得到最大频率和最小频率分别为467.8KHZ和-4.5058MHZ(用第一种的Track功能测得的值为1.000039GHZ和995.351MHZ),调频宽度为4.9736MHZ(变调深度为0.49736%)。SSC扩频时钟的频率约为30.39KHZ。

图6 SSC扩频时钟的测试

F2和F3的参数设置:

由于SSC波形的频率比较低,约为30KHZ(周期约为33.3us),因此对采集多大的数据量进行分析有一定的要求,如测试中一屏幕采集5个SSC波形周期的话,则总的采集时间长度约为200us,如果设置示波器采样率为20GS/S,那么则需要采集至少4M(200us/50ps)的数据量。

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/tongxinshuyu/article-49336-1.html

-

-

马俊旗

马俊旗外抗美国

-

吴康

吴康和政府作对你能赢

智能电表购销合同范本_水果购销合同范本600字_购销合同范本简洁版

智能电表购销合同范本_水果购销合同范本600字_购销合同范本简洁版 山东移动4g流量卡本人亲身经历告诉你淘宝刷单真相,刷一单多少

山东移动4g流量卡本人亲身经历告诉你淘宝刷单真相,刷一单多少 mecanum轮全方位移动机器人技术以及应用 王兴松

mecanum轮全方位移动机器人技术以及应用 王兴松 no.7信令网由什么组成_7号信令网使用方法_信令网

no.7信令网由什么组成_7号信令网使用方法_信令网

可能不合格么