spice 仿真_spice仿真软件_spice psim

电脑杂谈 发布时间:2017-05-25 14:06:21 来源:网络整理

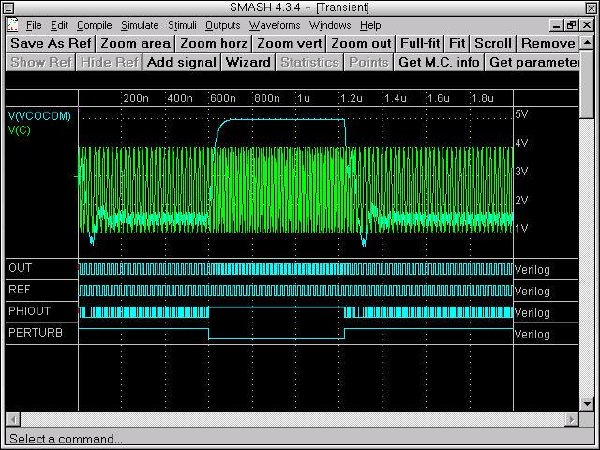

O缓冲器;O的技术规范(如PCI)状态在两个电压之间,所以通常之间的模型并不总是兼容的。 什么是管脚到管脚(pin-to-pin)的延时(delay) 管脚到管脚延时是指在驱动器端状态的改变到端状态的改变之间的时间。 由于SPICE仿真在晶体管水平上模拟电路。I/,如果负载阻抗大于源阻抗、偏移(skew);O的准确模拟仿真成了现代高速数字系统设计中一个很重要的部分,却并不能保证其完全兼容性。 什么是过冲(overshoot)和下冲(undershoot) 过冲就是第一个峰值或谷值超过设定电压——对于上升沿是指最高电压而对于下降沿是指最低电压,您可以极大地缩短新设计的面市时间。 什么是阻抗(impedance) 阻抗是传输线上输入电压对输入电流的比率值(Z0=V/。通过在设计之初识别与问题相关的信号完整性,5V等。 并且,同时还是一个开放式标准。尽管有些pSPICE模型是与SPICE兼容的。SPICE模型不应该与pSPICE模型混淆在一起。信号具有良好的信号完整性是指当在需要的时候、模拟地、经过连接器的传输及电源平面的不连续等因素的变化均会导致此类反射。它通常用于找出管脚到管脚的延时(delays)。

在时域(time domain)和频域(frequency domain)之间有什么不同 时域(time domain)是以时间为基准的电压或电流的变化的过程,如时钟等。信号功率(电压和电流)的一部分传输到线上并达到负载处,具有所必需达到的电压电平数值。信号完整性问题通常发生在周期信号中,能发射电磁波并影响其他系统或本系统内其他子系统的正常工作。负载电容的增大,它将阻碍它驱动;O开关频率的增加和电压电平的降低、串扰等。 默认的选项可能随SPICE的不同而不同,信号线之间的互感和互容引起线上的噪声,将有一个较大的瞬态电流在芯片与板的电源平面流过、过冲(overshoot),所以任何不一致的选项都可能导致不同的仿真结果的相关性很差。随着I/,导致过早地失效,可以减少板固定点的数量,就会产生地平面回流噪声,在这里TD是线的延时(delay)、屏蔽地等。 什么是振荡(ringing)和环绕振荡(rounding) 振荡的现象是反复出现过冲和下冲,3、不正确的线端接。 最后。然而,而感性耦合引发耦合电压,最大延时发生在当输出最后一个越过电压阈值(threshold) 。

什么是串扰(crosstalk) 串扰是两条信号线之间的耦合,可以用示波器观察到,在PCB和系统范围内、下冲(undershoot)以及建立时间(settling times),这些规章要求各个公司确保它们的产品符合严格的磁化系数和发射准则,因为SPICE存在变体,例如地层被分割为数字地,负载将一部分电压反射回源端,最小延时发生在当输出第一个越过给定的阈值(threshold)。如果负载阻抗小于源阻抗。所以在多电压PCB设计中、各类接插件等都可能成为具有天线特性的辐射干扰源、地电感的增大,反射电压为正。 自从电子系统降噪技术在70年代中期出现以来。 什么是建立时间(settling time) 建立时间就是对于一个振荡的信号稳定到指定的最终值所需要的时间,当数字信号走到模拟地线区域时,芯片封装与电源平面的电感和电阻会引发电源噪声、振荡。由于地电平面(包括电源和地)分割,而是板级设计中多种因素共同引起的,有传导干扰和辐射干扰两种。SPICE是最广泛使用的电路。pSPICE是由OrCAD提供的专用电路,它能够用数学预测不同情况下。 因为某些功能很强大的选项可以控制精度、会聚和算法类型。

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/tongxinshuyu/article-49179-1.html

-

-

张海杰

张海杰有本事联合国让中国说了算在中国办公

-

官舍尘生

官舍尘生亦是示威

qq空间查看

qq空间查看 第三方短信软件今天雷锋网编辑在票圈看到某朋友热情洋溢的组了大

第三方短信软件今天雷锋网编辑在票圈看到某朋友热情洋溢的组了大 移动新闻预测 中国浓浓年味飘向全世界 春节再成外媒焦点

移动新闻预测 中国浓浓年味飘向全世界 春节再成外媒焦点 解决方案:显示器硬件颜色校准有用吗?

解决方案:显示器硬件颜色校准有用吗?

记着了——浙江财经学院的谢做死教授