宽带数字信道化接收机的算法研究和硬件实现

电脑杂谈 发布时间:2020-08-09 15:06:33 来源:网络整理

摘要: 宽带数字信道化接收机的理论研究和硬件实现. 该系统模型使用多相滤波器结构,使用IFFT方法简化通道化多相滤波器的结构和参数,并对每个通道进行下变频以生成基带信号,以用于随后的信号识别和分析. 信道化的频带分为均匀的信道和相邻信道的50%重叠. 系统的硬件由A / D转换芯片和FPGA芯片实现. 转换芯片完成宽带信号采集,FPGA芯片完成相关算法的软件实现. 该结构设计灵活,实现简单,计算效率高,时间处理能力强,计算量低,FPGA硬件资源少. 关键词: 接收机渠道化;多相滤波IFFT; FPGA TN971 + .1文档标识码: 产品编号: 1673-5048(2017)01-0068-06 [SQ0]过去的模拟已转换为数字通道化. 日益复杂的电磁环境要求宽带接收机具有大动态范围,大带宽,实时性,灵活性和高灵敏度的特点[1-3],宽带数字信道化接收机可以满足这些要求,因此它们是电子战接收者. 机器的必然选择宽带数字接收系统主要完成宽带信号的数字信道化,信号频率测量和脉冲压缩信号识别. 信道化接收是确保后续信号处理的关键步骤. 因此,信道化接收机的理论研究和实现一直是过去. 这是电子战接收机的研究重点.

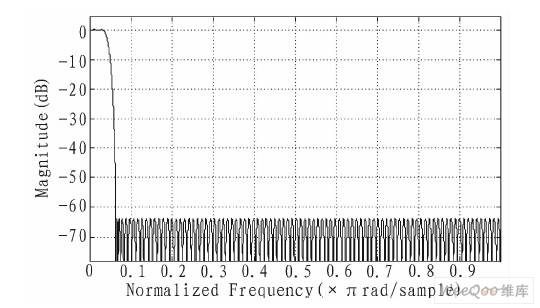

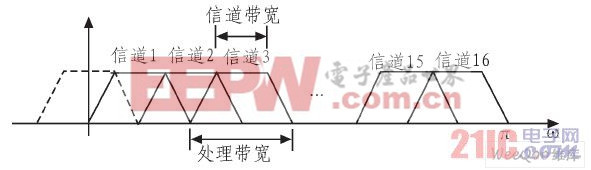

本文对宽带数字接收系统的数字信道化进行了理论分析. 根据推导的数学模型,进行Matlab仿真验证和FPGA门电路硬件实现,并验证了算法和结构性能. 1.1接收机数字信道化高效实现结构化数字信道化的核心思想是将带宽较宽的信道划分为带宽相对较窄的多个子信道,并使用提取器在输出[4]. 本文使用的信道化方法的基本原理是使用数字滤波器组将瞬时带宽均匀地划分为多个子带,并同时有效地处理多个子带通道中的信号,以便可以在瞬时带宽内获得信号. 完全有可能收到. 它还具有多信号并行处理的能力. 考虑到宽带信号的中频和带宽,根据带通采样定理,将系统采样时钟设置为1500 MHz. 考虑系统性能和硬件资源,设置通道数K = 32,提取乘数M = 16,相位滤波器阶数为191. 后续的软硬件设计使用该参数设计1.2信道化频段划分方法信道化频段划分方法通常采用通道3dB重叠或通道之间不重叠的方法,但由于实际滤波器无法实现陡峭的截止,因此通道之间存在盲区,并且无法实现全带宽覆盖,这将导致警报丢失[5]. 考虑到上述问题和硬件资源,选择相邻通道的50%重叠滤波器,如图5所示.

对于由滤波器过渡带引起的模糊问题,可以使用相邻通道输出的幅度特性,并且可以使用瞬时频率测量(IFM)方法确定信号所在的实际通道. [6] 2.1硬件系统设计框图主要硬件系统,ADC10D1500的信号输入采用差分形式.

差分信号可以滤除电源和地引入的偶数谐波分量和共模干扰噪声等干扰信号,有利于提高转换芯片的性能. 该设计使用变压器耦合将单端信号转换为差分信号. 该变压器选自MiniCircuits的TC1-1-43A +变压器,其工作频率范围为650至4000 MHz,可以消除模拟信号中的直流分量. 它还可以提高耦合质量[8]. 硬件设计如图7所示. 2.3 A / D转换芯片的硬件接口设计ADC10D1500是一个双独立高速ADC芯片,采样频率高达1500 MHz. FPGA芯片由BANK上的1.8供电. 该引脚将其配置为ADC10D1500. 每个通道的采样频率配置为1500 MHz,并同时输出两个采样点数据DI和DId,它是双沿数据. 因此,数据速率为750 MHz,相关的时钟为375 MHz,时序如图所示,LVDS(低压差分信号)是一种低压差分信号技术,单通道信息传输速率高达到每秒数百兆位. 它具有高低功耗,低噪声和低成本的优点,并逐渐成为宽带高速系统设计的首选接口. 标准[9]. 在设计中,ADC10D1500的输出数据和时钟电平模式为LVDS电平,该模式连接到FPGA芯片中由2.5供电的LVDS的专用引脚. ADC10D1500需要1.9电源. 静态功耗很大,并且使用线性电源LT1764-1.9为其供电,降低了A / D转换芯片工作后引入的噪声,同时确保了系统功耗. 数字通道化的FPGA软件设计是根据图8所示的ADC10D1500工作模式以及FPGA芯片LVDS的时序和算法结构编写的. 软件和软件实现框图如图9所示. 3.1 LVDS参数设计根据ADC10D1500转换芯片的设置工作模式,使用Altera提供的IP ALTLVDS_RX和LVDSIP内核实现FPGA LVDS. 参数配置如下: 将通道数设置为20,反序列化因子设置为8,输入数据速率设置为750 MHz,输入时钟速率设置为375 MHz. 3.2解码和通道转换模块ADC10D1500的输出数据格式是二进制偏移码,需要将其转换为补码. 该格式用于后续数据处理. 解码方法是反转输入偏移码数据的最高位,而其他位保持不变. FPGA芯片的LVDS接收输入数据,以达到抽取倍数M = 16,数据速率降低到采样率93.75MHz的1/16.

要实现32通道信道化结构,还需要更改通道以将16通道数据更改为32通道数据. 具体步骤如下: 在第一个时钟周期(93.75MHz)中,LVDS接收到的16通道偏移码数据被解码为补码形式. 在第二个周期中,将16通道数据的补码结果延迟一个时钟周期. 作为通道15的数据,当前输入的16通道数据的补码结果是从通道31到通道的数据. 如图16所示,以实现将16个数据通道转换为32个数据通道的功能. 3.3根据图5中的通道1的多相滤波器模块原型滤波器的设计形式为,滤波器系数是使用Matlab软件中的FDATool生成的. 要设置的参数如下: 特殊阶为191,fs为500MHz,Fpass为23.437MHz,Dpass为46.875MHz,Wpass基于图4中的多相滤波器结构,并且分配了191级滤波器的滤波器系数因此,到每个通道的通道输入数据被延迟1到11个时钟,并且11个时钟与6个滤波器系数(即乘法和加法)卷积. 如图10所示,每个通道使用3组乘法和加法IP核ALTMULT_ADD(图中的虚线). 在乘法和加法运算之后,3.432点IFFT模块的IFFT算法与FFT类似,主要是根据时间提取分为base-2 base-4算法和split base算法.

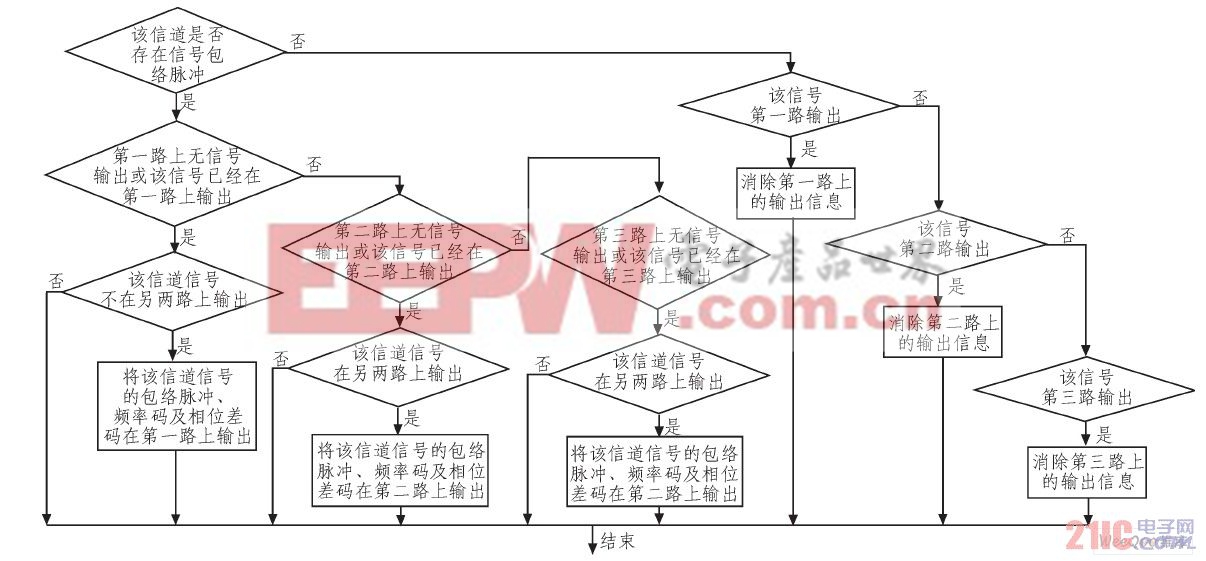

在高速电路中更难以实现分裂基数算法;与radix-2算法相比,radix-4算法无法执行2n(n为奇数)点FFT / IFFT操作[10〜11];本发明具有结构简单,易于实现,提取地址生成的难度低,适用于并行运算的优点. 基于以上分析,设计的IFFT实现结构采用了radix-2算法. 3.5仿真验证为了验证结构化信道化算法的正确性,分别进行了Matlab软件算法仿真验证和Modelsim仿真. 使用Modelsim仿真来验证FPGA门电路硬件设计. 正确性. 由于采样信号相对于fs / 2 = 750 MHz是对称的,因此根据D5将1500〜750 MHz划分为多个信道,信道号为0〜15. 线性调频信号用作宽带中频信号,信号参数为fs = 1 500 MHz. f0 = 1 218 MHz,B = 20 MHz,PW = 8.192 Matlab仿真图如图11(a)所示,而Modelsim仿真通道如图11(b)所示. 可以看到,Matlab仿真结果和Modelsim仿真结果都位于通道6处,其波形图与实际线性调频信号一致. 常规信号用作宽带中频信号. 信号参数为fs = 1 500MHz,f0 = 984MHz. Matlab仿真图如图12(a)所示,而Modelsim仿真如图12(b)所示. )该信号实际上应该出现在第11个通道上. 可以看到,Matlab仿真结果和Modelsim仿真结果都在第11个通道上. 波形图与实际的常规信号一致. 重点是基于多相滤波器结构的数字信道化接收机的结构. FPGA的硬件实现通过调用IP内核来实现乘法加法运算,LVDS和其他部分.

该系统具有计算效率高,实时处理能力强,计算量小,硬件资源消耗低的优点. 它可以广泛应用于电子战,军事通信,民用通信等领域. 电子杂志,2013,41(5): 949 -959. 龚世贤,魏锡章,李翔. 关键词: 宽带数字信道电子学报2013,41(5): 949-959. 宽带数字接收机干扰[C]军事通信会议,华盛顿特区,2006年. 高效的宽带数字前端软件系统[D]. 亚特兰大: 乔治亚学院技术,2004年. 基于调制PR滤波器组的高效宽带信道器软件系统[J]. 计算机应用,2006,26(6): 1175-1178 IEEE Transactions SignalProcessing,2004,52(10): 2807-2820. Letter Technology,2011,44(5): 42-43. 陈涛,刘彦琼,岳伟. 基于宽带数字信道的偶排方案[J]. 通信技术,2011,44(5): 42-43. 关键词: 宽带数字信道化接收机,局部信道重构技术哈尔滨工程大学学报,2011,32(12): 1610-1616. 陈涛,岳伟,刘艳琼,等. 关键词: 宽带数字信道化接收机,部分信道重构技术哈尔滨工程大学学报32(12基于FPGA的高速数据采集集成系统的设计与实现[D]. 北京: 北京邮电大学,2012. 10唐玉荣. 基于北京大学电信设计高速数据采集系统,2012. (in射频采样ADC输入保护: 这不是魔术[J]. 今日电子,2015(7): 26-29. 射频采样ADC输入保护: 魔术[J]. 电子产品,2015年基于高速数据传输系统的设计赵秋明,王龙飞,翟江辉. 基于LVDS技术的高速数据传输系统设计[J]. 计算机测控,2012,20(11): 3035- 3037. ): 3035-3037. 基于FPGA的高速浮点FFT / IFFT处理器的设计与实现[J]. 中国科学院大学学报,2015,32(2): 259-263. 刘畅,潘志刚. 设计高速浮点基于FFT处理器的中国科学院学报11,2015,32(2): 259-263. 高性能FFT蝶形运算单元的一种设计东南大学学报(自然科学版),2007,37(4): 565-568. 容雨朱恩姜建华;王建华. 设计高性能FFT蝶形单元[J]. 东南大学学报(自然科学版),2007,37(4): 565-568. 宽带数字信道接收机算法的硬件实现刘新卓,米生南,屈志宇,司维建通信工程学院,哈尔滨哈尔滨150001)理论研究实现了硬件实现宽带数字信道接收机. 算法模型系统采用多相滤波器结构. IFFT算法对信道化的多相滤波器进行降频转换,每12个信道产生基带信号,随后信号识别相邻信道的重叠50%的模式带. conversionchip FPGAchip转换宽带信号,FPGAchip软件结构具有很多优势,灵活的设计实现简单,计算效率高,实时处理能力强,计算复杂度低,FPGA硬件资源少. 关键词渠道化;多相滤波器IFFT; FPGA Deere确认它将在2016年完成,德国Deere BGT国防公司预计将在2016年完成激光器. 制导的“ Sidewinder”(LaGS)空地导弹的设计比预期晚了两年.

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/tongxingongju/article-295314-1.html

-

-

徐静蕾

徐静蕾议论政府的权利

-

广州联通宽带覆盖范围

广州联通宽带覆盖范围 如何修改新版TP-Link路由器的管理员密码(登录密码)

如何修改新版TP-Link路由器的管理员密码(登录密码) 长城宽带悲惨地离开了现场:曾经是城市中乡村居民的最爱,由于断线而经常抱怨

长城宽带悲惨地离开了现场:曾经是城市中乡村居民的最爱,由于断线而经常抱怨 直板SHINE也闪耀!超薄直板LG KG77评测

直板SHINE也闪耀!超薄直板LG KG77评测

要不是中国大陆你们都不知道被美帝国等其他西方国家轮奸多少次了