宽带数字信道化

电脑杂谈 发布时间:2020-08-09 15:05:42 来源:网络整理

在《雷达系统组成原理》一文中,我们介绍了一种典型的雷达系统,包括天线,和处理器. 在传统的雷达信号处理设备中,接收机的输出直接由处理器收集. 当信号带宽足够大时,后端数字处理设备的数据速率将无法跟上. 例如,对于带宽为2GHz的信号,在以4GHz的采样率进行采样后,以16bitADC为例,至少需要8GB / s的数据处理速度,而典型的FPGA时钟只有几个最多一百兆. 为了处理宽带信号,必须提取信号.

但是根据信号提取的原理,我们知道提取信号后,其频谱在频域中将是周期性的,这将引起频率混叠的问题. 一种解决方案是,我们首先将原始信号的带宽划分为多个子带,例如,将带宽B每B / k划分为一个子带,然后使用滤波器过滤掉每个子带. 此时,我们可以提取每个子带.

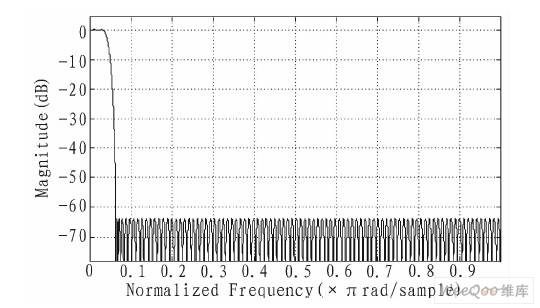

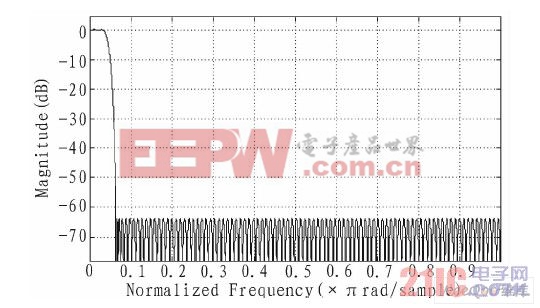

这样做的一个缺点是滤波器仍然以较高的采样率工作,因此滤波器系数更大,并且在实际实现中浪费了很多乘法运算. 为了解决这个问题,首先考虑一个FIR滤波器,其单位采样响应为h(n),其Z变换H(Z)为

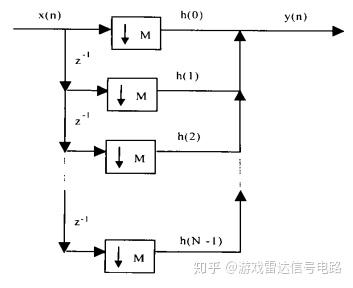

. 图1显示了抽取前滤波的处理框图

图1过滤和处理系统的框图

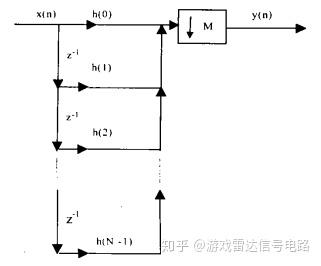

对于图1中的系统框图,我们可以进行如图2所示的等效转换.

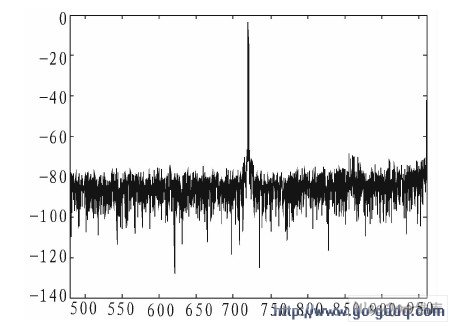

使用图2中的结构时,仅需要图1中乘法数的1 / M. 当M = 20时,所需的滤波器从一个80阶滤波器变为20个四阶滤波器. 因此,通过滤波器的多相分解(此处省略公式推导),我们等效地将传统数字下变频的结构转换为抽取和滤波的形式. 此步骤也称为多相滤波. 之后,将每个分支的分量下变频到基频以进行后续处理.

此处应注意,当每个分支的调谐频率的周期N等于多相滤波器的抽取因子M时,下变频系数

可以一一对应地将其分配给多相滤波器的每个分支. 此时,我们可以通过选择适当的旋转因子并通过FFT计算来实现此步骤. 因此,一个完整的数字信道化接收机通常包含两部分: 多相滤波和FFT操作.

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/tongxingongju/article-295310-1.html

-

-

王康

王康没办法

-

-

尚雪姣

尚雪姣管股票的人肯定可以发财

广州联通宽带覆盖范围

广州联通宽带覆盖范围 如何修改新版TP-Link路由器的管理员密码(登录密码)

如何修改新版TP-Link路由器的管理员密码(登录密码) 长城宽带悲惨地离开了现场:曾经是城市中乡村居民的最爱,由于断线而经常抱怨

长城宽带悲惨地离开了现场:曾经是城市中乡村居民的最爱,由于断线而经常抱怨 直板SHINE也闪耀!超薄直板LG KG77评测

直板SHINE也闪耀!超薄直板LG KG77评测

怎么知道发布新闻的机构是真的质检总局