笔记本电脑处理器选择 CPU/MCU/FPGA/SoC 这些芯片究竟是啥?(5)

电脑杂谈 发布时间:2018-02-12 03:55:54 来源:网络整理硬件描述语言HDL的发展至今已有30多年的历史,其成功地应用于设计的各个阶段:建模、仿真、验证和综合等。到20世纪80年代,已出现了上百种硬件描述语言,对设计自动化曾起到了极大的促进和推动作用。但是,这些语言一般各自面向特定的设计领域和层次,而且众多的语言使用户无所适从。因此,需要一种面向设计的多领域、多层次并得到普遍认同的标准硬件描述语言。20世纪80年代后期至90年代,VHDL和Verilog HDL语言适应了这种趋势的要求,先后成为电气和电子工程师协会(Institute of Electrical & Electronics Engineers, IEEE)标准。

现在,随着超FPGA以及包含SoC内核FPGA芯片的出现,软硬件协调设计和系统设计变得越来越重要。传统意义上的硬件设计越来越倾向于与系统设计和软件设计结合。硬件描述语言为适应新的情况,迅速发展,出现了很多新的硬件描述语言,像System Verilog,SystemC、Cynlib C++等;另一方面,PLD设计工具在原先仅支持硬件描述语言设计输入的基础上,日益增加对传统高级设计语言(如C/C++)的设计支持。

目前,硬件描述语言可谓是百花齐放,有VHDL、Verilog HDL、Superlog、SystemC、System Verilog、Cynlib C++、C Level等。整体而言,在PLD开发领域应用最广的还是VHDL和Verilog HDL。随着逻辑系统开发规模的不断增大,SystemC和System Verilog等系统级硬件描述语言也得到越来越多的应用。

VHDL

早在1980年,因为美国军事工业需要描述电子系统的方法,美国国防部开始进行VHDL的开发。1987年,IEEE将VHDL制定为标准。参考手册为IEEE VHDL语言参考手册标准草案1076/B版,于1987年批准,称为IEEE 1076-1987。然而,起初VHDL只是作为系统规范的一个标准,而不是为设计而制定的。第二个版本是在1993年制定的,称为VHDL-93,增加了一些新的命令和属性。

虽然有“VHDL是一个4亿美元的错误”这样的说法,但VHDL毕竟是1995年以前唯一制定为标准的硬件描述语言,这是它不争的事实和优势;但同时它的使用确实比较麻烦,而且其综合库至今也没有标准化,不具有晶体管开关级模拟设计的描述能力。目前来说,对于特大型的系统级逻辑电路设计,VHDL是较为合适的。

实质上,在底层的VHDL设计环境是由Verilog HDL描述的器件库支持的,因此,它们之间的互操作性十分重要。目前,Verilog和VHDL的两个国际组织OVI(Open Verilog International)、VI正在筹划这一工作,准备成立专门的工作组来协调VHDL和Verilog HDL语言的互操作性。OVI也支持不需要翻译,由VHDL到Verilog的自由表达。

Verilog HDL

Verilog HDL是在1983年,由GDA(Gateway Design AUTOMATION)公司的Phil Moorby首创的。Phil Moorby后来成为Verilog-XL的主要设计者和Cadence公司的第一合伙人。在1984-1985年,Phil Moorby设计出了第一个名为Verilog-XL的;1986年,他对Verilog HDL的发展又作出了另一个巨大的贡献:提出了用于快速门级仿真的XL算法。

随着Verilog-XL算法的成功,Verilog HDL语言得到迅速发展。1989年,Cadence公司收购了GDA公司,Verilog HDL语言成为Cadence公司的私有财产。1990年,Cadence公司决定公开Verilog HDL语言,于是成立了OVI组织,负责促进Verilog HDL语言的发展。基于Verilog HDL的优越性,IEEE于1995年制定了Verilog HDL的IEEE标准,即Verilog HDL 1364-1995;2001年发布了Verilog HDL 1364—2001标准,在这个标准中,加入了Verilog HDL - A标准,使Verilog HDL有了模拟设计描述的能力

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/shumachanpin/article-72906-5.html

-

-

大山真志

大山真志美国没有预料到的是

-

幼主高恒

幼主高恒雷达探测精度和灵敏度

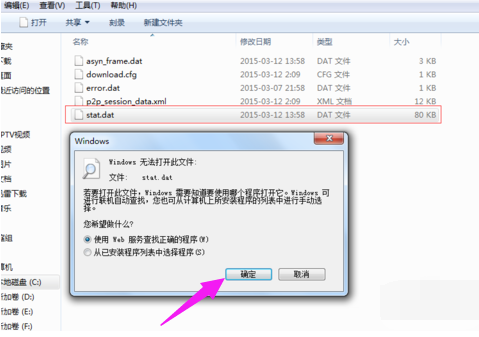

dat格式用什么播放器打开_dat格式怎么关掉 mac_手机dat格式怎么打开

dat格式用什么播放器打开_dat格式怎么关掉 mac_手机dat格式怎么打开 档案图书 江苏大学图书馆空调管路改造工程的招标公告

档案图书 江苏大学图书馆空调管路改造工程的招标公告 畅谈12辆索伦托旧车体验+后视镜导航体验

畅谈12辆索伦托旧车体验+后视镜导航体验 比较三个最热门的运动相机之后,我必须

比较三个最热门的运动相机之后,我必须

这样不好吧