gps授时_刀鎺_鎺字怎么念(2)

电脑杂谈 发布时间:2016-12-28 06:01:11 来源:网络整理GPS信息采集器设计

GPRMC数据所采用的是ASCII码,所以在这个模块中不仅要将时间信号提取出,还要将对应的数据转换成BCD码。接收数据中的状态如图3所示,初始状态为状态0,当接收到$时转向状态1,否则不断循环等待,状态1、2、3、4、5、6分别表示接收到数据位G、P、R、M、C和“,”,如未接收到则转向状态0从新开始,状态7提取出时分秒信息的ASCII码,当提取完后转向状态8用来等待7个“,”,因为这些数据流不需要,当等到第7个“,”时转向状态9,提取出年月日,提取完以后结束转向状态0等待下一个码流的到来。

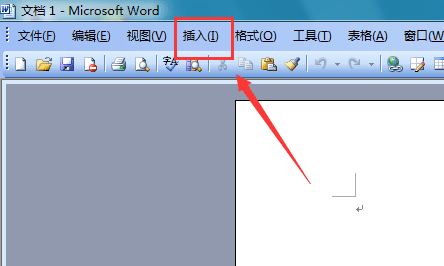

图 4 转换模块RTL视图

时间信息转换设计

在GPS时间采集器中所提取的时间虽然已由ASCII码转变成BCD码,但是GPRMC中所包含的时间比北京时间晚了8个小时,所以在这个模块中要将GPS时间转换成北京时间。由于IRIG-B码中所需要的信息除了时hour[5..0]、分min[6..0]、秒sec[6..0],还有天day[9..0],而采集到的时间是年gps_year[7..0]、月gps_mouth[7..0]、日gps_day[7..0]、时gps_hour[7..0]、分gps_min[7..0]、秒gps_sec[7..0],所以在这个模块中也要将年月日转变成相应的天数,还要特别注意的问题就是对于闰年与非闰年的判断,最后产生的四个时间信息为精准的BCD码,便于下面设计,其RTL视图如图4所示。

IRIG-B(DC)码编码器设计

前面几个模块中已将所需的时间提取出来了,这个模块就是把这些时间转换成DC码。通过对B码的编码原理的理解,使用10MHz的时钟进行设计,由于每个码元需要100000个时钟,故当为“1”时需要计数器计数高电平50000个,低电平50000个;当为“0”时需要计数器计数高电平20000个,低电平80000个。为了使GPS模块的pps与DC码的秒头一致,所以在检测到pps上升沿的时候就开始使得计数器开始计数,FPGA对编码仿真如图5所示。

图6 当前时间的数码管显示以及实验箱的解码显示

图中clk为10MHz的时钟,pps为输入信号,是由GPS产生的,day[9:0]为天数,hour[5:0]、min[6:0]、sec[6:0]分别为时、分、秒。通过仿真波形可以看出通过FPGA设计的编码器精确度很高,1pps与输出的B码PR(位置识别标志)相差的延时为100ns,可忽略不计。当1pps上升沿到来时,就开始状态机的启动,在最后一个状态的时候,也就是计数器计数P0时,会留下最后1ms转到状态开始用于等待1pps上升沿的到来,从而达到精确的效果。gps授时

硬件实现

通过FPGA将整体模块整合后,调整GPS,将1pps信号和码流分别接在电路的外接端口和UART的接收端口,最后将生成的.sof文件烧入FPGA中,用数码管显示当前北京时间,如图6所示。现在时间是2012年8月28日9点21分。数码管显示后面六位为时分秒,高两位为天数的后两位,2012年是闰年,8月的今天应该是241天,刚好显示的也是41。将含有当前时间信息的DC码输出,由于IRIG-B码解码箱需要的是差分信号,所以需要将DC码通过RS485芯片从而产生差分的DC,然后接入实验箱调到解码模式DF,从而得到当前解码时间和数码管显示时间一致。

结论

本设计介绍了一种通过FPGA设计出GPS授时的IRIG-B(DC)码的研究方法,并在硬件中得以实现,对于具有8256个LE的FPGA才使用了23%,所占用的资源比较少,精度高。而且所得到的同步时钟中1pps的秒头和DC码的秒头相差控制在ns级,比较准确,输出结果也比较稳定,易于监测且实用性较高。

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/shumachanpin/article-23660-2.html

-

-

王肖飞

王肖飞你收家里

Microsoft拼音输入法3. 0正式版

Microsoft拼音输入法3. 0正式版 手机充电器一体锂电池是应用越来越广泛的一种储能转换装置,因为

手机充电器一体锂电池是应用越来越广泛的一种储能转换装置,因为 GPS的原理和应用-

GPS的原理和应用- word中间一点怎么打·软键盘特殊符号问题详解

word中间一点怎么打·软键盘特殊符号问题详解

不一个档次