CPU组成计算机的工作过程是计算机执行程序的过程。

电脑杂谈 发布时间:2021-06-07 05:03:36 来源:网络整理CPU 构成

计算机的工作过程是计算机执行程序的过程。程序是一个指令序列,它清楚地告诉计算机应该执行什么操作以及在哪里可以找到用于该操作的数据。

一旦程序加载到主存中,计算机就可以自动执行取指令和执行指令的任务。专用于此任务的计算机组件称为中央处理单元(CPU),而制成单片集成电路的 CPU 通常称为微处理器(Microprocessor)。图 3-1 显示了采用陶瓷 PGA 封装的 Intel 80486 DX2 CPU。

(a) 俯视图

(b) 底视图

图 3-1 陶瓷 PGA 封装的 Intel 80486 DX2 CPU

计算机行业从 1960 年代初开始使用 CPU 一词。到目前为止,CPU在形式、设计和实现上都发生了巨大的变化,但其基本工作原理并没有发生显着变化。

早期的 CPU 通常是为大型特定应用程序定制的。目前,这种为特定应用设计定制 CPU 的昂贵方法已在很大程度上让位于可批量生产的通用处理器的开发。这种标准化趋势大致始于分立晶体管大型机和小型机时代,并随着集成电路(IC)的普及而大大加速。集成电路可以在很小的空间内设计和制造越来越复杂的 CPU。 CPU的小型化和标准化,大大增加了这些数码设备在现代生活中的应用范围,远远超出了专用计算机的有限应用。现代微处理器已经无处不在,从汽车到手机,甚至儿童玩具。

3.1 CPU 功能及组成

3.1.1 指挥系统开发

指令是计算机硬件可以识别并直接执行操作的命令。计算机中所有指令的集合构成了计算机的指令系统。指令系统是表征计算机性能的重要因素。其格式和功能不仅直接影响机器的硬件结构,还直接影响机器的系统软件和适用范围。因此,设计一套合理有效、功能齐全、通用性强、内容丰富的指挥系统显得尤为重要。

从计算机的层次结构来看,计算机指令分为三类:微指令、机器指令和宏指令。微指令是微程序级的指令,属于硬件;宏指令是由若干条机器指令组成的软件指令,属于软件;机器指令,也就是我们通常所说的指令,介于微指令和宏指令之间。每条指令可以完成一个独立的算术运算或逻辑运算。

回顾计算机的发展历史,指令系统的发展经历了从简单到复杂的演变。早在 1950 年代和 1960 年代,大多数计算机都是由晶体管或电子管的分立元件组成,体积庞大且价格昂贵。因此,计算机的硬件结构比较简单,支持的指令系统只有十几个到几十个。基本指令,和简单的寻址方式。到1960年代中期,随着集成电路的出现,计算机的功耗、体积和价格不断下降,硬件功能不断增加,指令系统越来越丰富。 1960年代后期,一系列计算机开始出现,即具有相同基本指令系统和相同基本架构的一系列计算机。

1970年代,高级语言成为大、中、小型机的主要编程语言,计算机应用日益流行。计算机设计者利用成熟的微程序技术和飞速发展的超集成电路技术,加入各种复杂的、高级的面向语言的指令,使指令系统越来越大。按照这种方法设计的计算机系统称为复杂指令集计算机(Complex Instruction Set Computer),简称CISC。如此庞大的指令系统,不仅使计算机开发周期变长,正确性难以保证,调试维护困难,而且大量复杂指令使用频率低,造成硬件资源浪费。为此,人们提出了精简指令集计算机(RISC),它便于VLSI技术的实现。它是计算机体系结构的一种设计思想,是现代计算机体系结构发展史上的一个里程碑。 1990 年代初期,IEEE 的 Michael Slater 对 RISC 的定义是这样描述的:RISC 处理器设计的指令系统应该能够有效地执行流水线处理,并使优化编译器能够生成优化代码。

3.1.2 命令系统性能要求

指令系统的性能决定了计算机的基本功能。它的设计是计算机系统设计的核心问题。它不仅与计算机的硬件结构有关,也与用户的需求有关。一个完整的指挥系统应该满足以下四个要求:

1.完整性

指令系统的完备性是指当各种程序用汇编语言编写时,指令系统直接提供的指令就足够使用了,无需借助软件来实现。计算机中最基本、不可或缺的指令构成了指令系统的完整性。其他一些指令可以通过基本指令或直接通过硬件来实现。两者只是执行时间和编程难度不同。指令系统中硬件指令的使用是为了提高程序执行速度,方便用户编写程序。

2.有效性

有效性是指用指令系统提供的指令编写的程序可以高效运行。高效率主要表现在程序占用的存储空间小,执行速度快。一般来说,一个功能齐全的指挥系统必须非常有效。

3.规律性

规律性是指指令系统的对称性和统一性,指令格式和数据格式的一致性。

指令的对称性意味着指令系统中的所有寄存器和存储单元都可以一视同仁,所有指令都可以使用各种寻址方式,这将提高程序的可读性,简化程序设计。很方便。

指令的统一性是指具有运算性质的指令可以支持多种数据类型,例如算术指令可以支持字节、字和双字整数运算、十进制数运算、单双精度浮点运算等。等待。因此,程序员无需考虑数据类型和选择指令,提高了编程效率。

指令格式与数据格式的一致性意味着指令长度与数据长度之间存在一定的关系,便于处理和访问。

4.兼容性

兼容性是指计算机的体系结构设计基本相同,计算机的基本结构、数据表示和通用的基本指令集相同,所以指令系统是兼容的,即相同的软件可以在不加修改的情况下使用在具有相同系统结构的其他机器上。目前,新推出机型的指令系统除了兼容该系列电脑的指令系统外,还包含了所有老机型的所有指令,实现了“向上兼容”,即运行在该系列计算机上的软件。低端机无需任何改装即可在高端机上使用。运行。

作为控制和执行指令的组件,CPU对整个计算机系统的运行极为重要。它不仅与计算机的其他功能部件交换信息,而且控制这些功能部件的运行。

使用电脑解决问题时,首先要编写相应的程序,并预先通过输入设备将程序和原始数据保存到主存中。计算机在工作时,依次取出指令,分析指令,执行指令,自动转移到下一条指令。计算机逐条执行指令以实现预先设计的程序控制,直到完成程序指定的任务。

3.1.3 CPU基本功能

CPU 控制整个程序的执行,它有以下基本功能:

(1)程序控制

程序控制就是控制指令的执行顺序。

程序是指令的有序集合。这些指令的顺序不能任意颠倒,必须严格按照程序指定的顺序执行。

确保计算机按一定顺序执行程序是CPU的首要任务。

(2)操作控制

操作控制就是控制指令进行操作。

一个指令的功能往往是通过几个操作信号的组合来实现的。因此,CPU管理并生成每条指令的操作信号,并将各种操作信号发送给相应的组件,从而控制这些组件按照指令的要求进行操作。

(3)时间控制

时间控制是对各种操作的时间控制的实现。

在计算机中,各种指令的操作信号和一条指令的整个执行过程都是严格定时的。只有这样,计算机才能有条不紊地工作。

(4)数据处理

数据处理是对数据进行算术和逻辑运算。

完成数据处理是CPU的基本任务。

3.1.4 CPU的基本组成

传统上,CPU 由两个主要组件组成:控制器和算术单元。

随着集成电路技术的不断发展和进步,新型CPU集成了一些原本放在CPU外部的分立功能元件,如浮点处理器、缓存等,大大提高了CPU性能指标。时间,也使得CPU的内部构成越来越复杂。

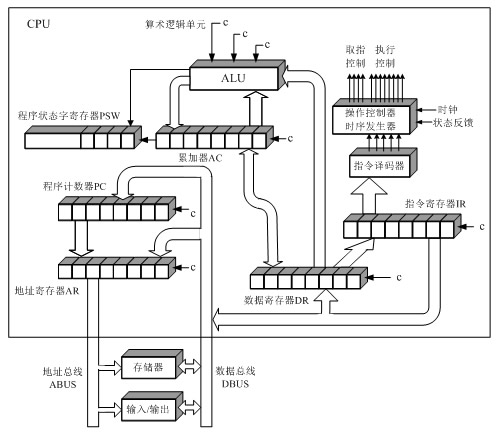

CPU主要部件的逻辑结构如图3-2所示:

图3-2 CPU主要部件逻辑

1.控制器

控制器是整个计算机系统的指挥中心。在控制器的指挥和控制下,运算器、存储器和输入/输出设备等部件协同工作,形成一个完整的通用计算机。

控制器根据程序预定的指令执行顺序访问来自主机的指令。它根据指令的功能,利用硬件产生一系列带有时序标志的微操作控制信号,以控制计算机中的各种功能。部件的运行,协调和指挥整个计算机完成指令的功能。

控制器通常由程序计数器 (PC)、指令寄存器 (IR)、指令 (ID)、时序发生器和运算控制器组成。其主要功能包括:

从主存中取出一条指令,并指出下一条指令在主存中的位置;对指令进行解码,产生相应的操作控制信号,启动指定动作;指挥和控制CPU和主存以及输入/输出设备之间数据流的方向。

2.计算器

运算单元是用于在计算机中实现数据处理和其他功能的部件。它接受来自控制器的命令,负责完成操作数据的处理任务。它的核心组件是算术逻辑单元(ALU)。

与控制器相比,运算单元接受控制器的指令并执行动作,即运算单元的所有操作都由控制器发出的控制信号指挥,因此是一个执行元件。

算术单元由算术逻辑单元(ALU)、累加寄存器(AC)、数据寄存器(DR)和程序状态字寄存器(PSW)组成。它有两个主要功能:

执行所有算术运算;执行所有逻辑操作,并执行逻辑测试。

3.1.5 CPU 中的主要寄存器

CPU中至少要有六种寄存器:指令寄存器(IR)、程序计数器(PC)、地址寄存器(AR)、数据寄存器(DR)、累加寄存器(AC)、程序状态字寄存器(PSW)。

这些寄存器用于临时存储一个计算机字,其数量可以根据需要进行扩展。

下面详细介绍这些寄存器的功能和结构。

1.数据寄存器(DR)

数据寄存器(DR)主要用作CPU与主存和外设之间信息传输的中转站,以弥补CPU与主存和外设之间运行速度的差异。

数据寄存器用于临时存放从主存读取的一条指令或一个数据字;反之,当一个数据字存入主存时,也临时存入数据寄存器中。

数据寄存器的作用是:

作为CPU与主存及外围设备之间信息传输的中转站;弥补CPU与主存和外围设备之间运行速度的差异;在单累加器结构算术单元中,数据寄存器也可以兼作操作数寄存器。

2.命令寄存器

指令寄存器(Instruction Register,IR)用于存储当前正在执行的指令。

执行一条指令时,先将指令从主存读取到数据寄存器,再传送到指令寄存器。

一条指令分为两个字段:操作码和地址码。为了执行任何给定的指令,必须测试操作码以识别所需的操作。指令(Instruction Decoder,ID)就是完成这项工作的。

指令译码器对指令寄存器中的操作码部分进行译码,产生操作控制电位,送至微操作控制电路。在时序元件的时序信号的作用下,产生具体的操作控制信号。

指令寄存器中操作码字段的输出就是指令的输入。一旦操作码被解码,它就可以向操作控制器发送特定的操作特定信号。

3.程序计数器

程序计数器(PC)用于指出主存中下一条指令的单元地址。

在程序执行之前,必须将程序的首地址,即程序的第一条指令所在的主存单元的地址发送给PC。因此,PC的内容就是从主存中取出的第一条指令的地址。

当一条指令执行时,CPU可以自动递增PC的内容,使其始终保持下一条要执行的指令的主存地址,并准备好取下一条指令。如果是单字长指令,则(PC)+1PC,如果是双字长指令,则(PC)+2PC,依此类推。

但是,当遇到分支指令时,下一条指令的地址会由分支指令的地址码字段指定,而不是像往常一样通过依次增加PC的内容来获得。

因此,程序计数器的结构应该是一个具有注册信息和计数两个功能的结构。

4.地址注册

地址寄存器(AR)用于保存CPU当前访问的主存单元的地址。

由于主存和CPU的运行速度不同,必须使用地址寄存器临时保存主存的地址信息,直到主存访问操作完成。

CPU和主存交换信息时,即CPU向主存存储/取出数据时,或者CPU从主存读取指令时,必须使用地址寄存器和数据寄存器.

同理,如果我们把外围设备的设备地址作为主存的地址单元,那么CPU和外围设备交换信息时,也需要用到地址寄存器和数据寄存器。

5.accumulation 寄存器

累加器寄存器通常简称为累加器(Accumulator,AC),是一种通用寄存器。

累加器的作用是:当算术逻辑单元(ALU)的算术逻辑单元(ALU)进行算术或逻辑运算时,它为ALU提供一个工作区,可以临时保存一个操作数或运算结果对于 ALU。

显然,算术单元中必须至少有一个累加寄存器。

6.程序状态字寄存器

程序状态字 (PSW) 用于表征当前的操作状态和程序的工作方式。

程序状态字寄存器存储由算术指令和逻辑指令运行或测试的结果建立的各种条件码的内容,如运算结果进位/借位标志(C)、运算结果溢出标志(O)、运算结果是零标志(Z),运算结果是负标志(N),运算结果符号标志(S)等。这些标志位通常由1位触发器保存。

此外,程序状态字寄存器还保存了中断、系统工作状态等信息,以便CPU和系统及时了解机器运行状态和程序运行状态。

因此,程序状态字寄存器是一个存储各种状态条件标志的寄存器。

3.1.6 操作控制器和时序发生器

1.微操作和数据路径

控制器在实现一条指令的功能时,总是将每一条指令有序地分解为一系列最基本、最简单、不可分割的操作控制动作。这是最基本的,最简单的,不能细分的操作叫做微操作。

我们通常将许多寄存器之间传输信息的路径称为数据路径,它控制着信息从哪里开始,通过哪个寄存器或多路复用器,最终传输到哪个寄存器。

在数据通路中,微操作通过自身的控制功能和相互的密切配合,使指令流、数据流等信息流按照预定的路径流动,实现指令的功能。每条指令的功能决定了微操作信号的序列和它需要的时序。

2.操作控制器

控制器的基本功能是负责指令的读出、识别和解释,并指导和协调各功能部件执行指令。

操作控制器是CPU中的一个组件,完成取指令和执行指令的整个过程。其主要功能是根据指令操作码和时序信号的要求产生各种操作控制信号,从而在各个寄存器之间正确建立数据通路,完成对指令的取指和执行的控制。

有两种操作控制器:组合逻辑控制器和微程序控制器。两者的区别在于控制信号形成部分不同,体现了不同的设计原则和方法。

根据不同的设计方法,组合逻辑控制器可以进一步细分为硬连线控制器和门阵列控制器。

3.定时信号发生器

CPU 除了操作控制器,还必须有时序信号发生器。

由于计算机的高速工作,每个动作的时机必须非常严格,不得有任何错误。时序发生器的作用是对操作控制器产生的各种控制信号进行严格的时间控制,产生各功能部件所需的时序控制信号。

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/shoujiruanjian/article-381015-1.html

- gotomycloud怎么用?gotomycloud注册?GoToMyCloud如何使用

- 凯立德2012夏季版?凯立德导航怎么升级?2016凯立德最新车载版?2012最新凯立德夏季版2921J0B下载

- youku free download?photo funia相册编辑?趣味照片合成(PhotoFunia)3.5.6去

- 8684公交数据包?8684离线版下载?8684公交下载?苏州8684公交查询

- 【灵信宝商务版客户端】灵信宝商务版客户端

- 灵信宝商务版_尽管太阳神孔蒂拉雅维拉科查是世间万物的创造

- 苹果6储存容量几乎已满?苹果4存储容量几乎已满?解决iphone“ 存储容量几乎已满”的办法

- 小雨伞下载?韩娱之幸福小雨伞女主?小雨伞法?小雨伞 v8.2.0.48 免费绿色版下载

如何查看Linux系统中的内存使用情况的命令呢?

如何查看Linux系统中的内存使用情况的命令呢?

二、具有大量的常驻程序和自动加载服务

二、具有大量的常驻程序和自动加载服务 上海证券交易所,深圳证券交易所,中小企业板,创业板等的代号是什么.

上海证券交易所,深圳证券交易所,中小企业板,创业板等的代号是什么. iPhone7 Plus的最大内存是多少,Apple 7Plus的最大容量是256G

iPhone7 Plus的最大内存是多少,Apple 7Plus的最大容量是256G

拿出切实可行的措施