英特尔揭露下一代Xeon处理器网格存取数据新途径

电脑杂谈 发布时间:2021-05-12 19:03:55 来源:网络整理英特尔不久前宣布,在使用Skylake微体系结构的新一代Xeon服务器处理器发布之后,它将不再使用E5和E7的命名方法,而是分为四个不同等级:铂金,金,银和青铜。今天的Intel It还透露,下一代Xeon处理器将在芯片设计架构中采用全新的网状互连架构,作为在CPU内核和高速缓存之间访问数据的新方法,以改善CPU访问延迟并满足需求。对于更高的内存带宽,这也是英特尔近年来对至强核心架构进行的最的重大改造。

英特尔在其官方网站上披露了这一重要信息,不仅将被其新系列英特尔至强可扩展处理器的新一代至强处理器(代号Skylake-SP)采用,甚至将成为将来开发Xeon服务器级CPU采用的新体系结构设计。

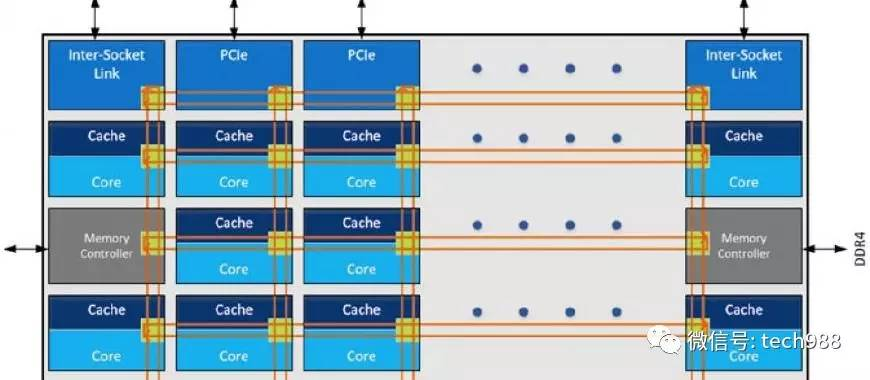

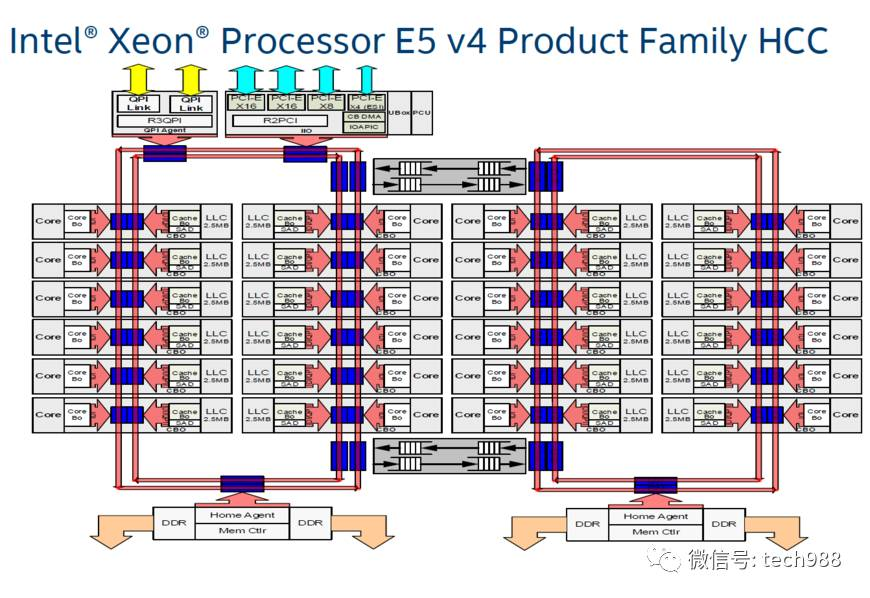

与上一代Broadwell微体系结构不同(上图显示了HCC(高核配置)版本的裸芯片),每个内核和Xeon处理器芯片上的高速缓存,内存控制器和I / O控制器之间,采用环形互连的方法,每个完整的环形路径用于进行数据访问或控制指令的传输。尽管设计体系结构可以减少CPU访问延迟并降低传输成本,但是传输路径的选择是有限的。一旦内核数量增加,如果可以快速访问数据并且必须支持更高的内存传输带宽,则现有体系结构将开始受到限制。因此,英特尔决定重新设计新的芯片架构,以使CPU更具延展性。

新一代Skylake-SP服务器处理器将采用新的网格互连架构设计

在新一代的Skylake-SP微体系结构芯片设计中,英特尔首次采用了新的网格互连体系结构设计方法。数据访问和控制命令以连接方式传输。由于可以在每一行和每一列中连接最小的单元,因此每个Skylake-SP内核,高速缓存,内存控制器和I / O控制器路径选择的变化是多样化的,并且还可以跨不同节点互连以找到最短的数据传输捷径。即使增加内核数,它也可以保持对数据的快速访问,并支持更高的内存带宽和更多的高速I / O传输。

英特尔还提供了Mesh体系结构设计的概念图,以说明新体系结构的特征。除了采用新的网状互连架构之外,新一代的至强处理器架构设计还在外部连接的设计和配置方面进行了许多更改。例如,作为用于存储通道管理的存储控制器,它已从其原始位置更改。芯片架构的底部位置移至芯片中间的左侧和右侧,而与其他相邻处理器连接的内部系统总线则移至芯片架构的左上方和右端。

英特尔采用基于Skylake架构的新一代Xeon处理器,并将开始在芯片设计架构中采用新的网状互连架构设计,以取代传统的环形互连设计方法,以改善CPU访问延迟并支持更高的性能。内存带宽要求。

英特尔还表示,采用网格互连架构设计的Skylake-SP处理器还具有低功耗特性,从而允许该处理器以较低的处理器时钟速度运行,并且在较低的工作频率下运行。电压环境,从而可以提供更好的性能改进,并可以提高能源效率。

英特尔还描述,采用全新网格互连架构设计的新一代Xeon处理器可以使GPU在数据访问或指令传输方面更加高效,就像完全设计的高速公路交换系统一样,该系统具有灵活扩展的能力。即使流量很大,它也可以根据流量实时控制入站和出站流量,以减少交通拥堵。

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/shoujiruanjian/article-374956-1.html

- gotomycloud怎么用?gotomycloud注册?GoToMyCloud如何使用

- 凯立德2012夏季版?凯立德导航怎么升级?2016凯立德最新车载版?2012最新凯立德夏季版2921J0B下载

- youku free download?photo funia相册编辑?趣味照片合成(PhotoFunia)3.5.6去

- 8684公交数据包?8684离线版下载?8684公交下载?苏州8684公交查询

- 【灵信宝商务版客户端】灵信宝商务版客户端

- 灵信宝商务版_尽管太阳神孔蒂拉雅维拉科查是世间万物的创造

- 苹果6储存容量几乎已满?苹果4存储容量几乎已满?解决iphone“ 存储容量几乎已满”的办法

- 小雨伞下载?韩娱之幸福小雨伞女主?小雨伞法?小雨伞 v8.2.0.48 免费绿色版下载

如何清除三星s8的内存?三星手机内存快满了,该怎么办?如何删除内存?

如何清除三星s8的内存?三星手机内存快满了,该怎么办?如何删除内存? 从型号看,CPU的外观如何? CPU梯形图从2019年8月到2019年9月的最新排名

从型号看,CPU的外观如何? CPU梯形图从2019年8月到2019年9月的最新排名 听苹果系性冷淡风听多了想撸25N好了

听苹果系性冷淡风听多了想撸25N好了 PCMarkVantage内存子项测试为南亚原厂内存节省70元

PCMarkVantage内存子项测试为南亚原厂内存节省70元

必将来犯之敌全部葬送于南海海域