内存条和一根双Rank的内存是否有ECC功能?

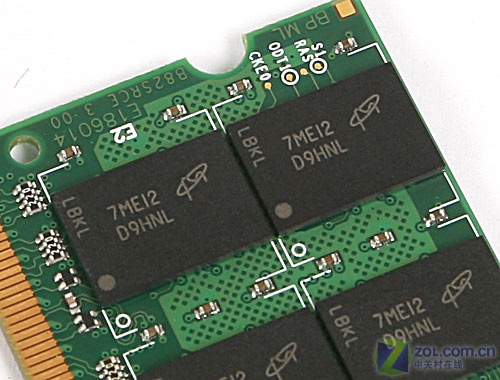

电脑杂谈 发布时间:2021-04-26 11:03:05 来源:网络整理通常,每个人都提到的内存应严格称为内存模块(Memory Module)。记忆棒可以在普通计算机市场或平台上购买。记忆棒通常使用DRAM(动态随机存取存储器)作为存储粒子。几个内存颗粒与矩形印刷电路板配合以形成内存条。除了内存颗粒外,记忆棒上可能还有其他芯片,例如SPD内存芯片,Registering Clock Driver芯片或Data Buffer芯片。

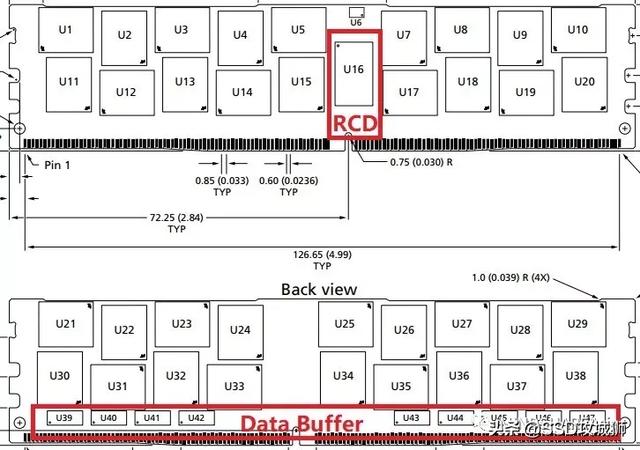

内存模块(RDIMM)的正面

记忆棒的背面

图片中的黑色矩形是芯片的外部封装,其中包含一个或几个芯片(通常是一个芯片)。

在整个计算机系统中,内存条不能单独工作,因此需要相应的内存控制单元(内存控制器)和相应的内存条电源模块。最早的内存控制器位于北桥,但是随着北桥逐渐退出市场,内存控制器已移至处理器内部。

应注意,并非所有计算机系统都使用存储模块,例如Ultrabooks。内存颗粒直接安装在主板上。这样,主板设计应考虑内存模块本身一部分的设计内容。同时,需要提供类似的SPD芯片,或者将其内容嵌入到BIOS中。一些计算机系统使用带有内置高速存储芯片的处理器。当内置存储容量满足要求时,可以省略外部存储插槽的设计。

以下内容可能更基本。已经熟悉的读者可能希望帮助您找出是否有任何错误,并欢迎以各种形式向我们提供反馈。

什么是RAM?

什么是SRAM?

什么是DRAM?

关于这三个问题,请参阅[DDR] SRAM和DRAM

纠缠是跳过吗?您可以尝试以下问题:

两个单列的内存是否与一个双列的内存相同?

带有x16内存颗粒的记忆棒是否具有ECC功能?

RDIMM的RCD奇偶校验主要包括哪些信号?

什么是SDRAM?

SDRAM是同步动态随机存取存储器的缩写。

同步:是指基于同步时钟对内存粒子的读写访问。

动态(Dynamic):动态的含义有两点,一是存储单元的存储内容需要定期刷新,二是电源掉电后存储单元的内容会丢失。已关闭或未刷新。

随机访问:读写操作的延迟不会随访问存储介质的物理位置而变化。

应该注意,通常人们喜欢使用DRAM而不是SDRAM。原因是目前异步DRAM很少。

什么是DDR?

DDR是Double Data Rate(双倍数据速率)的缩写。全名应为DDR SDRAM。 DDR内存是一种SDRAM。在DDR出手指接触主板上的内存模块插槽。此结构称为DIMM。因此有人将内存条称为DIMM条,而主板上的内存插槽也称为DIMM插槽。

由于有DIMM,因此估计存在SIMM(单列直插式内存模块)。有兴趣的读者可以在Internet上搜索。

什么是SODIMM?

在笔记本中使用普通的内存模块会使笔记本太大,而直接使用内存颗粒则不便于扩展和维护。两者之间的间隙由SODIMM填充。 SODIMM是Small DIMM DIMM的缩写,表示小DIMM的大小通常用于笔记本电脑或多合一计算机,如下图所示:

什么是DDR,DDR2,DDR3,DDR4?

DDR实际上是第一代DDR,也可以称为DDR1。

DDR2,DDR3和DDR4是指第二,第三和第四代DDR。它们在电压,速度,时钟拓扑,控制线和地址线拓扑以及支持的命令方面有所不同。除非读者需要,否则此处将不会对其进行扩展。您也可以参考JEDEC的官方规范。

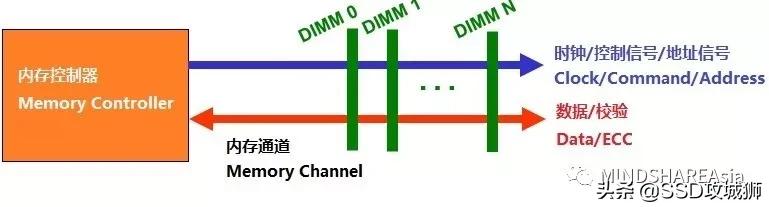

什么是内存通道?

9694b5d27b795922feccf6390ac6d6f6

几个DIMM可以连接到一组总线,这组总线称为内存通道(Memory Channel)。如图所示:

数据和奇偶校验ECC是双向信号,它连接内存通道中的所有DIMM。例如,数据信号DQ0将连接到DIMM0的DQ0和DIMM1 0.的DQ。

时钟,控制信号和地址信号是单向的,由内存控制器发送,并由内存粒子接收。地址信号将连接所有DIMM。

时钟和控制信号将不会连接到所有DIMM,而只能连接到某个DIMM或几个DIMM。例如时钟信号,CKE信号,ODT信号,CS_N片选信号等。具体的连接方法请参考系统设计的参考电路。

什么是记忆颗粒?

内存颗粒(DRAM设备)经常与内存混淆,内存经常与记忆棒混淆。严格来说,内存颗粒是指DRAM器件和DRAM芯片,它们是指符合JEDEC标准的芯片。从广义上讲,封装的存储芯片也可以称为存储颗粒。由于3DS的出现,一个封装中可能包含多个DRAM芯片(Die)。但是通常,一个包装中只有一个模具。

重要的是要注意,JEDEC DDR4的主要规格是针对DRAM设备的,而不是记忆棒。其中引入的信号时序图不是指内存插槽上的时序,而是指内存芯片的输入和输出端口的时序。

什么是排名?

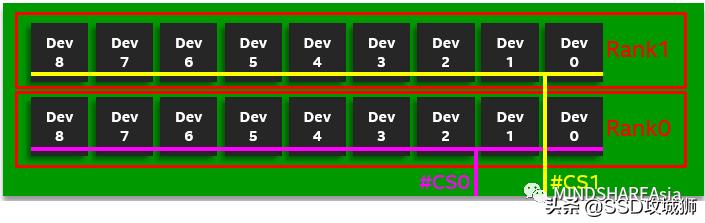

我提到一个内存通道可以有多个DIMM。如果由于某种原因,我们在主板上最多只能允许三个DIMM。例如,从第四个DIMM开始,我们的空间不足,或者由于长度过长等原因导致信号质量下降。但是就性能而言,我们在一个内存通道中需要六个DIMM,我们该怎么办? ?此时,可以引入等级的概念。等级就像逻辑DIMM。我们可以将原始两个物理DIMM的所有内存颗粒安装在内存印刷电路板上,以便内存模块具有两倍的内存容量。我们称这种逻辑DIMM等级。为了支持多列内存模块,我们需要在物理DIMM接口上定义多个CS_N芯片选择信号,以便可以选择相应的列。

x8双列RDIMM:

总而言之,等级是指一组存储粒子的CS信号连接在一起并由存储控制器的单个CS_N信号控制,它们共同形成64位(无ECC)或72位( ECC)存储阵列来共同完成由存储通道发出的指令。

记忆棒的数据宽度是多少?

x86体系结构中存储模块的数据位宽度为64位,即一个时钟周期,如果仅考虑上升沿来传输数据,则一个时钟周期可以传输64位数据。如果选择“双倍数据速率”,则可以在一个时钟周期内传输两个64位数据。

如果记忆棒支持ECC检查功能,则需要额外的8位宽度。因此,除了64位数据外,支持ECC功能的记忆棒还具有8位校验数据。

目前,主流DRAM器件的数据位宽分别为4位,8位和16位,分别为4位,8位和16位。如果使用x4内存颗粒构造具有ECC功能的内存模块,则需要(64+ 8) / 4 = 18 x4内存颗粒。如果使用x8内存颗粒,则仅需要9个内存颗粒。

这样的设计只是单层设计。如果是多列设计,则需要更多的内存颗粒。例如,使用带有ECC的2个Rank存储棒,如果使用x4内存颗粒,则总共需要36个x4 DRAM设备。

请注意,如果使用x16内存颗粒,则无法实现ECC功能,因为4个x16内存颗粒形成了不具有ECC功能的Rank,并且如果再添加一个内存颗粒,它将具有8位更多的位。宽度无法匹配。因此,大多数x16内存都在SODIMM中用于笔记本电脑。当然,如果必须增加ECC功能,则可以考虑添加x8芯片。

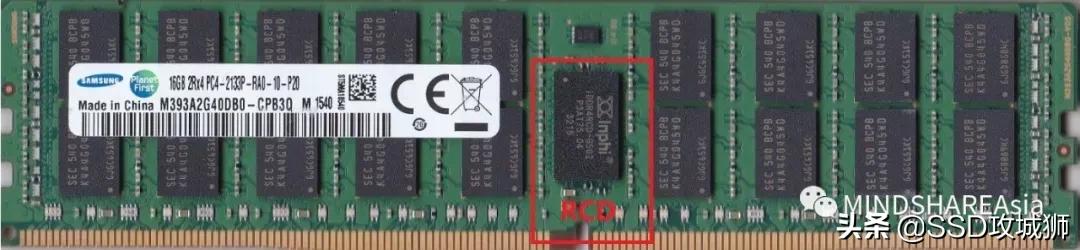

什么是RDIMM?

RDIMM的第一个字母R实际上是前面提到的另一个芯片,称为注册时钟驱动器。没有此芯片的内存模块通常称为UDIMM(无缓冲DIMM)。该寄存器芯片主要用于缓冲时钟/控制/命令/地址和其他信号。缓存的主要目的是解决信号质量和过载问题。

RCD(时钟缓存寄存器芯片):

此外,普通的RDIMM将支持ECC功能和命令/地址奇偶校验功能(CA Parity)。

什么是LRDIMM?

为了通过物理DIMM支持更多列,我们还通过数据缓冲芯片传递数据信号,而不是直接连接到DRAM设备,从而提高了数据信号的质量。如图所示:

参考资料

DDR4内存颗粒的主要规格:JESD79-4 DDR4 SDRAM规格

DDR4 RCD规范:DDR4RCD02规范

DDR4 DB规范:DDR4DB02规范

DDR4 SPD内容存储规范:DDR4 / DDR4E SPD内容主规范

SPD操作规范:EE1004和TSE2004设备规范

JEDEC网站:

内存制造商:

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/shoujiruanjian/article-371032-1.html

-

-

梁梦佳

梁梦佳只是一种在军事上表现一种姿态

-

司马昱

司马昱

- gotomycloud怎么用?gotomycloud注册?GoToMyCloud如何使用

- 凯立德2012夏季版?凯立德导航怎么升级?2016凯立德最新车载版?2012最新凯立德夏季版2921J0B下载

- youku free download?photo funia相册编辑?趣味照片合成(PhotoFunia)3.5.6去

- 8684公交数据包?8684离线版下载?8684公交下载?苏州8684公交查询

- 【灵信宝商务版客户端】灵信宝商务版客户端

- 灵信宝商务版_尽管太阳神孔蒂拉雅维拉科查是世间万物的创造

- 苹果6储存容量几乎已满?苹果4存储容量几乎已满?解决iphone“ 存储容量几乎已满”的办法

- 小雨伞下载?韩娱之幸福小雨伞女主?小雨伞法?小雨伞 v8.2.0.48 免费绿色版下载

华硕RT-AC87U拆解图赏:四颗螺丝后路由器

华硕RT-AC87U拆解图赏:四颗螺丝后路由器 解决办法:主板的多少温度正常?主板温度高的原因及处理方法0

解决办法:主板的多少温度正常?主板温度高的原因及处理方法0 笔记本CPU标准电压与低电压处理器有什么区别?

笔记本CPU标准电压与低电压处理器有什么区别? 解决方法:如果Win7 CPU使用率波动,该怎么办?

解决方法:如果Win7 CPU使用率波动,该怎么办?

怎么样才能完全关闭自动更新