寄存器和内存位置 指令集和PSW的内容参考至2016年10月21日

电脑杂谈 发布时间:2021-03-09 16:03:30 来源:网络整理关于此博客中有关指令集和PSW的内容,请参考:,同时总结寄存器和存储器之间的交互。

命令集

对于每个CPU,它都有一组可以执行的特殊指令(这部分指令由CPU提供)。

正是由于不同CPU体系结构的指令集不同,X86处理器无法执行ARM程序,而ARM程序无法执行X86程序(Inter和AMD都使用x86指令集,而大多数手机都使用ARM指令设置)。

注:指令集分为软件和硬件级别:硬件指令集是CPU本身在硬件级别提供的可执行指令集。软件指令集是指语言库提供的指令,只要安装了语言库,就可以执行。

注册

将要执行的程序部分加载到内存中时,CPU需要从内存中获取指令,然后对指令进行解码(为了知道类型和操作数,可以简单地理解为: CPU需要知道它是什么指令),然后执行该指令。然后接受下一条指令并重复上述操作。

由于CPU访问存储器以获取指令或数据所需的时间比执行指令要多得多,因此在CPU内部提供了一些通用寄存器来存储诸如关键变量和临时数据之类的信息。

因此,CPU需要提供一些特定的指令,以便它可以从内存中读取数据并将其存储在寄存器中,并将寄存器数据存储在存储器中。

通用寄存器

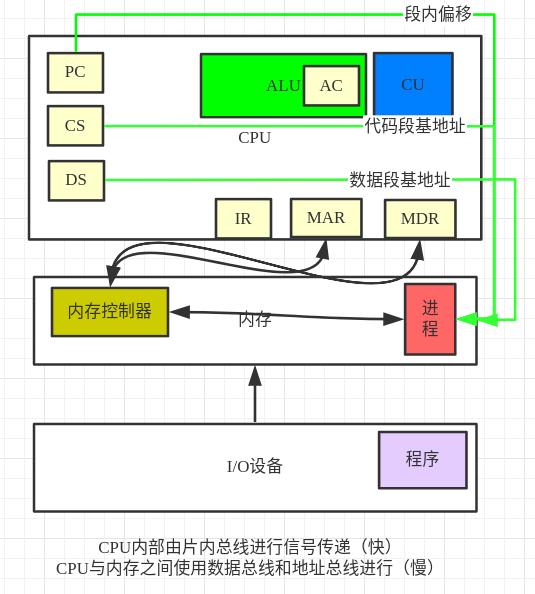

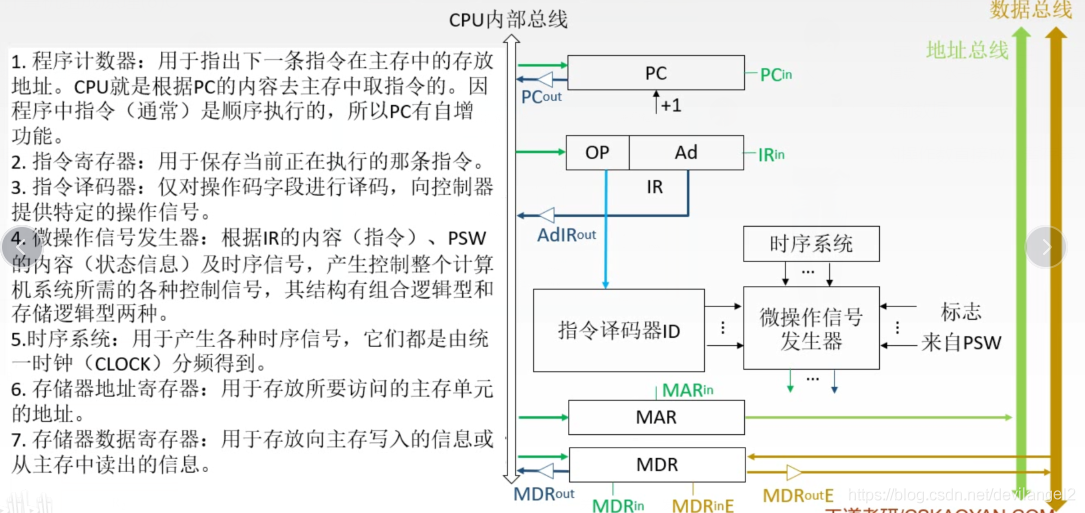

IP寄存器:用于指向当前执行指令的下一条指令(非内部制造商将IP寄存器称为PC寄存器:程序计数器)。提取指令后,寄存器将更新为指向下一条指令;

CS寄存器:代码段寄存器,通常用于存储代码;

通常,CS和IP一起用于处理下一个要执行的代码。

DS寄存器:数据段寄存器,通常用于存储数据;

存储寄存器

MAR:保存要访问的数据的内存地址,并保存地址值

MDR:保存从内存读取的数据或要写入内存的数据,并保存数据值

IR:保存当前正在执行的指令

AC寄存器:累加寄存器,当算术单元的算术逻辑单元(ALU)执行算术或逻辑运算时,它将为ALU提供一个工作区。累积寄存器临时存储ALU操作的结果信息。

以下:

按照上图,以提取并添加指令为例:

获取指令:首先,指令地址在PC中,然后通过片上总线发送到MAR寄存器。 MAR与内存管理器进行交互,以获取MAR指令下的地址指令并将其放入MDR寄存器中。然后将其发送到IR寄存器(IR:存储当前指令);

解码:将指令的操作码部分发送给CU,由CU负责解码;

执行指令:因为它是一条获取和添加指令,所以首先在CU的帮助下执行获取操作,将获取指令的地址代码发送给MAR,然后与内存控制器进行交互以从中获取获取信息内存地址下的数据被发送到MDR;由于需要逻辑运算,通过CU控制,将两个MDR寄存器中的值(保存来自存储器的两个数据)复制到ALU,然后ALU执行加法运算(可以使用在中间的AC寄存器中),计算完成后,将结果复制到MDR寄存器中,最后写回到内存中。

PSW

添加一个重要的寄存器:PSW。

在CPU中,有一个PSW寄存器,代表程序状态字。该寄存器存储一些控制位,例如CPU的优先级和CPU的工作模式(用户模式,内核模式)。

CPU执行进程切换时,需要将寄存器中与当前进程相关的状态数据写入内存对应位置(内核中进程的堆栈空间)以保存它,并在切换回在此过程中,需要将其从内存中删除并将其复制回寄存器。也就是说,切换上下文时,需要保护和还原场景。

内核模式CPU可以执行指令集中的所有指令并使用硬件的所有功能。

仅允许用户模式CPU执行指令集中的某些指令。一般来说,在用户模式下禁止执行与IO和内存保护相关的所有操作。此外,还禁止其他一些特权指令。例如,在用户模式下不能将PSW的模式设置控制位设置为内核模式。

如果用户模式CPU要执行特权操作,则需要启动系统调用以请求内核来帮助完成相应的操作。实际上,在启动系统调用之后,CPU将执行trap指令以捕获(捕获)到内核。特权操作完成后,需要执行一条指令以使CPU返回用户模式。

除了将落入内核的系统调用之外,更多的硬件将导致陷阱行为落入内核,以便CPU控制可以返回到操作系统,以便操作系统可以决定如何处理硬件异常。

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/shoujiruanjian/article-363207-1.html

-

-

吕雉

吕雉给手下的小弟摇旗呐喊而已

-

- gotomycloud怎么用?gotomycloud注册?GoToMyCloud如何使用

- 凯立德2012夏季版?凯立德导航怎么升级?2016凯立德最新车载版?2012最新凯立德夏季版2921J0B下载

- youku free download?photo funia相册编辑?趣味照片合成(PhotoFunia)3.5.6去

- 8684公交数据包?8684离线版下载?8684公交下载?苏州8684公交查询

- 【灵信宝商务版客户端】灵信宝商务版客户端

- 灵信宝商务版_尽管太阳神孔蒂拉雅维拉科查是世间万物的创造

- 苹果6储存容量几乎已满?苹果4存储容量几乎已满?解决iphone“ 存储容量几乎已满”的办法

- 小雨伞下载?韩娱之幸福小雨伞女主?小雨伞法?小雨伞 v8.2.0.48 免费绿色版下载

而且