解决方案:前端总线频率(FSB)和DDR存储器频率的详细说明

电脑杂谈 发布时间:2021-01-12 06:14:22 来源:网络整理FSB

FSB是主板为CPU提供的参考时钟频率,通常为100、133、166、200。我们正在谈论的FSB(FrontSystemBus)是指系统前端总线,它是处理器与主板北桥芯片或内存控制集线器之间的数据通道。常见频率是400、333、533、800。

作为新手,您不必掌握太多概念性的东西,只需记住以下公式即可:

主频率= FSB *乘数(MHz)

IntelCPU前端总线= FSB * 4(MHz)

AMDCPU前端总线= FSB * 2(MHz)

CPU数据带宽=前端总线* 8(MB / s)

内存带宽=内存等效工作频率* 8(MB / s)

前端总线频率

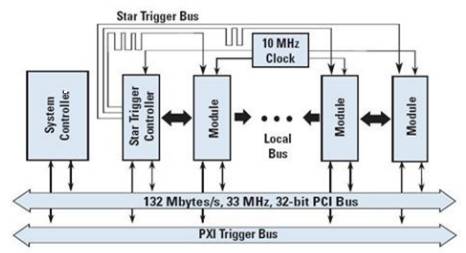

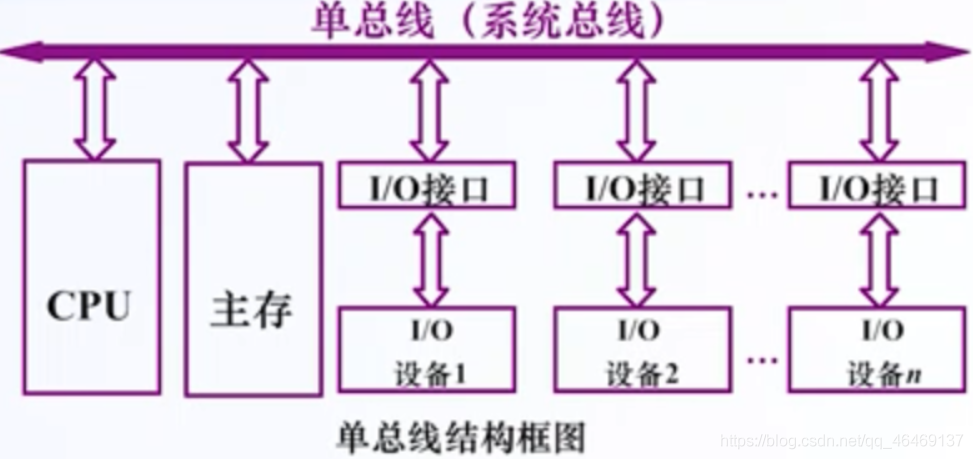

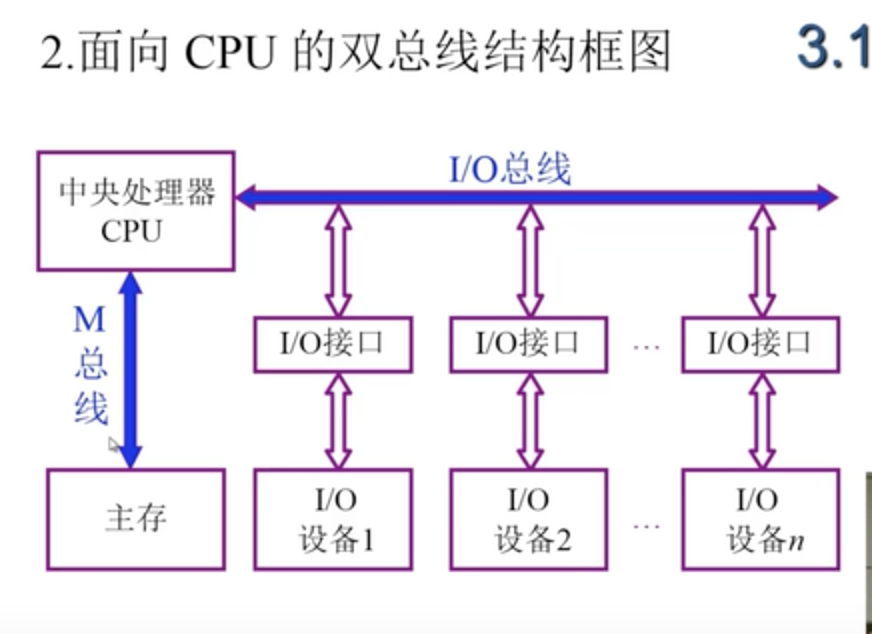

Bus是一组传输线,这些传输线将信息与一个或多个源组件传输到一个或多个目标组件。用外行的话来说,它是多个组件之间的通用连接,用于在每个组件之间传输信息。人们经常以MHz为单位描述总线频率。公共汽车有很多类型。前端总线的英文名称是FrontSideBus,通常用FSB表示,FSB是将CPU连接到北桥芯片的总线。计算机的前端总线频率由CPU和北桥芯片确定。

北桥芯片负责与内存,图形卡和其他具有最大数据吞吐量的组件进行联系,并与南桥芯片连接。 CPU通过前端总线(FSB)连接到北桥芯片,然后通过北桥芯片与内存和图形卡交换数据。前端总线是CPU与外界交换数据的最重要通道。因此,前端总线的数据传输容量对计算机的整体性能有很大的影响。如果没有足够快的前端总线,则无论CPU的强度如何,都无法显着提高计算机的整体速度。数据传输的最大带宽取决于所有同时传输的数据的宽度和传输频率,即数据带宽=(总线频率×数据位宽度)÷8。目前,可以在PC分别为266MHz,333MHz,400MHz,533MHz,800MHz,最高为1066MHz。前端总线的频率越高,CPU与北桥芯片之间的数据传输容量就越大,并且能够充分发挥CPU的功能。当前的CPU技术发展迅速,计算速度迅速提高。足够大的前端总线可以确保将足够的数据提供给CPU。较低的前端总线将无法向CPU提供足够的数据,这限制了CPU性能。必须发挥作用并成为系统瓶颈。

FSB和FSB频率之间的差异

前端总线的速度是指CPU与北桥芯片之间的总线速度,更实质地表示CPU与外界之间的数据传输速度。 FSB的概念基于数字脉冲信号的振荡速度。换句话说,100MHz FSB专门指每秒振荡10,000次的数字脉冲信号,这对PCI和其他总线的影响更大。频率。前端总线和FSB的两个概念容易混淆的主要原因是在很长一段时间之前(主要是在Pentium 4出现之前以及Pentium 4刚出现时),前端总线的频率是与FSB相同。因此,前端总线通常直接称为FSB,这最终会引起这种误解。随着计算机技术的发展,人们发现前端总线频率需要高于FSB,因此使用QDR(QuadDateRate)技术或其他类似技术来实现这一目标。这些技术的原理类似于AGP的2倍或4倍。它们使前端总线的频率比FSB高2倍,4倍甚至更高。从那时起,前端总线和FSB之间的差异就得到了关注。当前的主流产品使用这些技术。

DDR和DDR2内存说明

DDR传输标准

严格来说,DDR应该称为DDRSDRAM。人们习惯称其为DDR。一些初学者经常看到DDRSDRAM并认为它是SDRAM。 DDRSDRAM是DoubleDataRateSDRAM的缩写,表示双倍速率同步动态随机存取存储器。 DDR存储器是在SDRAM存储器的基础上开发的,并且仍使用SDRAM生产系统。因此,对于存储器制造商来说,他们只需稍)技术。当数据有效时,存储控制器可以使用此经过数据滤波的信号来精确定位数据,每16次输出一次,并重新同步来自不同存储模块的数据。 DDR基本上不需要增加时钟频率就可以使SDRAM的速度提高一倍。它可以在时钟脉冲的上升沿和下降沿读取数据,因此其速度是标准SDRA的两倍。

DDR和SDRAM在物理体积方面的差异并不大,它们具有相同的大小和相同的引脚距离。但是DDR有184个引脚,比SDRAM多16个引脚,SDRAM主要包括新的控制,时钟,电源和接地信号。 DDR内存使用支持2.5V电压的SSTL2标准,而不是SDRAM使用的3.3V LVTTL标准。

DDR存储器的频率可以两种方式表示:工作频率和等效频率。工作频率是存储器颗粒的实际工作频率。但是,由于DDR存储器可以在脉冲的上升沿和下降沿都传输数据,所以等效频率是工作频率的两倍。

如果PC1600是根据传统传输标准命名的,则PC1600(DDR200)应该是PC200。当时,DDR内存正在与RDRAM内存竞争下一代内存标准。因此,对它不了解的人自然会认为PC200远远落后于PC600,根据市场竞争的考虑,JEDEC调整了DDR存储器的命名约定。 DDR内存是根据内存的传输速率来命名的。这就是为什么今天的PC1600、PC2100、PC2700、PC3200、PC3500等。 CPU-Z工具,将显示“ SPD最大带宽”。

PC1600的实际工作频率为100MHz,等效工作频率为200MHz,则其数据传输速率为“数据传输速率=频率*每次传输的数据位数”,即200MHz * 64bit = 12800Mb / s ,然后除以8,将其转换为MB作为单位,即1600MB / s,称为PC1600。

DDR2传输标准

DDR2可以看作是DDR技术标准的升级和扩展:DDR的核心频率等于时钟频率,但是数据频率是时钟频率的两倍,这意味着数据必须一次传输两次。时钟周期。 DDR2使用“ 4位预取(4位预取)”机制,核心频率仅为时钟频率的一半,而时钟频率为数据频率的一半,因此即使核心频率仍为200MHz,数据频率DDR2内存可以达到800MHz —这就是所谓的DDR2800。

当前,现有的标准DDR2内存分为DDR2400和DDR2533,DDR2667和DDR2800。核心频率为100MHz,133MHz,166MHz和200MHz,总线频率(时钟频率)分别为200MHz,266MHz,333MHz和400MHz。 ,等效数据传输频率为400MHz,533MHz,667MHz和800MHz,相应的内存传输带宽分别为3.2GB / sec,4.3GB / sec,5.3GB / sec和6.4GB / sec ,根据内存传输带宽标记为PC23200、PC24300、PC25300和PC26400。

**************************

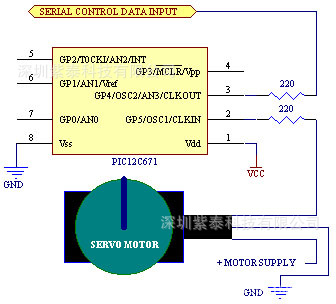

* SDRAM和DDR接线指南*

**************************

2007/02 /

ecos应用程序与硬件平台无关。尽管开发板不涉及SDRAM和DDR,但是在某些高端平台上使用ecos时,您可能会遇到内存布线问题。对于完整的描述,我们将在这里给出解释。

许对内存接线感到困惑,找不到切入点,也不知道如何启动,实际上,高速硬件设计的主要任务是抗干扰,内存接线也不例外。这样考虑:内存有什么用?它用于存储数据,写1读为1,写0读为0,以确保正确的数据访问。那么,什么情况下会导致数据访问错误?

1、判断错误,将0判断为1,将1判断为0。参考电平可能不准确(为什么不呢?由信号线的内部电阻引起的电压降),可能是附加干扰,或者阻抗不匹配可能会导致信号失真。

2、时序错误,建立/保持时间不满足,或者采样点的相位错误,并且不在有效信号位置。扳机需要维持一段时间的能量供应才能正常工作,这就是建立/保持时间。

只要您解决了这两个问题并确保正确访问内存,就可以成功设计内存电路。

使用此指导思想,可以逐步完成内存布线。但是,对于不同的RAM类型,尽管目标是避免判断和时序错误,但由于工作模式不同,实现方法也有很大差异。

高速系统通常使用低压,低摆幅的低压信号,这些信号容易提高速度并降低功耗,但这给接线带来了困难,因为低压信号的功率会受到很大的影响。信号线的内部电阻,即电压平方关系。因此,有必要将内部电阻减至最小,例如使用电气平面,打更多的孔,缩短布线距离以及最终使用电阻器进行高压传输用较低的电压分压信号。 SDRAM,DDR-I,DDR-II和DDR-III的信号电压低于1,从而使其越来越难以稳定。

请注意电源。如果电源不足,内存将无法稳定工作。

我经常看到“等长接线”。实际上,长度相等不是目的。真正的目的是满足建立和保持时间,相同的频率和相位,并且采样正确。相等的长度只是实现此目标的最简单方法。要定量分析线长,必须根据时钟模型公式进行计算。时钟同步电路的类型在后面简要介绍,只要您知道SDRAM是通用时钟同步而DDR是源同步。

SDRAM是一种常见的时钟同步模式,它只关心建立时间,而不关心保持时间。这些时间与每个段的飞行时间,每个门电路的延迟,时钟偏斜,抖动,周期等有关,需要根据公式进行精确计算。计算完各种参数后,请遵循规则并让EDA软件协助设计。只要长度相同,就不需要计算最长的线。有些软件可以自己计算,而有些只能自己计算。您可以对EXCEL表进行编程,以自动以某种格式对报告文件求和,这也是的。

所有DDR信号都必须匹配,无论多么复杂,以确保稳定性。

起始端匹配可以与22/33欧姆电阻串联。端子匹配分为交流匹配和直流匹配。电阻和电容可以抑制噪声。戴维宁电路可提供高压传输,以使参考电平更加准确。功耗高,但功耗却比单个50欧姆低。

CPU和DDR都是高速设备。 DDR发热量高,应远离。 DDR是一种源同步时钟模式,需要保持时间。并不是说线越短越好,并要求最小距离。确保时钟稳定,频率和相位相同,并且冗余足够。

有时,信号线交叉。此时,您可以调整PCB中的线,然后反转标记,因为只要有存储位的地方,RAM的每条数据线都不需要相互对应。注意:刷新线A10不能调整,当需要读取RAM ID时也不能调整。

对设计质量的评估取决于余量(冗余),设置时间余量和保持时间余量。 SDRAM / DDR运行良好并不意味着利润很小。它可能在实验室中正常工作,但是一旦您到达现场,就会崩溃。频率漂移,时钟抖动,相位差,介电常数变化等将导致采样误差/不满足建立和保持时间,并且较大的裕度可以尽可能抵抗这些干扰,并在恶劣的环境中保持稳定。

记忆有两种表现形式:记忆颗粒和记忆棒。内存模块具有自己的走线长度,需要计算。提出一个问题:有3种安装内存模块的方式:垂直插入,对角插入和水平插入。您认为哪种方法更好?

附件:时钟同步电路的类型

源同步意味着时钟选通信号clk由驱动器芯片与发送数据一起发送。通用时钟同步意味着在数据传输过程中,总线上的驱动端和接收端共享相同的时钟源,并且相同的时钟缓冲器(时钟缓冲器)发出同相时钟以完成数据的发送和接收

通用时钟同步,同一时钟信号通过时钟分配器分为2个通道,一个连接到,另一个连接到。在时钟的上升沿发送数据,并在下一个周期的上升沿采样和接收。速度低于200-300MHZ。

源同步是指时钟和数据一起发送,而时钟则稍晚发送。传输速率主要由数据和时钟信号之间的时间差决定。所以速度很快。

公共时钟同步电路的走线长度为len时钟的最大值

|| ---

------ |

||

-通用时钟同步

-----

|驱动器| ------------------> clk

|活动|

|| ===============>数据

-----

源同步

------------------

-------------

------------------

-----------

||

--------------------

|||

创建和维护

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/shoujiruanjian/article-347211-1.html

-

肖源圣

肖源圣 -

张文规

张文规美国佬在叙利亚被普京把了脸跑到南海来撒野

- gotomycloud怎么用?gotomycloud注册?GoToMyCloud如何使用

- 凯立德2012夏季版?凯立德导航怎么升级?2016凯立德最新车载版?2012最新凯立德夏季版2921J0B下载

- youku free download?photo funia相册编辑?趣味照片合成(PhotoFunia)3.5.6去

- 8684公交数据包?8684离线版下载?8684公交下载?苏州8684公交查询

- 【灵信宝商务版客户端】灵信宝商务版客户端

- 灵信宝商务版_尽管太阳神孔蒂拉雅维拉科查是世间万物的创造

- 苹果6储存容量几乎已满?苹果4存储容量几乎已满?解决iphone“ 存储容量几乎已满”的办法

- 小雨伞下载?韩娱之幸福小雨伞女主?小雨伞法?小雨伞 v8.2.0.48 免费绿色版下载