超强:组成原理(五)CPU指令流水线

电脑杂谈 发布时间:2020-12-26 15:01:10 来源:网络整理5.5个CPU指令流水线一.流水线

装配线

([1)管道:

从指令值到实际执行的过程分为多个小步骤。当CPU实际上开始执行指令序列时,将逐步执行该指令以减少其等待时间。

(2)流水线级越多,工作效率越高。英特尔处理器的流水线级远远超过嵌入式CPU的流水线级

(3)管道的效率:

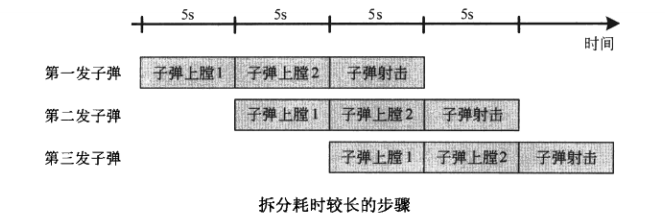

a。指令各步骤的操作时间长度不同。长跳步步骤将导致管道效率降低(短跳步步骤必须等待长跳步步骤完成)

b。解决方案:

i。长时间跳动

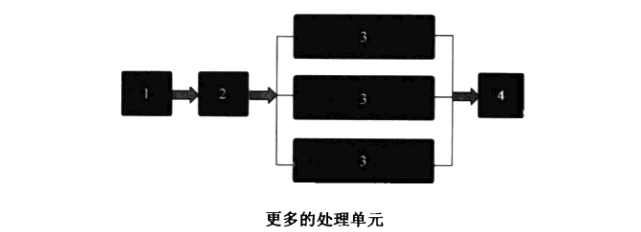

ii。添加长拍处理单元:对于短拍动作,同时获得多个长拍执行结果。

例如:长拍是短拍执行时间的3倍,可以增加到3个长拍执行单元和1个短拍执行单元

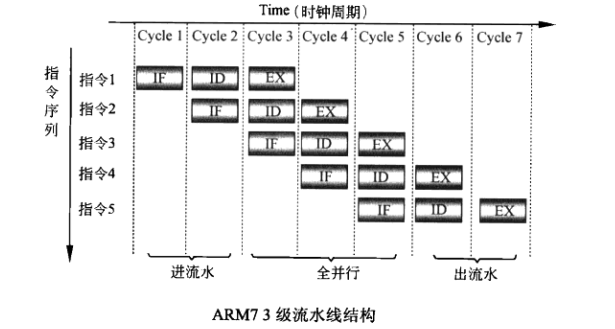

ARM7的三阶段流水线:

ARM7将已知的指令执行时间分为3个步骤:提取IF,解码ID和执行EX

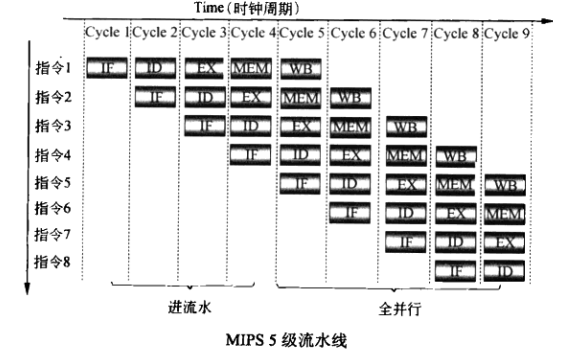

经典MIPS5级管道

(1)处理器内部的程序员可以看到许多通用寄存器。这些通用寄存器构成了寄存器文件寄存器文件

(2)为了防止不同管道之间的数据相互干扰,CPU会在每个阶段将通用寄存器中的值复制到管道寄存器中,以免每个拍子的工作订单。

(3)在汇编语言中,ALU执行单元直接访问通用寄存器,但是在硬件实现中,通用寄存器的值首先被复制到ALU输入寄存器(流水线寄存器)中,然后发送回通用寄存器

(4)MIPS在三级流水线的基础上增加了两个阶段,一个是mem阶段,从内存中获取数据,另一个是WB阶段,将ALU计算后的数据导出到通用注册文件

IF-> ID-> EX-> MEM-> WB

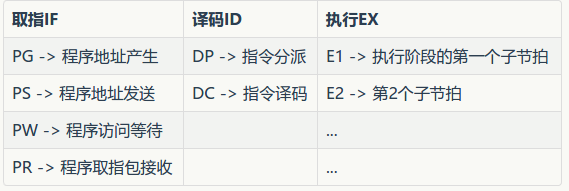

DSP对三级流水线的深度扩展

([1) DSP处理器将获取,解码和执行的三个主要步骤细分为多个小步骤

(2) MIPS处理器将MEM和ALU计算放在不同的阶段,写回通用寄存器也形成了一个单独的阶段。DSP将MEM和WB阶段都放在了指令执行阶段,这更符合程序员视角。

三.管道思维历险记

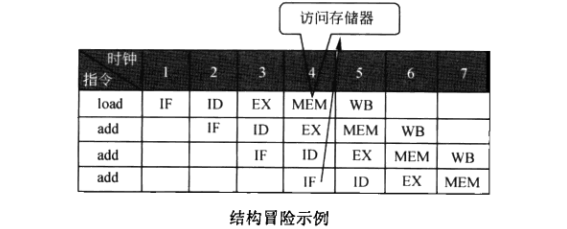

结构风险:由于硬件资源冲突,不同阶段的执行步骤无法同时执行

在MIPS处理器的流水线中,IF级需要访问内存以获取指令,而MEM级需要访问内存以获取数据。这两个动作必须访问存储器,从而导致存储器和寄存器之间的总线冲突,无法同时执行。但是,在现代处理器中,程序存储在L1P缓存中,数据存储在L1D缓存中,因此没有冲突。

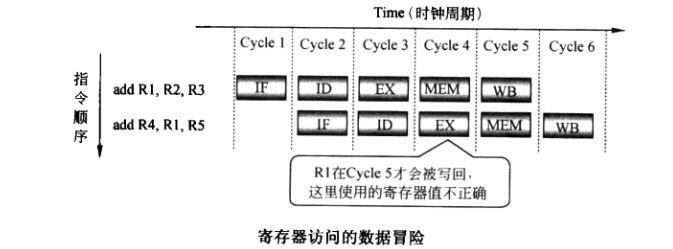

数据冒险

(1)管道使先前订购的指令同时处理。当某些指令组合出现时,可能导致使用错误的数据。

(2)因此,cpu使用转发来解决问题:如果当前指令的源操作数在EX / MEM的流水线寄存器中,则将流水线寄存器中的值直接传递给ALU输入通用寄存器文件的值

(3)但并非所有数据冲突都可以通过传递解决,必须配置循环等待

子指令的R1最早只能在cycle4中到达MEM / EX流水线寄存器,因此仍然有必要隐藏一个循环

控制冒险:

(1)当流水线中的一条指令具有跳转操作时,其他流水线预先进行的操作将根据pc + 1进行提取,而跳转操作会使这些流水线上的所有操作无效

(2)流水线级别越深,跳转指令导致的效率下降越严重

四.管道分支预测

1位预测算法:

如果指令上次跳转,则预计这次跳转也会发生

2位预测算法:

每条指令的预测状态信息从1位添加到2位。如果执行了跳转,则将为+1,如果将其添加为3,则将不会添加。如果不执行跳转信息,它将为-1,并且不会减少为0。如果计数器值为0/1,则不执行预测,而计数器为2/3,则执行预测。

英特尔分支预测实现

(1)前两个是算法思想。英特尔在此基础上进行了一系列设计。英特尔分支预测包括3个单元:分支目标缓冲区(BTB),静态预测器和返回堆栈

五.乱序执行指令

乱序执行

执行指令时,由于某些限制,它们通常会等待。例如,在MEM阶段访问的数据不在高速缓存中,需要从外部存储器获取。此操作需要数十个周期。如果按顺序执行,则以下指令MEM必须等待指令操作完成。无序执行意味着不依赖数据的指令将首先执行。

命令依赖性

([1)与寄存器相关:当两个指令共享寄存器时,它们可能是相关的。

a。先阅读然后阅读

ADD BX,AX

ADD CX,AX #2条指令先后读取AX寄存器

b。 RAW:写后读

```shell

ADD BX,AX

ADD CX,BX #后面的指令依赖前面的指令。先写BX,后读BX,指令间存在数据流动

```

c。 WAR:读后写

```shell

ADD BX,AX

MOV AX,CX #指令1读AX,指令2写AX,逻辑上本没有相关性,但X86cpu的寄存器太少,指令要公用寄存器,导致指令相关

```

d。先写(WAW)

```shell

MOV AX,BX

MOV AX,CX #输出到同一个寄存器

```

[注]:WAR和WAW在两条指令之间没有数据流,这称为伪相关。

与控制相关:

上一条指令是跳转指令,下一条指令的执行需要跳转指令的结果。这是控制相关三.删除指令相关

删除与数据相关的

与数据删除相关的操作不是由CPU执行,而是由编译器和程序员执行。

x = a + b

y = x + c

z = y + d // x,y,z产生深度相关

// 改造后

x = a + b

y = b + c

z = x + y // 此时去除了x,y间的相关性

删除与控制相关的

推测执行:cpu可以根据跳转预测的结果将跳转指令放在要执行的跳转指令之前,这是一种预测的推测行为。现代分支预测的准确性能达到98%以上,因此可以在一定程度上消除控制相关性

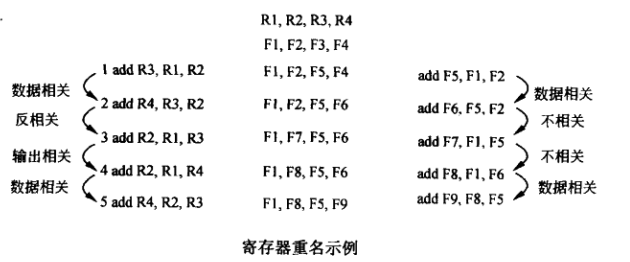

删除错误的相关性:WAW,WAR

(1)处理器的ISA寄存器的数量通常很少(暴露给程序员的寄存器),这将导致多个变量映射到同一寄存器,因此即使指令在逻辑上不相关,它们会相关,因为使用了相同的寄存器。

([2)通过将相同的ISA寄存器映射到不同的物理寄存器来解决伪相关(名称相关)。

([3)映射策略:

将每条指令的目标寄存器映射到新的物理寄存器。将指令的源寄存器映射到ISA寄存器最近映射到的物理寄存器。执行该指令后,可以使用映射到目标寄存器的较早物理寄存器。已发布

首先,R1,R2,R3和R4分别映射到F1,F2,F3和F4。第一条指令R3是目标寄存器,并且到新物理寄存器F5的映射将用完物理寄存器,因此每当第二条映射完成后,它必须实时释放:R4寄存器开始映射到F4寄存器,在指令2之后,R4映射到F6寄存器,此时,可以释放原始的F4寄存器四. CPU如何执行乱序执行

缓冲区

CPU必须提供能够缓存多条指令的缓冲区,以实现乱序执行的效果

指令调度

(1)指令具有操作数和操作码。操作码描述了指令的作用(CPU分配的执行单元类型);重命名寄存器后,目标寄存器始终是新的,因此指令是否可以被执行,与目标操作数无关,但与操作码和源操作数有关

(2) 2个要执行的条件,除了这2个条件外,该指令无需等待上一条指令的执行完成

cpu中是否有空闲执行单元来执行该指令(操作码),是准备按顺序提交指令结果的指令的源操作数

(1)尽管指令的执行顺序不正确,但是提交指令结果的顺序必须是顺序的。由于存在“精确中断”

(2)精确中断:在执行该指令期间,会有一个中断。这时,CPU将ISA寄存器压入堆栈,执行中断服务程序,然后在中断之后执行指令。精确的中断需要终端货币的指令全部执行,中断之后的指令均不执行,在无序执行内核中,终端后面的指令可以在中断前面执行

(3)因此,CPU引入了一个重排序缓冲区来缓冲指令的执行结果。这些结果将顺序提交给寄存器以实现精确的中断。五.处理器并行体系结构

弗林分类

1966年,Flynn将处理器系统结构分为4类

(1) SISD:处理器一次处理一条指令,每条指令处理一条数据(单条指令单条数据)

([2) SIMD:一次处理一个数据,一条指令可以处理多个数据点(数据并行)

(3) MISD:一次处理多条指令,每条指令处理一个数据(此设计无用)

([4)MIMD:一次处理多条指令,每条指令可以处理多个数据点

并行命令

(1)发射单元一次发出多条指令,它可以实现指令并行(多次发出)

([2)两种多重发行方式

i。 SuperScalar:Super Scalar(硬件)

a。超标量意味着在cpu内添加一个硬件单元,该硬件单元负责并行化行程指令的输入。

b。奔腾4使用超标量实现指令并行化

ii。 VLIW:非常长的指令字(软件)

a。非常长的指令字意味着编译器或程序员用汇编语言声明要在一个周期内执行多条指令。 || Symlink 2指令

b。 TI C6000 DSP使用超长指令字实现指令并行性

(3)超标量由于需要增加电路设计和功耗,因此在执行阶段并行制定超标量。为了确保程序兼容性,x86必须使用超标量,而以后的RISC处理器可以使用超级标量。长指令字VIEW结构

(4)在并行性方面,VIEW更好,因为它实现了源代码中的指令并行性,并且擅长数据密集型操作。但是,当发生高速缓存未命中时,VIEW无能为力并且使用乱序+超标量处理器可以提前执行以下指令,因此乱序+超标量适用于负责任的控制程序。

数据并行

([1)多媒体程序具有一个功能:相同的操作应用于多个数据,因此会生成SIMD

([2) Intel的MMD,SSE2,SSE3,SSE4.1,SSE4.2,AVX指令集都是SIMD。AMD的3DNOW!,SSE5指令集也是SIMD

([3) MMX指令可以一次处理64位数据,SSX指令可以一次处理128位数据

([4)几种不同的SSE指令

(a)垂直计算

SSE指令将需要操作的两个寄存器中的数字划分为几个相应的段,并且两个寄存器对相应段中的数据进行操作

(b)水平计算

两个源操作数来自同一寄存器

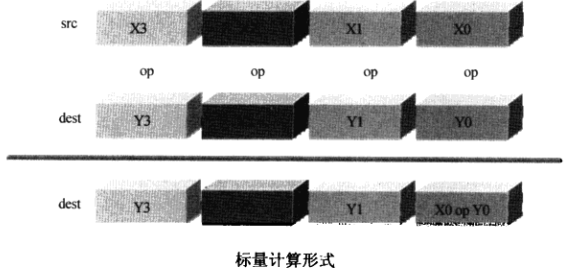

(c)标量计算

a。类似于垂直计算的2个寄存器段,不同之处在于标量计算只能计算2个寄存器中的1个段,而其他段保持不变

b。如下所示,只有x0和y0被操作,其他部分保持未经训练的状态

线程并行

([1)软件多线程:时分多路复用操作系统

([2)硬件多线程

(a)粗粒度的硬件多线程:

当处理器发现某个线程被长时间阻塞(例如:高速缓存未命中)时,将发出另一个线程的指令

(b)细粒度的硬件多线程

处理器的每个周期都从不同的线程发送指令

(c)同时多线程

超标量处理器可以同时发送多个指令,这些指令来自不同的线程

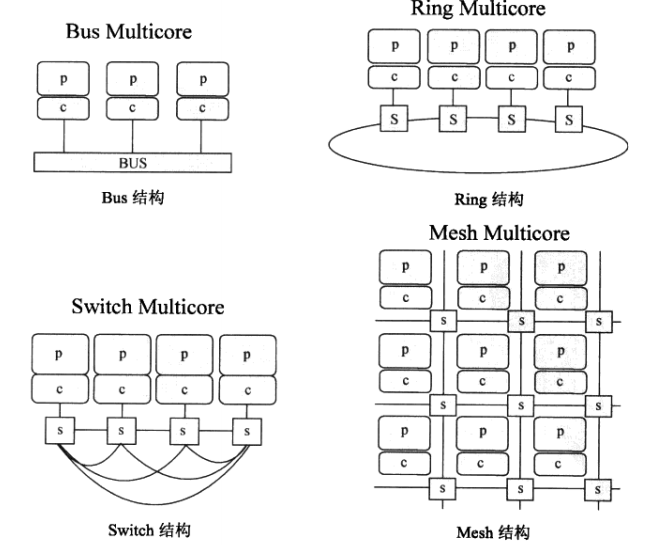

([3)多核处理器体系结构

i。 p:处理器处理核心,c:缓存缓存,而s:switch用于核心间通信。线表示通讯路径

ii。总线多核结构多核:设计简单,但是任何两个核将占用总线进行通信,这将导致其他核无法通信并降低效率。

iii。 Swich多核结构:多核:任意两个核之间的独立通信连接。 1,2核心通信不会阻止3,4核心通信。但是,这种方法消耗大量的互连资源。 SwitchMulticore通常用于4个核心。不管有多少个内核,都会浪费资源

v.Ring多核结构多核:改进了总线结构,1和3通过2进行通信,并且两个相邻的核具有最快的通信速度。通常有8个内核使用这种结构

vi。 Mesh Multicore结构多核:类似于二维Ring结构。当内核过多时,开关结构将导致连接过于复杂。网状结构有利于扩展和高效率。许多内核(例如64核)都可以使用此设计。

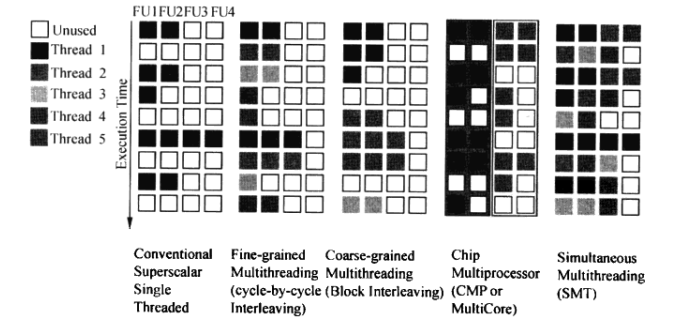

([4)各种硬件多线程的比较

(a)图形说明:每行代表一个循环

(b)每列代表一个功能单元

i。第一个是单线程处理器,大量功能单元处于空闲状态,有时if和id阶段中的所有控制单元都处于空闲状态

ii。细粒度的多线程:每个周期从不同的线程发送指令

iii。粗粒度多线程:当cpu发现某个线程被阻塞(高速缓存未命中)时,它将发出另一个线程的指令

iv。多核技术:每个核2个功能单元,无硬件多线程,2个核分别处理2个不同的线程

V。同时执行多线程:功能单元的利用率最高,超标量CPU会同时从多个线程发送指令,每个线程使用不同的功能单元

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/shoujiruanjian/article-343339-1.html

-

-

王明杰

王明杰全世界都知道美国是中东乱局始作俑者

- gotomycloud怎么用?gotomycloud注册?GoToMyCloud如何使用

- 凯立德2012夏季版?凯立德导航怎么升级?2016凯立德最新车载版?2012最新凯立德夏季版2921J0B下载

- youku free download?photo funia相册编辑?趣味照片合成(PhotoFunia)3.5.6去

- 8684公交数据包?8684离线版下载?8684公交下载?苏州8684公交查询

- 【灵信宝商务版客户端】灵信宝商务版客户端

- 灵信宝商务版_尽管太阳神孔蒂拉雅维拉科查是世间万物的创造

- 苹果6储存容量几乎已满?苹果4存储容量几乎已满?解决iphone“ 存储容量几乎已满”的办法

- 小雨伞下载?韩娱之幸福小雨伞女主?小雨伞法?小雨伞 v8.2.0.48 免费绿色版下载

班花小红mm听室友说自己的电脑配置太低了

班花小红mm听室友说自己的电脑配置太低了 CPU的类型是什么?

CPU的类型是什么? 事实:当前,64G的手机内存基本上是不够的,但是为什么苹果仍会发布64G的手机?

事实:当前,64G的手机内存基本上是不够的,但是为什么苹果仍会发布64G的手机? 最新版本:CPU二级缓存的功能是什么

最新版本:CPU二级缓存的功能是什么

不如把錢投到房地產