DDR4实用教学(一):DDR4寻址原理

电脑杂谈 发布时间:2020-12-23 20:04:17 来源:网络整理2011年1月4日,三星电子完成了历史上第一款DDR4内存。 DDR4和DDR3之间的三个最大区别是:16位预取机制(DDR3为8位),在相同核心频率下,理论速度是DDR3的两倍。传输规格更加可靠,数据可靠性进一步提高;工作电压下降到1.2V,更节能。

它看起来很棒,那么DDR4是什么?它是如何工作的?硬件设计涉及哪些参数?在这一系列博客文章中,我们将为大家讨论。

本文简要讨论了DDR4是什么以及DDR4的工作原理。

什么是DDR4?

与其他DDR系列DRAM一样,DDR4的全名是DDR4-DRAM,是当前电子系统体系结构中使用最广泛的RAM存储器。

这句话可以分解为3个关键词:内存,DRAM,DDR4。

让我们先谈一下存储。顾名思义,谈到存储,它是一个动词。以生活为例。如果有酸奶,则当您不想吃时,请将酸奶存放在冰箱,特定楼层和特定位置。进餐时,将酸奶放在冰箱中的某个位置和某个位置。

这个过程称为存储,结合了生命,我们可以看到存储需要3个关键操作:

1.酸奶在哪里?你必须知道。如果您不知道将它放在哪里,那么酸奶就像失去了一样。映射到电子领域的这一过程称为“寻址”。

2.存放酸奶并取出酸奶。您需要先去某个冰箱,打开一个抽屉,然后从某个位置取出酸奶。该过程映射到电子领域,称为“读/写”。

3.将酸奶放在该位置,必要时必须可以食用。映射到电子领域的这一过程称为“数据保存”。

总而言之,内存是一种可以“寻址”,“可以读写数据”和“可以保存数据”的电子设备。

让我们再次谈谈DRAM。 DRAM的全名是动态随机存取存储器,它被翻译为动态随机存取存储器。所谓随机是指“将其存储在任何要存储的地方”,听起来非常自由和灵活。所谓动态的是指在保存数据的过程中不断补充电源的需求。听起来非常耗电且费力。为什么我们仍然使用DRAM结构?因为在电路结构上,DRAM的结构比SRAM简单得多。

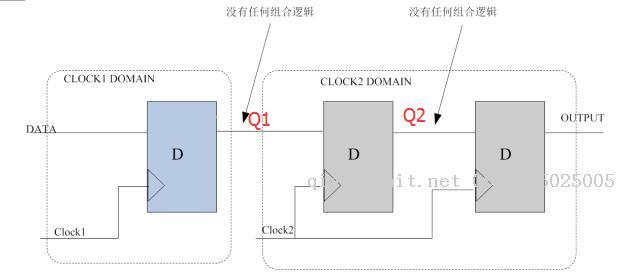

最后谈谈DDR。当我们谈论DDR时,每个人都会想到内存,但实际上DDR并不是指内存。 DDR实际上是一种技术,全名是Double Data Rate,它转换为Double Rate,但是这些技术已广泛用于DRAM中。因此人们习惯将DDR称为内存,因此婴儿在随后的硬件设计过程中会在其他总线上看到DDR,请不要惊慌,因为您看到的DDR不一定与存储有关。双倍利率是什么意思?可以简单地说,当第一代存储器读写数据时,每当时钟信号从低到高或从高到低变化时,就对数据进行采样。一个时钟周期只能采样一个数字。当时钟从低到高时,随后的聪明人会采样一个数据,而当时钟从高到低时,将再采样一个数据。一个时钟周期可以采样两个数据。因此读写速度是以前的2倍。此技术手段指的是DDR。如果您不懂“时钟”和“采样”一词,那么...

因此,总而言之:DDR4-DRAM是第四代静态存储器,支持双重数据读取和随机位置访问。

DDR4-DRAM的工作原理

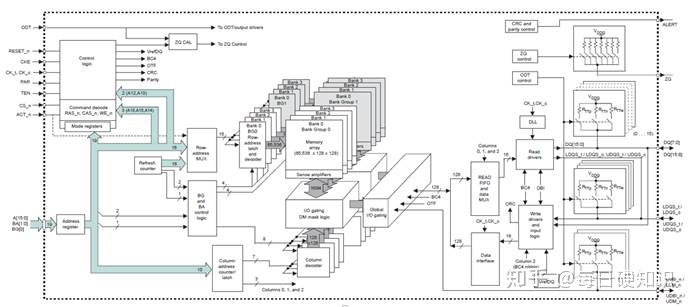

DDR4芯片的内部功能框图如下:

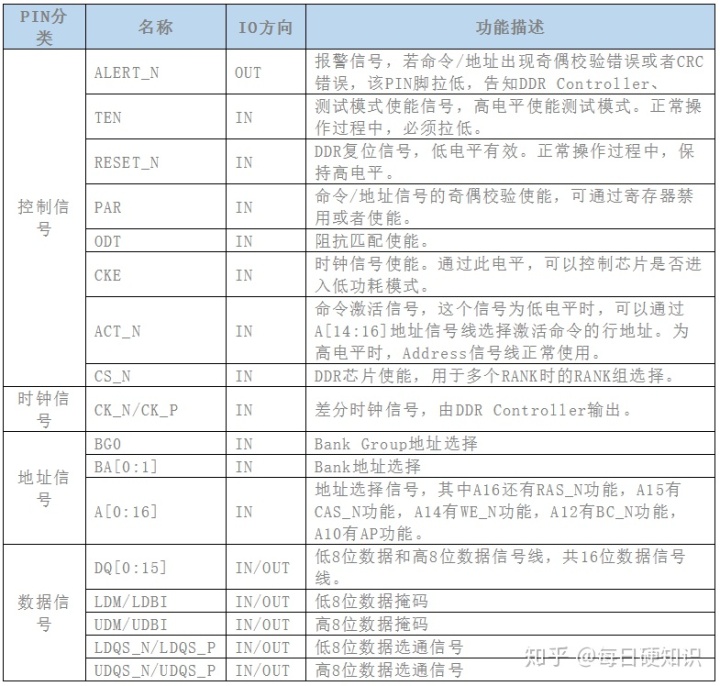

根据引脚的功能,它们可以分为7类:前3类是电源,接地和配置。

最后四类是:控制信号,时钟信号,地址信号,数据信号

电源,接地和配置信号的功能非常简单,因此在此不再赘述。控制信号主要用于完成DDR4和DDR4控制器之间的状态切换。

DDR4中最重要的信号是地址信号和数据信号。

如上所述,DDR4芯片具有20条地址线(17条地址,2条BA,1条BG)和16条数据线。在弄清这些信号线的作用以及地址信号为何具有多路复用功能之前,让我们首先提出一个问题。如果我们使用20条地址线和16条数据线来设计DDR,那么我们可以设计多少DDR寻址能力?

根据教科书中学习到的最简单的单行8421编码寻址方法,我们知道20条地址线(甚至不是读写控制信号)的寻址空间为2 ^ 20,并且16条数据线可以当一次传输16位数据时,我们可以轻松地计算出DDR芯片的最大存储容量为:

Size(max)=(2 ^ 20)* 16 = 1048576 * 16 = 16777216bit = 2097152B = 2048KB = 2MB。

但是实际上,DDR的最大容量可以为1GB,这是传统单行编码寻址容量的512倍。它是如何做到的?答案很简单,分时复用。

我们可以如下设计DDR存储空间:

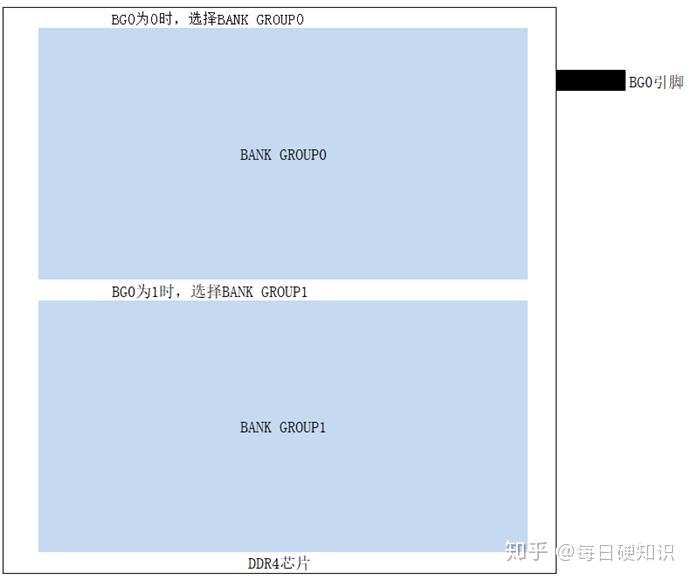

首先将存储空间分为两个大块,即BANK GROUP0和BANK GROUP1,然后使用1条地址线(剩余19条),命名为BG,然后进行编码。如果将BG拉高以选择BANK GROUP0,则下拉以选择BANK GROUP1。 (当然,您也可以将其分成4个大块,并使用2行进行编码)

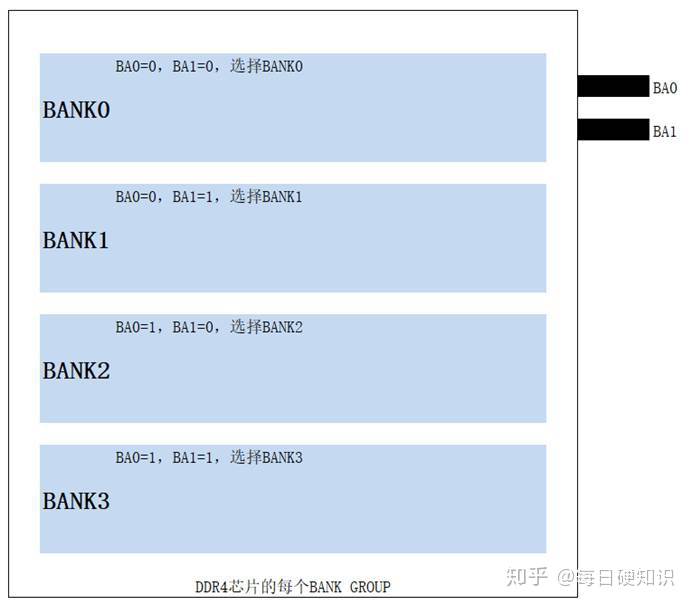

将1个BANK GROUP区域划分为4个BANK子区域,分别命名为BANK0、BANK1、BANK2、BANK3。然后我们挑选出2条地址线(剩余17条),分别命名为BA0和BA1,并对4个小BANK进行编码。

这时,我们将DDR内存颗粒划分为2个BANK GROUP,每个BANK GROUP分为4个BANK,总共8个BANK区域,并分配了3条地址线,分别称为BG0,BA0,BA1。那么我们还有17条信号线,我们应该如何设计每个存储体?这时,有必要使用分时复用的设计概念。

其余17行用于第一次代表行地址,第二次代表列地址。

最初,当地址发送一次时,数据发送一次,并且寻址范围最大为16KB(不读取或写入信号)。

现在将其修改为两次发送地址。数据传输一次后,寻址范围最大扩展到2GB。尽管数据传输速度降低了一半,但存储空间却扩大了很多倍。这是需要改进的地方。

因此,对于其余的17条地址线,保留1表示传输地址是否为行地址。

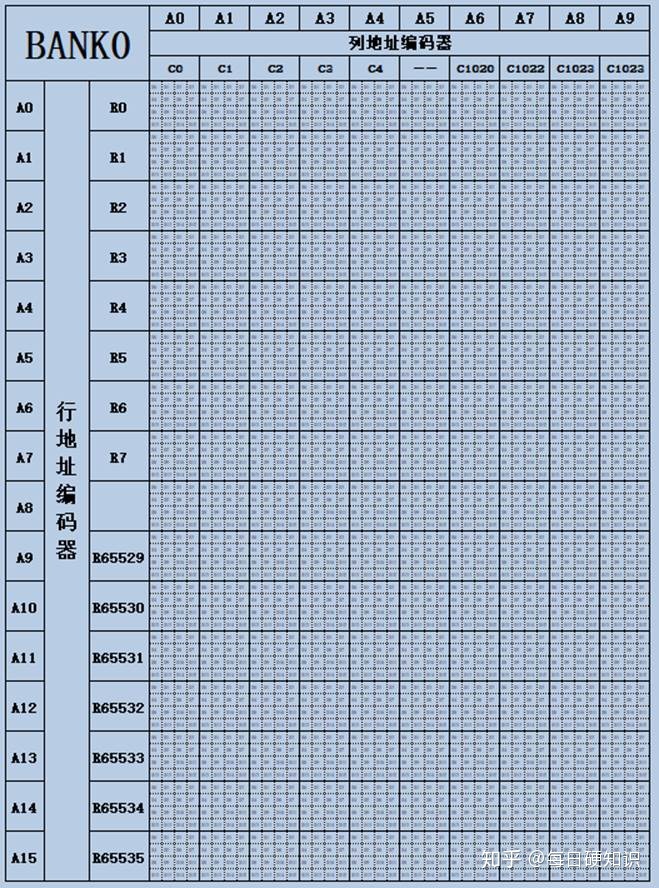

在第一次传输中,启用了行地址选择,并且保留了16条地址线,它们可以指示行地址范围。您可以轻松地将行地址范围计算为2 ^ 16 = 65536 = 64K。

在第二次传输中,禁用行地址选择,保留16条地址线,保留10条列地址线以指示列地址范围,可以轻松表示的列地址范围为2 ^ 10 = 1024 = 1K ,其余6个用于表示读/写状态/刷新状态/锻炼功能等复用功能。

这样,我们可以将1个BANK划分为67108864 = 64M个地址。如下图所示:

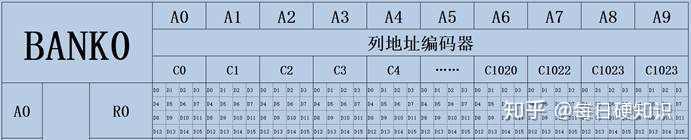

在每个地址空间中,我们使用所有16条数据线来一次存储16位数据。

所以1个BANK可以分为65536行,每行有1024列,每个存储单元为16位。

每行可以存储1024 * 16bit = 2048bit = 2KB。每行的存储容量称为“页面大小”。

单个存储区有65536行,因此每个存储区的存储容量为65536 * 2KB = 128MB。

单个BANK GROUP具有4个BANK,每个BANK GROUP的存储容量为512MB。

单个DDR4芯片具有2个存储组,因此单个DDR4芯片的存储容量为1024MB = 1GB。

到目前为止,所有20条地址线和16条数据线均已分配。我们以正向设计的思维方式解释了DDR4的存储原理,接口定义和寻址方法。

在下一部分中,我们将说明DDR4的详细工作原理和硬件设计步骤,以及调试时需要注意的参数以及DDR4的SI仿真。

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/shoujiruanjian/article-342653-1.html

- gotomycloud怎么用?gotomycloud注册?GoToMyCloud如何使用

- 凯立德2012夏季版?凯立德导航怎么升级?2016凯立德最新车载版?2012最新凯立德夏季版2921J0B下载

- youku free download?photo funia相册编辑?趣味照片合成(PhotoFunia)3.5.6去

- 8684公交数据包?8684离线版下载?8684公交下载?苏州8684公交查询

- 【灵信宝商务版客户端】灵信宝商务版客户端

- 灵信宝商务版_尽管太阳神孔蒂拉雅维拉科查是世间万物的创造

- 苹果6储存容量几乎已满?苹果4存储容量几乎已满?解决iphone“ 存储容量几乎已满”的办法

- 小雨伞下载?韩娱之幸福小雨伞女主?小雨伞法?小雨伞 v8.2.0.48 免费绿色版下载

历史上最昂贵的英特尔CPU出现了:28核Xeon处理器每个售价高达8.140,000元

历史上最昂贵的英特尔CPU出现了:28核Xeon处理器每个售价高达8.140,000元 解决无法读取内存的问题的解决方法

解决无法读取内存的问题的解决方法 解决方案:32位win2003 / 2008企业版支持4G以上内存的设置方法

解决方案:32位win2003 / 2008企业版支持4G以上内存的设置方法 非常给力:使用最强的游戏机安装自己的计算机三款ASUS主板购物指南

非常给力:使用最强的游戏机安装自己的计算机三款ASUS主板购物指南

时代不同了