CPU中的L1,L2和L3缓存之间的区别:缓存如何工作?

电脑杂谈 发布时间:2020-09-10 06:07:03 来源:网络整理

每个现代处理器都有少量的缓存。在过去的几十年中,缓存体系结构变得越来越复杂:CPU缓存级别已提高到三个级别:L1,L2和L3,每个块的大小都增加了,并且缓存关联性也发生了一些变化。

但是,在我们深入研究细节之前,让我问您,什么是缓存,为什么需要它?另外,现代处理器包括L1,L2和L3高速缓存。这些缓存级别之间有什么区别?

缓存和系统内存:SRAM和DRAM

高速缓存基于更快(且更昂贵)的静态RAM,而系统内存则使用较慢的DRAM(动态RAM)。两者之间的主要区别在于,前者由CMOS技术和晶体管(每个模块六个)制成,而后者则使用电容器和晶体管。

DRAM需要不断刷新(由于泄漏),以将数据保留更长的时间。因此,它消耗的功率明显更多,并且速度较慢。 SRAM不需要刷新,效率更高。但是,较高的价格阻碍了主流技术的采用,从而限制了其在处理器缓存中的使用。

在处理器中缓存的重要性?

现代处理器要比其1980年代和1990年代初的原始处理器亮几年。如今,高端消费类芯片的运行频率超过4GHz,而大多数DDR4内存模块的额定频率都低于1800MHz。结果,系统内存太慢,无法在不严重降低其速度的情况下直接用于CPU。这是缓存的来源。它充当两者之间的中介,存储重用的小数据,或者在某些情况下,存储这些文件的内存地址。

L1,L2和L3缓存:有什么区别?

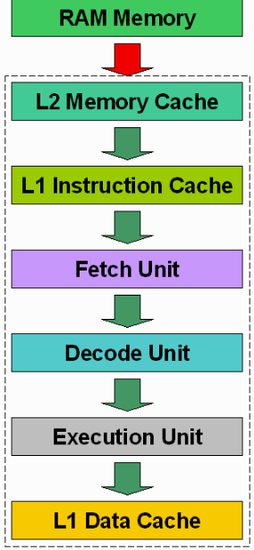

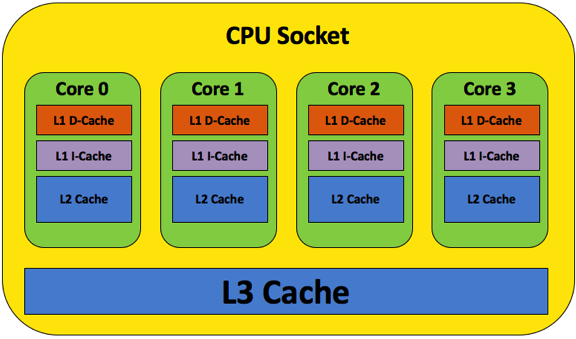

在现代处理器中,按照大小增大和速度减小的顺序,高速缓存存储器分为三个部分:L1,L2和L3高速缓存。 L3高速缓存是最大和最慢的(第三代Ryzen CPU具有高达64MB的大型L3高速缓存)高速缓存级别。 L2和L1比L3小得多,而且速度更快,并且每个内核都是分开的。早期的处理器不包括三级L3缓存,并且系统内存直接与L2缓存交互:

L1缓存进一步分为两部分:L1数据缓存和L1指令缓存。后者包含需要由CPU执行的指令,而前者则用于保存要写回主存储器的数据。

L1高速缓存不仅充当指令高速缓存,而且还保留预解码的数据和分支信息。此外,尽管L1数据高速缓存通常充当输出高速缓存,但是L1指令高速缓存的行为类似于输入高速缓存。循环时这很有用,因为所需的指令就在采集单元的旁边。

现代CPU可以为旗舰处理器提供高达512KB的一级缓存(每个内核64KB),服务器组件的功能几乎是其两倍。

L2缓存比L1大得多,但速度也较慢。旗舰CPU的大小为4-8MB(每个内核512KB)。每个内核都有自己的L1和L2缓存,并且L3缓存的最后一级在裸片上的所有内核之间共享。

L3缓存是最低级别的缓存。从10MB到64MB不等。服务器芯片具有高达256MB的三级缓存。此外,与竞争对手的英特尔芯片相比,AMD的Ryzen CPU具有更大的缓存大小。这是因为MCM设计可与Intel的Monolithic进行比较。

当CPU需要数据时,它首先搜索关联核心的L1高速缓存。如果找不到,则接下来搜索L2和L3缓存。如果找到了必要的数据,则称为缓存命中。另一方面,如果高速缓存中没有数据,则CPU必须请求将其从主存储器或存储设备加载到高速缓存中。这需要时间,并且可能会对性能产生不利影响。这称为缓存未命中。

通常,当高速缓存大小增加时,高速缓存命中率增加。在游戏和其他对延迟敏感的工作负载中尤其如此。

看看内存图

通过对缓存的基本描述,让我们讨论系统内存如何与缓存通信。这称为缓存或内存映射。高速缓存存储器分为块或组。这些块分为n个64字节的行。系统内存与高速缓存分为相同数量的块(组),然后将两者链接在一起。

如果您有1GB的系统RAM,则缓存将分为8192行,然后分为多个块。这称为n路关联缓存。使用2路关联高速缓存时,每个块包含2行,4路包含4行,8路包含8行,而16路包含16行。如果RAM的总大小为1GB,则内存中每个块的大小为512 KB。

如果您具有512 KB 4路关联缓存,则RAM将被分为2,048个块(1GB为8192/4)并链接到相同数量的4行缓存块。

以与16路关联缓存相同的方式,将缓存分为512个块,这些块链接到内存中的512个(2048 KB)块,每个缓存块包含16行。当缓存中的数据块用完时,缓存控制器将使用所需的数据重新加载一组新的块,以继续执行处理器。

N路关联缓存是最常用的映射方法。还有另外两种方法,称为直接映射和完全关联映射。在前者中,缓存行和内存之间存在硬链接,而在后者中,缓存可以包含任何内存地址。基本上,每一行都可以访问主内存的任何块。此方法具有最高的命中率。但是,其实现成本很高,因此芯片制造商通常会避免使用它。

哪个映射是最好的?

直接映射是最容易实现的配置,但同时效率最低。例如,如果CPU需要给定的内存地址(在这种情况下为1,00 0),则控制器将从内存中加载64字节的行并将其存储在高速缓存中(1,000至1,06 3)。将来,如果CPU需要来自同一地址或该地址之后的地址(1,000到1,06 3))的数据,它们将已经在缓存中。

当CPU在映射到同一高速缓存行的存储块中一个接一个地需要下一个地址时,这将成为一个问题。例如,如果CPU首先请求地址1,000,然后再请求地址2,000,则由于两个地址在同一存储块中(块大小为128 KB),将发生高速缓存未命中。另一方面,映射到它的高速缓存行是从地址1,000到1,063开始的行。因此,高速缓存控制器将在第一高速缓存行中将地址从行2000加载到2063,从而消除了较旧的数据。这就是为什么直接映射缓存是效率最低的缓存映射技术并被广泛放弃的原因。

完全关联映射在某种程度上与直接映射相反。内存缓存行和RAM内存位置之间没有硬链接。缓存控制器可以存储任何地址。以上问题不会发生。这种缓存映射技术是最有效的,并且具有最高的命中率。但是,正如已经说明的那样,这是最困难,最昂贵的实施。

结果,使用了一组完全关联映射和直接映射的混合关联映射。在这里,每个存储块都链接到一组线(取决于SA映射的类型),并且每条线可以保存来自映射存储块中任何地址的数据。在4路集关联高速缓存中,内存高速缓存中的每个集最多可容纳来自同一内存块的四行。使用16路配置时,该数目将增加到16。

当映射集上的所有插槽都用完时,控制器将弹出其中一个插槽的内容,并从同一映射存储块中加载另一组数据。例如,将组关联的内存缓存方式从4路增加到8路,每个组将具有更多可用的缓存插槽。但是,如果不增加高速缓存的数量,则每个链接的内存块的内存大小将增加。基本上,在不增加整体缓存大小的情况下增加集合缓存集上的可用插槽数量意味着,该集合将链接到更大的内存块,这由于刷新次数的增加而有效地降低了效率。

另一方面,增加缓存大小意味着每个集合中将有更多的行(假设集合大小也增加了)。这意味着每个内存块有更多数量的链接缓存行。通常,这会增加命中率,但是可以增加总数的限制是有限的。

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/shoujiruanjian/article-317752-1.html

-

-

刘村

刘村台湾若敢竖起台独旗帜

- gotomycloud怎么用?gotomycloud注册?GoToMyCloud如何使用

- 凯立德2012夏季版?凯立德导航怎么升级?2016凯立德最新车载版?2012最新凯立德夏季版2921J0B下载

- youku free download?photo funia相册编辑?趣味照片合成(PhotoFunia)3.5.6去

- 8684公交数据包?8684离线版下载?8684公交下载?苏州8684公交查询

- 【灵信宝商务版客户端】灵信宝商务版客户端

- 灵信宝商务版_尽管太阳神孔蒂拉雅维拉科查是世间万物的创造

- 苹果6储存容量几乎已满?苹果4存储容量几乎已满?解决iphone“ 存储容量几乎已满”的办法

- 小雨伞下载?韩娱之幸福小雨伞女主?小雨伞法?小雨伞 v8.2.0.48 免费绿色版下载

利用内存编写外挂的方法及技巧(一)_光明网

利用内存编写外挂的方法及技巧(一)_光明网 内存错误,详细教您应用程序错误,无法读取内存

内存错误,详细教您应用程序错误,无法读取内存 ddr3的主板 399元精英G41T-M6评测:DDR3内存更值得选择

ddr3的主板 399元精英G41T-M6评测:DDR3内存更值得选择 优化的解决方案:AMD cpu如何识别模型(适用于小白)

优化的解决方案:AMD cpu如何识别模型(适用于小白)

叙利亚等