至强CPU架构英特尔一次性宣布了六代新CPU架构! 10nm Xeon首次亮相

电脑杂谈 发布时间:2020-08-23 03:15:54 来源:网络整理

在美国当地时间12月12日,英特尔召开了一次技术交流会议,称为“架构日”. 不出所料,它宣布了每个人都期待的新CPU架构,并且一口气就能完成六次. ,还有新的GPU核心图形卡,3D堆叠芯片,内存存储,计算编程,深度学习等.

曾在AMD负责CPU和GPU设计的Jim Keller和Raja Koduri分别负责有关技术架构的说明. 加入英特尔之后,这也是他们第一次在重要活动中公开露面.

大神级别的吉姆·凯勒

让我们先谈谈CPU架构. 尽管英特尔处理器经过数十年的迭代更新,但它们本质上是Core微体系结构.

从2019年到2021年,英特尔将每年推出一个新的微体系结构. 尽管暂时无法确定它们是否本质上是Core微体系结构的延续和改进,但至少这些年来变化的幅度是空前的.

2019年的新结构为“阳光湾”(Sunny Cove),主要变化包括:

-单线程性能(只有这种小的体系结构更改肯定不小)

-降低功耗

-新增了减少延迟的算法

-提高可伸缩性并并行执行更多操作(也许支持更多核心)

-增加密钥缓冲区和缓存以优化以数据为中心的工作负载

-新功能可以加速诸如AI和加密之类的特殊计算任务

-针对特定用例和算法的体系结构扩展,例如用于提高加密性能的新指令,向量AES / SHA-NI,压缩/解压缩等.

它将使用10纳米工艺制造,并集成有第11代核显示器(在此处进行详细说明),并且相应的处理器代码是先前发布的“ Ice Lake”.

英特尔表示,Sunny Cove可以减少延迟,增加吞吐量,改善并行计算功能,并改善游戏,多媒体,数据和其他相关应用程序的体验. 它将成为下一代Core和Xeon处理器的基础架构. 这将是第二天晚上首次亮相.

英特尔还在现场多次展示了Sunny Cove. 其中之一运行7-Zip压缩和解压缩. 由于有了新的ISA指令集,它声称性能提高了75%.

另一个是Ice Lake-U,它具有15W的超低功耗水平,但是没有透露细节,并且演示环境仍然是一个工程开发平台.

2020年的新架构是“ Willow Cove”(Willow Cove),对缓存进行了重新设计(主要是第一和第二个缓存),对晶体管进行了优化(与制造工艺有关),并且有新的安全功能(也许硬件基本上不受融合/幽灵漏洞的影响).

它仍然应该是10nm制程,但肯定会像14nm +和14nm ++一样得到优化和改进.

2021年的新架构是“金海湾”(Golden Cove),它将继续改善单线程性能,增强AI,5G,网络,性能,并继续加强安全性.

该过程可能会持续到10nm或7nm.

以上是用于高性能平台的新体系结构,低功耗Atom也将具有三个连续的新体系结构,但步伐稍慢.

它们将出现在面向台式机和移动应用的超低功耗奔腾和赛扬处理器系列中.

2019年是“ Tremont”,它将提高单线程性能,网络服务器性能,降低功耗并延长电池寿命. 该过程可能是10nm.

2021是“ Gracemont”,它将继续提高频率和单线程性能,并增强矢量性能.

2023或更早版本的代号不确定. 这只是下山. 除了进一步提高单线程性能和频率外,还会有更多的功能,可能会发展到7nm.

最后,顺便说一句,这次宣布的六个代号全都指的是微体系结构. 特定的处理器产品将具有不同的代号. 例如,与Sunny Cove对应的台式机处理器是Ice Lake,并且它们是相关的. 不尽相同.

在架构日活动中,英特尔不仅展示了15W低功耗Ice Lake-U,而且还提出了一个庞然大物:

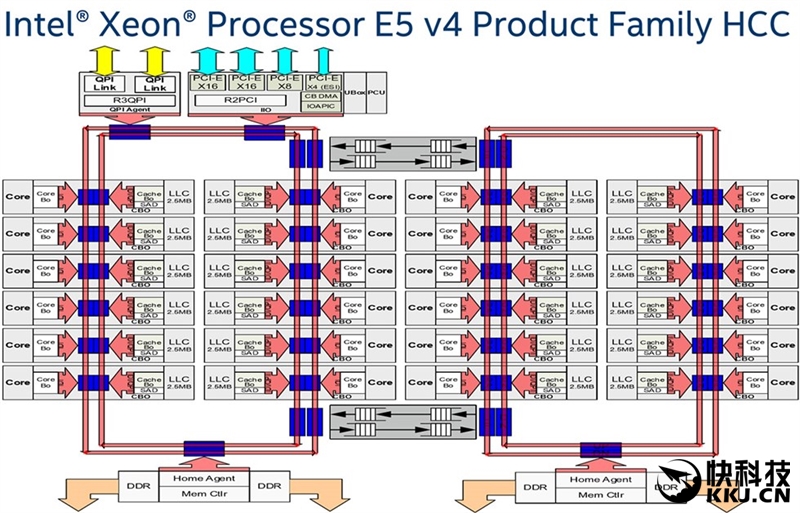

这是基于10nm工艺的Sunny Cove架构(代号Ice Lake-SP)的新一代Xeon Xeon处理器. 可以看出,整个散热顶盖被覆盖了,内部核心面积肯定不小,可能为350平方毫米. 甚至更多.

没有透露细节. 我相信核心数量将大大增加-当前的14nm Skylake-SP系列最多具有28个核心. 面对AMD EPYC系列,即使使用双芯片,当前的32核和下一代64核也确实不足. 集成包最多只有40个内核.

但是,考虑到Cascade Lake尚未发布并且服务器市场的更换速度要慢得多,Ice Lake-SP可能要到2020年初才能正式亮相.

英特尔创建Foveros 3D软件包: 不同工艺和芯片的共存

工艺越来越困难,芯片设计也越来越复杂,未来在哪里?作为行业领导者,英特尔在设计新的CPU和GPU架构和产品时也提出了一个新的,更灵活的想法.

在“架构日”活动中,英特尔展示了一种称为“ Foveros”的全新3D芯片封装技术. 首次引入了针对CPU处理器的3D堆叠设计,该设计可实现将芯片堆叠在芯片上并集成不同的流程,结构,相关产品将于2019年下半年推出.

英特尔表示,这项技术提供了极大的灵活性. 设计人员可以以新产品形式“混合和匹配”不同的技术专利模块,各种存储芯片和I / O配置,并使产品可以分解为较小的“芯片组合”.

英特尔首先回顾了近年来发展新工艺的困难,特别是对于高性能计算芯片. 14nm工艺已经使用了四年,这在过去是无法想象的.

但是,英特尔不仅每一代都有一个过程,而且针对不同目的的芯片(例如I / O芯片组)的不同优化实际上也在不断发展.

对于下一代工艺计划,英特尔将其分为三个层次. 首先是用于计算的1274 10nm工艺,随后将优化到1274.7、1274.12(10nm +,10nm ++)和I / O的1273. 新的Foveros设计P1222,短期内无需进一步优化.

未来,该计算芯片将进入1276年7纳米制程,IO和Foveros也将同时发展. 至于未来的1278计算芯片技术,仍在探索中,它应该对应5nm而不会发生意外.

英特尔表示,不同用途的芯片或功能模块对晶体管密度的要求完全不同,性能,功耗和成本也有很大差异. 因此,所有使用相同工艺的芯片模块都无法达到最佳效果,尤其是新技术越来越难,而且不值得,而且做起来也越来越难.

英特尔先前已推出EMIB(嵌入式多芯片互连桥)2D封装技术. 为此,典型的产品是集成了AMD Vega GPU图形核心的Kaby Lake-G处理器.

Foveros升级为3D封装,将多芯片封装从单平面更改为三维组合,这大大提高了集成密度,并使不同芯片或功能模块的组合更加灵活.

这是3D Foveros 3D封装的结构: 底部是封装基板,底部放置有底部芯片(Bottom Chip),它起到了Active Interposer-AMD Fiji / Vega的作用核心集成封装HBM视频存储器也存在类似的情况.

插入器上可以放置各种新产品或模块,例如CPU,GPU,内存,基带...

插入器中有大量的TSV 3D硅通孔,用于连接上下焊料凸点(Solder Bump),使上芯片和模块与系统的其他部分通信.

目前,英特尔已经拥有Foveros芯片的样品,并表示已准备好量产. 英特尔将在明年推出第一个产品,上面的这个小家伙,英特尔称其为“混合x86处理器”(Hybrid x86 CPU).

这种小芯片的长度和宽度仅为12×12毫米,高度仅为1毫米. 它不像那么大,但是内部3D堆栈封装了多个模块.

在基板上是具有低成本和低泄漏的P1222 22FFL(一种22nm工艺类型)IO芯片.

顶部是P1274 10nm工艺计算芯片,它是传统的CPU,集成了Sunny Core高性能内核和四个Atom低功耗内核(也许是新的Tremont架构).

甚至还有PoP集成存储芯片.

英特尔声称其待机功耗仅为2mW,即0.002W,最大功耗不超过7W. 显然,它是针对移动平台的,不需要风扇,但是没有说明特定的目标设备.

让我们看一下该处理器的内部组成: 右上角是具有专用0.5MB MLC中间高速缓存的单个Sunny Cove CPU内核,左上角是具有四通道4的LPDDR4X控制器. ×16位的位宽. ,以及四个小型CPU内核,共享1.5MB二级缓存.

中间是4MB的最终级缓存,下面是第11代核显示器(64个EU单元)的低功耗版本,11.5代显示控制器,DisplayPort 1.4控制器和其他各种模块

但是,现场演示原型平台上还使用了一个小型风扇. 此外,您还可以看到PCI-E M.2接口,UFS闪存和几个SIM连接器. 英特尔是否要重新进入手机处理器?

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/shoujiruanjian/article-304874-1.html

- gotomycloud怎么用?gotomycloud注册?GoToMyCloud如何使用

- 凯立德2012夏季版?凯立德导航怎么升级?2016凯立德最新车载版?2012最新凯立德夏季版2921J0B下载

- youku free download?photo funia相册编辑?趣味照片合成(PhotoFunia)3.5.6去

- 8684公交数据包?8684离线版下载?8684公交下载?苏州8684公交查询

- 【灵信宝商务版客户端】灵信宝商务版客户端

- 灵信宝商务版_尽管太阳神孔蒂拉雅维拉科查是世间万物的创造

- 苹果6储存容量几乎已满?苹果4存储容量几乎已满?解决iphone“ 存储容量几乎已满”的办法

- 小雨伞下载?韩娱之幸福小雨伞女主?小雨伞法?小雨伞 v8.2.0.48 免费绿色版下载

![解决方案:CPU风扇的智能调速[如何设置]](http://www.pc-fly.com/uploads/allimg/20201220/1608455189972_lit.png) 解决方案:CPU风扇的智能调速[如何设置]

解决方案:CPU风扇的智能调速[如何设置]![如何查看主板型号?理解[图形]的三种方法](http://www.21ic.com/d/file/201210/40dc9db2337cbcb5bd1aebab67de672f.jpg) 如何查看主板型号?理解[图形]的三种方法

如何查看主板型号?理解[图形]的三种方法 为什么6GB的运行内存在实际使用中甚至没有3GB?原因就在这里!

为什么6GB的运行内存在实际使用中甚至没有3GB?原因就在这里! 如何在cpu上涂硅胶如何涂才好,下面就让答

如何在cpu上涂硅胶如何涂才好,下面就让答

而缩头缩脑只能招来更多的侵略