反射型内存网络集线器的设计与研究

电脑杂谈 发布时间:2020-08-22 11:14:04 来源:网络整理

文章编号: 1671—4598I 2015)04—1323—04中文图书馆分类编号: TP23文件标识代码: 反射式存储器网络集线器的设计与研究张秀雷,付宇,周强,王玉龙(北京大学,北京大学航空航天工程学院,自动化科学与电气工程学院,北京100191)摘要: 现有的星形反射式存储网络集线器仍以高速数据选择器为核心设备. 其实质是形成一个具有连接节点的环形拓扑结构的反射式内存网络,这是不正确的. 顶部为星形拓扑;针对这个问题. 本文设计并实现了一个真正的星形拓扑反射式内存网络集线器,该集线器可以通过快速以太网进行配置,并且可以在数据传输过程中实时监控性能指标;集线器采用FP(i A)与8通道高速串行/并行/并行-串行转换芯片架构,实现了连接到集线器的节点的星形拓扑结构,具有良好的并行处理能力,并提高了网络数据映射率关键词: 反射式存储器网络;集线器;星形拓扑;数据映射Des gnand反射式存储器网络的研究张Research等,付宇,关键词: 反射式存储器网络;集线器;星形拓扑;数据映射周强,王玉龙(中国科学院自动化科学与工程学院,北京航空航天大学,北京100l 91)摘要: Theexi sti ngrefl ecti vememorynetwork hub is sti bu b lt lt with ghspeed muhi请注意,它是核心组件. 并且,它本质上是用于连接拓扑反射存储网络的连接节点. 从某种意义上讲,这是一个重要的技巧. 因此,本文的主题是纸张设计和开发反射的真实意义内存网络集线器,它可以被配置和真实的-通过以太网实现对数据传输性能的实时存储. 该集线器使用了具有8通道高速高速FPGA的FPGA. 在通过集线器连接的节点上实现的结构是一个标准的拓扑结构. 该集线器具有良好的并行处理能力,并改善了网络数据速率的映射. 最后,通过实验验证了稳定性.

在轮毂上放松和放松. 关键字: ref veve vememory网络;枢纽;星白杨数据映射简介反射存储网络是基于高速共享存储技术的实时网络. 它主要由反射存储节点卡组成,这些反射存储节点卡通过传输介质(例如光纤或同轴电缆)连接以形成网络. 它可以在异构总线结构和操作系统之间以确定的速率实时地逐个传输数据. 反射内存网络大多以星形或环形模式联网. 环形模式的特征在于使用光纤传输介质以菊花链方式连接网络中的每个节点. 数据从一个节点发送到下一个节点,并接收数据. 处理完数据后,该节点将继续将其发送到下一个节点,依此类推,直到数据返回到原始节点[2j. 环形反射存储网络的优点是整个网络不需要额外的集线器资源,并且所用光纤的数量比星形结构的数量少大约一半,并且成本非常低. 3.缺点是,当环形网络中的某个节点发生故障时,整个反射式内存网络将瘫痪. 在半物理模拟测试系统中,它可能会对产品产生不可估量的影响. 星型连接使用集线器作为数据. 在转发设备之后,网络中的每个节点首先将数据传输到集线器,然后集线器将对数据进行相应的处理,然后将其同时转发到其他节点.

使用集线器,可以实时监视数据流,可以绕过错误节点,并且可以大大减少数据更新时间. 但是,当今出现的数字集线器实际上表现出星形特征,但是实际的数据传输过程仍然使用环形传输技术. “”. 真正的意义. 收件日期: 2014-12-30;修订日期: 2015〜02-06. 作者简介: 张秀雷(1985年),男,山东人,硕士,实验家,主要从事测控,仿真网络方向的研究. 关于星形结构反射式内存网络集线器的报道很少. 1伪星型枢纽分析. 目前,反射式存储器集线器主要由GE FANuc的反射式存储器网络集线器(ACC-5595和HUB-5595)垄断. 两个集线器均由核心板和AC / DC DC电源组成. ,其中,核心板还包括: 1)SFP光纤收发模块; 2)同步检测单元: 自动检测是否连接了外部节点板; 3)高速模拟量2合1数据选择器模块(MUX); 4)状态和控制模块: 实现外部节点板的级联和自动旁路,形成一个循环反射存储网络. 尽管由这种集线器形成的反射式存储器网络拓扑看起来像一个“星形网络”,但它实际上是由高速模拟开关组成的. 环形网络实际上是一个伪星形结构'7. 它具有一定的优势: 它可以绕过故障节点,一个节点故障不会导致整个网络瘫痪. 它可以自动检测端口是否连接到节点板上,具有一定的优势. 聪明.

但是,该伪星反射存储网络仍然存在大数据延迟的问题. 针对这一问题,本文设计并实现了一个真正的星形反射式存储网络集线器. 2集线器硬件设计2.1集线器的总体结构设计集线器的功能结构原理如图1所示. 反射存储网络集线器的系统结构主要包括以下部分: 1)可编程逻辑模块(FPGA). 整个系统的控制中心. 2)串行/并行-串行转换模块. 与FPGA的完整数据交换. 万方数据: !!!: 跌出身体形状,量出盛形!! 3)检测. 4)5)电源. 图1集线器的功能结构光纤模块. 将光转换为电. 并进行端口有效性以太网控制模块. 与主机的数据传输. DC-DC电源模块. 为整个系统提供可靠稳定的电力. 6)状态指示,配置和其他辅助电路. 提供必要的辅助功能,以使系统稳定运行. 发送和接收数据时,从某个节点卡的TX端发送数据,然后通过集线器上的光电转换模块将高速光信号转换为高速串行电信号,然后再将串行-并行转换芯片将被发送数据被转换为并行数据并发送到FPGA进行处理. 最后,FPGA以广播的方式发送到连接到节点卡的其他通道,以实现真正的反射式存储网络星形拓扑. 2.2核心芯片的选择2.2.1光纤的选择在反射式存储网络中,信息以二进制0或1的形式表示,用于在不同节点之间以光功率调制的形式进行高速数据传输,而可编程逻辑模块则用于识别和识别. 处理是电信号,因此网络中的每个节点都必须具有光电转换设备[8].

Finisar选择的模型是FTI,该模型被广泛使用并且在技术上更加成熟. F851 9P2BNL模块,此模块尺寸较小,数据双向传输速率高达2. 125 Gb / s. 2.2.2串行/并行转换器的所选数据以串行方式在光纤中传输. 光纤转换光电信号后,获得获得的串行电平信号,并且集线器中的FPGA以更高的效率处理并行数据,在数据进入FPGA内部缓冲器之前,需要进行串行到并行转换[9]. 当集线器传输数据时,并行数据将转换为串行数据并通过光纤发送到其他节点. 选择TLK2501串行/解串器模块作为集线器的主要数据转换模块. 2.2.3可编程逻辑模块选择集线器的控制器采用可编程逻辑器件FPGA来实现. 综合考虑I / 0资源的数量,系统的功耗和成本,最终选择了Altera Cycl one IIl系列的EP3C120F780C8N芯片作为主控制器. FPGA具有大量的逻辑资源和内存,并封装在BGA中,可以满足主控制器集线器的各种性能要求. 2.2.4以太网模块集线器的以太网接口模块选择更常用的HR911105A. 与HR911105A连接的是DM9000A型的10M / 100M自适应以太网接口芯片,支持3.3V和5V电压电源,并具有独立于介质的接口,低功耗,全双工通信模式和内部寄存器上的命令操作(以字节为单位) ,单词和双词.

2.3集线器PCB板设计整个集线器PCB板采用8层板结构,从顶层到底层是信号层,接地层,信号层,电源层,电源层,信号层,接地层,信号层. 其中,TLK2501和FPGA通过高速并行总线,时钟为106. 25 MHz,带宽为16位,并且在布线过程中采用等长设计以确保信号完整性. 此外,TLK2501与SFP模块之间的高速线路的传输速率高达2.125 Gb / s,并且在布线过程中采用了等长阻抗设计. 差分线的线宽和间距经过专门设计,可满足单端50 n和差分100 n的要求. 特性阻抗要求可确保电磁兼容性和信号完整性. 经过程序演示,组件选择,PCB板布线至板级调试后,最终的PCB板部分如图2所示. 图2集线器PCB部分图3集线器固件设计在集线器固件设计和开发过程中,整个系统分为模块. 整个系统分为TLK250l数据接收和发送,以太网控制,操作参数收集,数据接收和发送FIFO,数据CRC检查,接收和发送以及故障状态显示等模块. 3.1数据收发FIFO缓冲区设计TLK2501和FPGA进行数据传输时,有必要设计数据收发缓冲区,以确保数据处理的同步性. 当反射存储卡以双字传输数据时,TLK2501以字传输数据时,在设计FIFO时有两种类型: FIFO被设计为32位写入和32位读取,深度为l 024;接收FIFO设计用于16位写入和32位读取,深度为16384.

3.2数据发送模块TLK2501与光电模块之间的数据传输完全由硬件独立完成,FPGA程序主要处理TLK2501之间的数据传输方法. 通道发送模块状态机如图3所示. 万方数据第4期张秀磊等: 反射存储网络集线器的设计与研究·1325·传输完成图3通道发送模块状态机模块已初始化,状态机处于空闲空闲状态,在每个CTX-CLK时钟的上升沿,模块将检查发送FIFO中是否有数据,如果没有数据,它将等待一个时钟周期,然后继续查询. 如果FIFO中有数据,则IDLE空闲状态会将TX-EN设置为高电平,并在时钟的下一个上升沿将其设置. 状态机执行“发送就绪”状态以准备初始数据传输,即读取FIFO数据中的32位. 将低16位发送给TLK2501后,继续检查FIFO中是否有数据. 如果不是,则进入“发送最后一个”状态,并将32位数据的高16位发送到TLK2501;否则,发送TLK2501. 如果有数据,请进入“发送数据”状态. 3.3数据接收模块接收到通道中其他节点发送的数据后,由光电转换模块和TLK2501进行串并转换. 保存到TLK2501的接收FIFO中. FPGA不需要为TLK2501提供额外的接收时钟. TLK2501的时钟修复功能可以从串行端口接收的数据流中恢复远程发送节点的发送时钟,并与内部时钟同步作为接收时钟.

TI的

FPGA. K2501接收缓冲区中的读数完全是被动的. 也就是说,FPGA只需要设置相应的接收FIFO. 并将通讯引脚设置为TLK2501,TLK2501会自动将数据写入接收FIFO,程序仅需判断接收FIFO是否为空即可直接处理数据. 3.4以太网控制接口模块以太网控制模块主要实现接收和保存上位机发布的集线器配置指令,并上传集线器的工作状态和各端口的运行参数数据. 这些功能主要分为DM9000A初始化,数据查询功能,数据读取功能和数据上传等操作. 模块从主机计算机发送数据时. 首先将6字节的目标MAC地址写入寄存器MWCMD,然后写入6字节的集线器MAC物理地址,然后将要发送到寄存器FCH和FDH的数据长度写入(FCH为16位高8位数字). 最后,写入要发送的数据,并将发送寄存器TCR的第一个位置设置为高电平. DM9000A将自动封装数据头和帧头,并在将数据发送到主机之前执行CRC检查. 在DM9000A接收数据的过程中,如果CRC校验正确,则数据将存储在类似于FIFO的接收缓冲区中. 每个数据帧都有一个4字节的标头,后跟有效数据. 最后是CRC校验码. 帧头4字节的含义如表1所示. 表1DM9000A接收到的数据帧头格式地址偏移量00H01H02H03H名称01H帧状态长度低字节长度高字节4主机软件设计跨平台作为反射特性之一内存实时网络,使得状态监控主机程序也应具有跨平台操作的特点.

该设计使用J AVA作为主要开发语言,使用以太网作为主要通信工具,并且该应用程序可以在装有J AVA虚拟机平台的任何操作系统上运行. 本文使用Ecl ipse作为开发IDE和Wi. ndowBui der插件创建了一个接口来提高工作效率,并使用UDP通信作为主要数据传输协议. 该软件必须实现对反射存储器网络通信状态的完整实时检测,并且主要完成以下功能: 1)集线器配置. 包括集线器操作模式和控制每个端口的操作启用. 2)系统状态. 完整显示当前网络的工作状态,工作模式,使用的端口数,与以太网相关的通信IP和端口以及其他参数. 3)端口运行状态. 主要显示集线器每个端口的工作模式和状态,包括端口号,节点ID,端口状态,发送和接收的数据总量,该节点的存储范围,帧错误数,中断发送位置和数量,端口用法参数,例如失败率和失败率. 4)运行状态信息. 当前的工作状态详细信息主要以文本滚动方式显示. 上位机软件操作界面如图4所示. . : t藿考黼1i二t●■^图4上位机软件操作界面图该界面主要包括菜单栏,系统状态和参数配置,端口运行状态和运行状态详细信息,可以在反射式内存网络运行期间直观地显示各种状态参数.

5集线器性能测试的测试计划是这样一个过程,其中网络中的所有节点都在多个周期中写入不同的地址并验证写入的数据. 关键是测试系统在长期高负载大数据操作下是否能够保证数据传输的正确性和各种类型数据帧的完整性. 首先,不要使用集线器. 选择8个反射性存储卡,这些存储卡稳定可靠地工作,以形成一个环形网络,每个存储卡具有256 M内存,并进行数据穿越测试. 测试周期至少为1,000. 同时,记录每个数据包的传输时间延迟. 取所有测试的平均值. 此处,静态数据包长度用于计算,即数据的每一帧仅包含一个地址. 并在表2中输入计算出的误码率. 使用在先前测试中测试的8张反射式存储卡连接到集线器,以形成星型网络并执行数据遍历测试. 测试至少1,000个主要周期,并将计算出的误码率写入表3. Wanfang Data·1326·计算机测控量23表2纯环网每个节点的误码率分析表序列号块Err0ErrlErr2Err3Err4Err5Err6Err7延迟11 6 K

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/shoujiruanjian/article-304388-1.html

-

-

贾轶

贾轶央行降息不考虑物价上涨因素吗

-

张泽洋

张泽洋思路真的是太清晰了

- gotomycloud怎么用?gotomycloud注册?GoToMyCloud如何使用

- 凯立德2012夏季版?凯立德导航怎么升级?2016凯立德最新车载版?2012最新凯立德夏季版2921J0B下载

- youku free download?photo funia相册编辑?趣味照片合成(PhotoFunia)3.5.6去

- 8684公交数据包?8684离线版下载?8684公交下载?苏州8684公交查询

- 【灵信宝商务版客户端】灵信宝商务版客户端

- 灵信宝商务版_尽管太阳神孔蒂拉雅维拉科查是世间万物的创造

- 苹果6储存容量几乎已满?苹果4存储容量几乎已满?解决iphone“ 存储容量几乎已满”的办法

- 小雨伞下载?韩娱之幸福小雨伞女主?小雨伞法?小雨伞 v8.2.0.48 免费绿色版下载

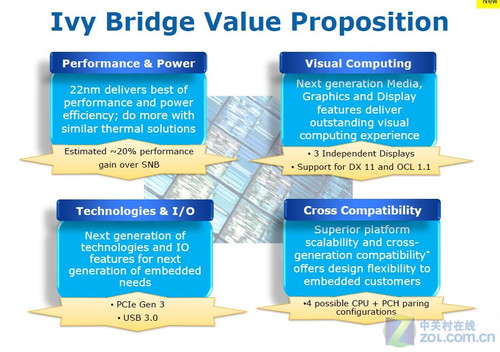

好戏还在后面吗?英特尔7系列芯片组深入解释

好戏还在后面吗?英特尔7系列芯片组深入解释 手机的ROM和RAM是什么?

手机的ROM和RAM是什么? 汽车CPU风扇33233323怎么办?3323步骤详解!

汽车CPU风扇33233323怎么办?3323步骤详解! 科学讲座-Intel CPU命名规则

科学讲座-Intel CPU命名规则

还是写长微博吧最