从另一个角度看电压. 显卡电压能耗平衡分析

电脑杂谈 发布时间:2020-08-02 17:09:54 来源:网络整理

1位英雄或元凶?

太平洋仍然是“太平洋”,黄石公园的冬天仍然很安静,小行星也无意降落到地球上……尽管这个世界的和平使一些意想不到的人感到失望, “世界的尽头”确实是我们在我们周围悄悄地漂流了. 随着世界末日的过去,我们可以松一口气,似乎能够拿起世界末日之前未完成的一些事情,例如: 您还记得我们所做的显卡电压和功耗之间的关系吗?一起在世界末日测试吗?

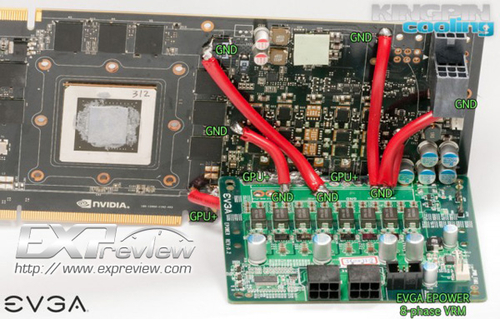

在上周的测试中,我们向您展示了在不同电压设置下具有相同负载和相同频率的图形卡的功耗差异很大. 我们选择的测试游戏和图像质量设置没有改变,并且测试场景基本上遵循准确性和可重复性的原则. 有理由认为,只要频率保持相同,这样的测试过程就不会带来太大的干扰. 但是测试结果有些出乎意料. 我们只是调整了核心电压参数,在相同负载和频率下的显卡显示出巨大的功率差距,甚至接近40%.

“上水”冷却问题并不是每个人都主动做出的选择.

实际上,每天在DIY圈子中都会重复类似的测试结果. 较低电压的芯片一直是“节能控制器”追求的目标,但是电压显然不仅是能耗的罪魁祸首. 罪魁祸首就是这么简单. 这对芯片意味着什么,哪些因素导致了高功耗的出现,我们应如何处理并尽可能减少电压的负面影响?您知道这些问题的答案吗?

“现在转到图形卡并转到“ |”以查看今天的最新文章“

“图形卡精彩图片摘要”

2电子的脏灵隧道效应

●电子的脏灵隧道效应

半导体与常规导体不同. 用我们每天看到的功耗=电压x电流的简单公式来解释半导体电压与功耗之间的关系是不正确的. 实际上,在频率(即开关动作的数量)保持不变的前提下,影响和产生电压功耗的最重要因素是我们熟悉但有些陌生的半导体芯片的重要问题泄漏. 要了解泄漏和电压之间的关系,我们可能首先需要研究一些量子力学方面的小型科学.

量子世界中基本粒子的图片

量子力学是一个神奇的领域. 在这个领域,“存在”和“位置”都不是真实的. 例如,当我们理解电子事物时,首先要丢弃“它在哪里”和“绝缘子不会让它通过”这两个概念. 在量子力学世界中,只要电子的势能达到一定水平,即使存在宏观非导电性,它也有可能从其原来的位置消失并出现在它想要出现的任何位置. 前面的绝缘材料. 事实也是如此,因此从宏观上讲,“绝缘子在破坏性击穿之前不会导电”似乎是绝对的事情,而在量子世界中似乎不是绝对的. 半导体芯片中的电子通常从绝缘层内部附近的位置消失,然后出现在绝缘层外部几纳米到十纳米的地方. 该过程不会破坏绝缘层本身的结构. ,因为此过程看起来像电子已经通过绝缘子形成了隧道,所以将其称为隧道效应.

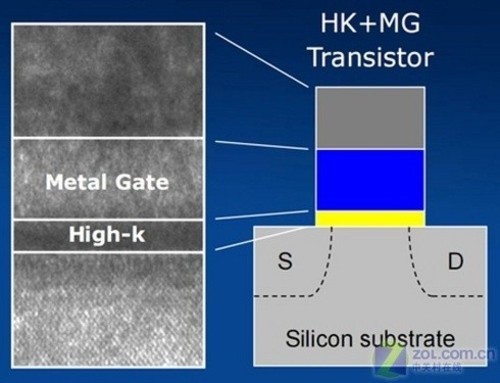

电子穿透绝缘子的隧穿效应

隧道效应充分体现了量子世界的魔力. 电子不再是真实的存在. 它变成一个怪人,可以调皮地消失,然后出现在意想不到的地方. 该效应对于许多应用领域都具有重要的作用和意义,但是对于半导体工业来说,隧穿效应已经使电子变成了彻头彻尾的“顽童”. 伴随着隧穿效应,电子可以从栅极内部的栅极氧化物层逸出到硅衬底的外部. 一旦到达这里,电子的行为就不再受人控制. 行进和与之相关的感应电流形成了我们熟悉和讨厌的东西.

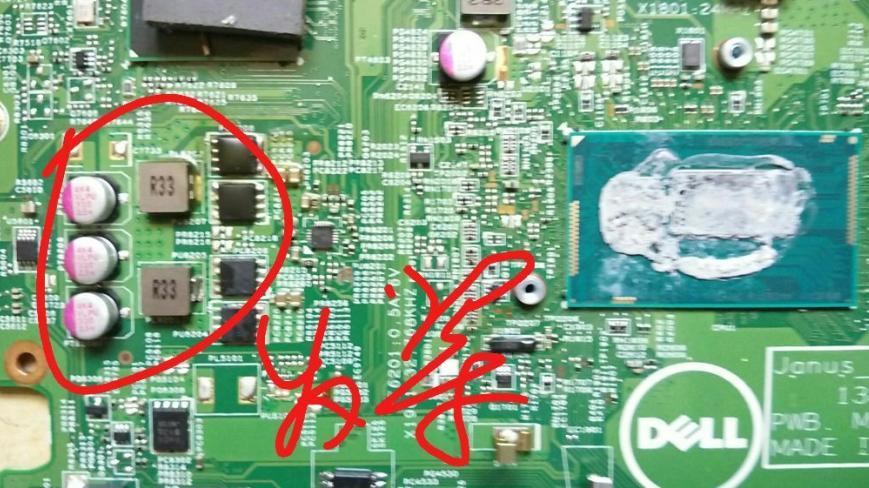

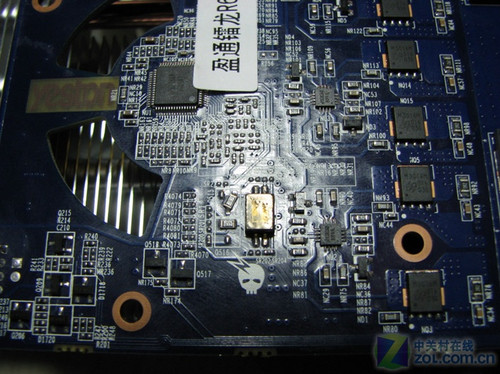

区域是绝缘但破裂的栅氧化层

泄漏是进入深亚微米障碍后困扰半导体行业的核心问题之一. 它对芯片的工作没有意义,但这是完全不可避免的. 当划线的宽度继续下降时,随着整个栅极尺寸的减小,栅极下方的栅极氧化物层的厚度/等效厚度(EOT)将继续变薄. 这种厚度的减小使栅极氧化物更薄. 该层容纳电子的能力迅速衰减. 隧道效应是反距离效应,距离越长,发生的可能性越低. 结果,在技术日趋完善的时候,电子比过去更容易完成从一侧消失然后在另一侧出现的过程. 此过程背后的驱动力是电压.

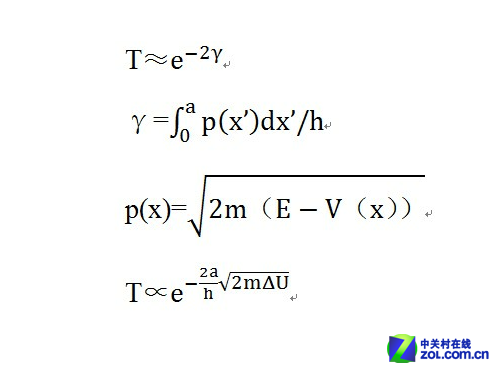

隧道效应概率问题的研究公式

上面看似“鬼影符号”的一组公式来自薛定inger方程的扩展和推论. 它描述了隧穿的可能性,T是该可能性的值. 我们无需担心难以理解的中间过程,我们只需要掌握对我们有用的关键点,即隧穿的概率与电子势能与电子势能之间的差近似成指数比例. 绝缘体,电子的势能通常与电压成正比. ,因此我们可以得出这样的结论: 电子隧穿和泄漏的可能性几乎受电压的指数影响. 我们甚至可以用“莫名其妙的决定”得出一个更简单的结论-只要稍微增加电压,与操作无关的泄漏电流就会“摆动”,并且芯片的功耗相同负载和相同的频率将随波逐流.

3电压有害还是有害?

●电压有害吗?

电压确实是一种使我们充满爱与恨的存在. 它将加剧电子的“顽固性”,使电子更容易越过绝缘层并形成泄漏. 从这个角度来看,电压无疑是控制芯片能耗的主要障碍. 但是另一方面,毫无疑问我们不能离开电压,因为电压保证芯片的正常工作是每个人都知道的最简单的事实.

晶体管的工作不能没有电压

晶体管“打开和关闭”以实现“与非”门的过程实际上是电子流入/停留/流出的过程. 驱动此过程的最基本元素是电压. 只有当电压达到一定水平时,电子才会经历我们在半导体中所需的定向运动. 晶体管的工作速度越快,频率越高,所需的驱动电压就越高. 因此,电压是半导体电路工作,尤其是高频工作的最重要基础,这甚至不需要任何科普知识.

即使是受影响相对较小的HD7950,功耗波动也高达36.8%

但是,无论是我们的流行科学还是上周的测试结果,毫无疑问,半导体电路工作的基本决定因素都被冠以“麻烦制造者”的烙印. 我们的测试仅将平均电压更改了15%,但换来了近40%的功耗变化. 即使我们进一步提高工作电压,由隧道泄漏引起的功耗增加也将更加明显. 迅速崛起. 这种异常的非线性增加不仅再次说明了隧道效应的严重性,而且使电压情况更加微妙.

一方面必须操作,另一方面则是无用和多余的. 再次发生包围的好场面...

4平衡是关键

●平衡是关键

现在,我们似乎陷入了一种自相矛盾的局面. 一方面,电压是导致泄漏并增加相同负载下图形卡功耗的罪魁祸首. 这将导致图形卡产生“完全没有意义的”功耗. 另一方面,电压是维持芯片工作频率的重要因素. 这两个平行存在,极其有用且完全无用,似乎使我们的选择极为困难.

实际上,事情并不像看起来那样困难. 只要我们了解我们的需求,选择也将变得容易. 一切事物都有积极和消极的一面,显示哪一面的具体属性取决于我们使它出现的位置. 让正确的事物在正确的时间,正确的时机出现,并解决最需要解决的矛盾. 我们自然可以收获事物的正面和正面属性,电压也不例外.

对于低端图形卡,性能可能比功耗更重要

我们需要弄清的第一件事是我们到底需要什么,是否需要补充高频,帧频或性能?还是使用过程中的功耗,热量和噪音性能?如果我们需要的是前者,那么矛盾自然就是性能而不是功耗. 此时,我们自然需要的是电压对高频晶体管的驱动特性. 尽管更高的电压会使泄漏更加严重,但这并不是矛盾的主体. 对于性能要求,我们只能通过改善散热和其他方法来平衡由电压升高引起的许多麻烦.

如果幸运的话,默认情况下,所使用的图形卡可以完全满足我们的需求,因此,作为驱动晶体管高频操作属性的电压就不再那么紧迫. 如果要控制图形卡的功耗,则降压是一种理想的方法. 较低的电压不仅可以大大降低隧穿的可能性,而且可以显着减少热电子迁移的发生,因为在热电子迁移现象中,驱动电子气进入晶格的电压效应远大于温度因子. . 因此,降低电压不仅可以减轻功耗和发热问题,而且可以进一步保护电路并等效地延长芯片寿命.

在稳定的前提下,采用降压对芯片有益

因此,在讨论降压是否有害时,我们可以给出一个相对肯定的答案-只要将降压幅度控制在芯片可以相对稳定运行的范围内,会影响芯片本身. 言语有利可图,但无害. 至于电压降的大小,受芯片和批次的质量所引起的随机性的限制,我们无法给出每个芯片可以正常工作的最低电压的确切答案,而是根据在我们的测试中,某些GPU芯片可以承受0.05V至0.1V的核心电压降. 如果要通过降低电压来降低图形卡的功耗,则可能希望以此为起点进行调整. 当然,必须要注意的是,由于GPU Boost和AMD Boost在一定程度上接管了电压的控制,因此目前支持这两种技术的产品很难降低电压.

GPU的电压,功耗和温度直接或间接影响性能,那么两者之间的直接关系是什么?或三者之间的激励优势是什么?本文使用严格的科学解释为您揭开神秘面纱. 文字可能晦涩难懂,但是如果您认真阅读,就会有所收获.

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/shenmilingyu/article-290403-1.html

-

-

于胜男

于胜男如果连自己的领海都能让人随便入侵

-

汉献帝刘协

汉献帝刘协语不惊人死不休的吸引眼球的所谓揭秘翻案文章

-

-

苗小娟

苗小娟就必然会提高存款利率上浮

为什么比特币挖矿使用那么多图形卡?

为什么比特币挖矿使用那么多图形卡? 高分一号分辨率?高分一号发射失败?高分10号卫星发射失败?中国高分辨率观测系统首星“高分一号”发射

高分一号分辨率?高分一号发射失败?高分10号卫星发射失败?中国高分辨率观测系统首星“高分一号”发射 显卡催化剂下载

AMDRadeonRadeonHD2400/HD/4770/4850/GTX970

显卡催化剂下载

AMDRadeonRadeonHD2400/HD/4770/4850/GTX970

配置电脑时如何识别显卡性能,查看显卡型号和配置

配置电脑时如何识别显卡性能,查看显卡型号和配置

我们是“让它三分”