三星电容规格 换个角度看台积电和三星的10nm 大战(2)

电脑杂谈 发布时间:2018-02-12 15:04:22 来源:网络整理进一步看看两者间鳍片结构的差异,透过TEM的影像以及EDS影像,我们可以解析其极细微的差异,图4a、4b呈现的是i8以及S8中鳍式矽基板的形貌,包含了N型(N-Fins)以及P型(P-Fins)结构。

两者的设计间存在着一些差异:首先,i8的N-Fins结构有二分之一的底部是相连的,这里跟S8的每个鳍片彼此间有很大的不同;表1统整了一些N-Fins的指标性尺寸,在这里我们可以发现两家的制程设计走向不一样的路线,S8致力于增加与闸极接触的鳍片高度(Fin High)与鳍片宽度(Fin Width),因此S8在这两个数字上都是略胜i8的,这个设计完全符合FinFET增加通道面积的概念。虽然i8可能在通道面积上略小于S8,但其鳍片间距却比S8小非常多,因此我们认为i8除了增加通道面积外,也兼顾缩小单元面积大小,因而能大幅增加SRAM单元数量。

另一方面是材料的选择,从图4c、4d的EDS影像显示,两种10nm的FinFET成份组成是大同小异的,而且也没有出现跟以往不同的新材料,但是,i8在P-Fins的设计上有一个较独特的地方,我们发现了明显的锗(Ge)讯号出现在鳍片上,而且整整涵盖了三分之一的鳍片,意即i8直接将锗元素添加于P-Fins结构中;而对照S8的设计,在P-Fins结构的顶端也可观察到锗讯号,但是非常微弱,而且只占整体十分之一的鳍片长。

在2016年IEEE国际电子元件会议(International Electron Device Meeting,IEDM)的一篇文章Setting the Stage for 7/5 nm中提及,在鳍片中添加锗确实能够有效地提升电洞的迁移率,而且三星、GLOBALFOUNDRIES、IBM皆已计画在7nm制程中使用,目前各厂尚未量产或大量添加,原因可能是尚未完全克服添加锗后形成的错位跟缺陷,但我们的确看到台积电已经在10nm量产中使用此技术领先群雄。

在目前的制程中,磊晶所生长的矽锗(SiGe)结构系利用矽锗与矽之间晶格常数差异产生应变,从而提高载子的迁移率,这使得逻辑元件在相同尺寸下,性能可以得到很大的提升。为了让读者一窥SiGe全貌,我们准备一个极薄(依照图5中闸极下缘high-k材料的边界及其下方的鬼影判断,我们制备的样品宽度为一个鳍片左右,约5~ 10nm)的样品来观察鳍片上方磊晶的SiGe结构。

图5即是在i8与S8平行P-Fins方向上观察到闸极与SiGe部位的高角度环形暗场(HAADF)影像及其EDS mapping影像。我们可以因此推敲一些设计细节:i8所使用接触SiGe的金属触点W为多段设计,但S8却是一整块的W材料;另一方面,比较SiGe的大小面积,即可看到S8的SiGe相对面积较小,可能在制程的过程中有较大的SiGe损耗,这一点在i8中可以看到其SiGe整体结构优于S8的表现。最后,在HAADF影像及EDS成份分析,则可观察到两者的SiGe皆呈现两个不同浓度的成份分布,中心与外层的锗浓度不相同,而这个设计最早在英特尔的14nm+时已经观察到了,相信浓度变化的SiGe应可导致更大的应变,使得载子的迁移率能够有效地提升。三星电容规格

最后使用SEM观察整体SRAM金属连线的状况(图6),在此可以清楚地看到i8在这个部份远远胜过S8,粗估M1至M11,i8的尺寸就比S8将近少了300nm,在这个金属连线迅速降低的情况下,相对而言即是带来寄生电容及讯号延迟(RC-delay)的现象。RC-delay的影响因子如下:

在导线距离W迅速减少的情况下,为了降低RC-delay的方法有二,第一为更换更低电阻的导线材料,这一点在日前于旧金山举行的IEDM 2017上,英特尔透露其10nm的制程节点细节,他们将为最底部的两互连层更换新材料——钴(cobalt),这个部份的细节将在日后进一步揭露;第二即是使用更低介电常数的材料做为low-k层。本文在i8与S8的讨论中,并没有发属导线材料的更新,所以我们推断i8所使用的low-k材料可能也优于S8,才能在尺寸最佳化300nm的情况下,依然保持高效能。

根据i8与S8的FinFET比较,以笔者的角度观察,S8规规矩矩地走向尺寸微缩,以及增加通道面积的方向,但是i8在这个架构概念下增加了更多的巧思,提升了整体逻辑区的密度,同时也在制程中添进了一些极微小的差异来改善效能。

透过进一步的材料分析,就能帮助制程端以及读者发现并了解这些极小的差异。正所谓「见微知著」,小小的一个SRAM区域就已经藏在许多设计上的小细节,而且最后的胜负就来自于这些每一个小细节的累积。

因应10nm以下的制程即将开打,制程端在微缩尺寸将会面临更多的挑战,此时制程的验证能力,如何精准地提供在几个纳米间的差距,绝对是致胜的关键。藉由材料分析带来的强大验证武器,将成为制程端以及读者的眼睛,并一起投入接下来的每一个战场。

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/sanxing/article-73754-2.html

Samsung G5109刷机教程_Samsung G5109钢丝刷官方系统包_可保存的积木

Samsung G5109刷机教程_Samsung G5109钢丝刷官方系统包_可保存的积木 i9088 刷机_kies无法连接i9088_i9100

i9088 刷机_kies无法连接i9088_i9100 java游戏精品全合集(按类型分类,游戏完全破解)

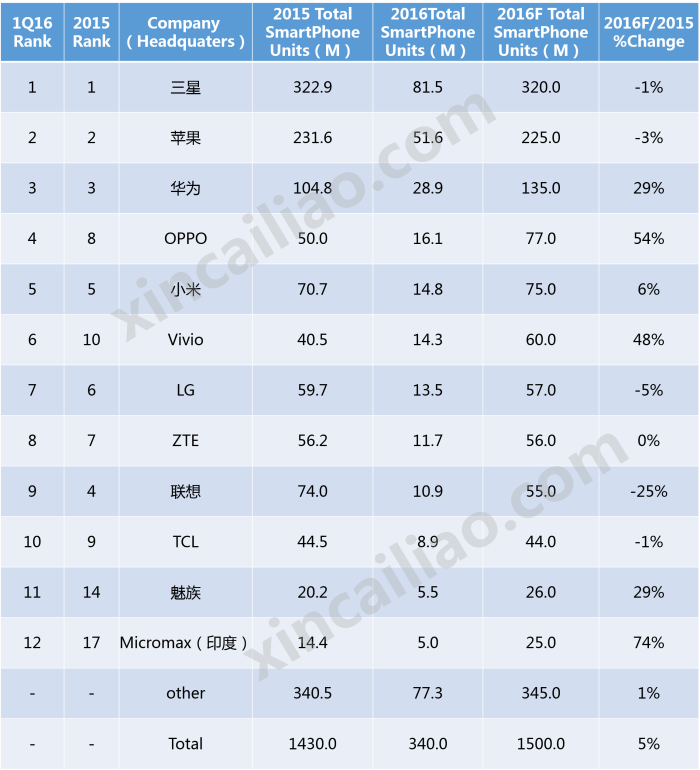

java游戏精品全合集(按类型分类,游戏完全破解) 第一季度全球手机销量下降. 为什么全球手机公司只有小米才能实现增长?

第一季度全球手机销量下降. 为什么全球手机公司只有小米才能实现增长?

马云创业时