tms320c6678_tms320c6713_tms320vc5501

电脑杂谈 发布时间:2017-01-09 14:15:59 来源:网络整理摘 要: 嵌入式应用中采用多处理系统所面临的主要难题是多处理器内核之间的通信。对KeyStone架构TMS320C6678处理器的多核间通信机制进行研究,利用处理器间中断和核间通信寄存器,设计并实现了多核之间的通信。从系统的角度出发,设计与仿真了两种多核通信拓扑结构,并分析对比了性能。对设计多核DSP处理器的核间通信有一定的指导价值。

关键词: TMS320C6678;KeyStone;处理器间中断;多核通信

嵌入式领域的处理器设计已向多核处理器迅速发展,TI公司的KeyStone架构的多核处理器就是其中之一。2010年11月,TI公司发布了最新的KeyStone架构的8核DSP处理器TMS320C6678,每个C66x内核频率为1.25 GHz,提供每秒高达40 GB MAC定点运算和20 GB FLOP浮点运算能力;1片8核的TMS320C6678提供等效达10 GHz的内核频率,单精度浮点并行运算能力理论上可达160 GB FLOP,是TS201S的50倍、C67x+的115.2倍[1],适合于诸如油气勘探、雷达信号处理以及分子动力学等对定浮点运算能力及实时性有较高要求的超高性能计算应用。

核间通信是多核处理器系统所面临的主要难点,通信机制的优劣直接影响多核处理器的性能,高效的通信机制是发挥多核处理器高性能的重要保障。TMS320C6678采用TI全新KeyStone多核架构,属于单芯片多核架构,有别于常见的板载多芯片通信方式[2]。而KeyStone架构的通信研究才刚刚起步,因多核通信复杂,需要搭建合适的通信拓扑结构,因此拓扑结构的选取会直接影响通信代价和并行计算的效率[3]。TMS320C6678采用基于KeyStone架构的中断控制器、核间通信寄存器以及合适的通信拓扑结构实现多核间的通信。通过中断系统激活处理器,触发具有通信功能的中断服务程序,调用寄存器完成相应的功能,并通过合适拓扑结构完成通信。

基于以上分析,本文针对TMS320C6678多核处理器,首先分析了中断控制器和核间中断原理及其实现;然后分析了核间通信的原理,给出了通信的发起和响应的实现方法;最后介绍了主辅和数据流两种多核通信的拓扑结构,并通过仿真对其通信代价进行了对比,得出了两种结构的优缺点以及适用范围。对设计多核处理器核间通信有一定指导意义。

1 TMS320C6678中断控制器

TMS320C6678采用基于KeyStone架构的中断控制器INTC(Interrupt Controller)[4]、激活处理器触发相应的中断服务程序,完成通信的第一步。

首先需要配置中断向量表,启动CPU中断功能。TMS320C6678的CPU可接收15个中断,其中:1个硬件异常(EXCEP)、1个不可屏蔽中断(NMI)、1个复位(RESET)和12个可屏蔽中断(INT4~INT15),中断源支持最多128个。每个核心通过事件控制器产生事件(Event),触发核间中断(IPI)和其他核心进行通信。在TMS320C6678中,核间中断(IPC_LOCAL)默认对应91号事件,而核间中断属于可屏蔽中断,通过中断控制器可以映射到INT4~INT15任意一个中断上。tms320c6678为了实现核间中断,必须按以下方式进行设置:

(1)控制状态寄存器(CSR)中的全局中断使能位置为1,全局中断使能;

(2)中断使能寄存器(IER)中的NMIE位置为1,可屏蔽中断使能;

(3)中断使能寄存器(IER)将要映射的可屏蔽中断的相应位置1;

(4)选择91号事件作为中断源,映射事件到指定的物理中断号。中断发生后,将中断标志寄存器(IFR)的相应位置1。

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/ruanjian/article-25204-1.html

-

-

郑闻

郑闻家用电器设计寿命一般是多少年

如何拍摄计算机的屏幕截图?您如何在计算机上拍摄屏幕截图? ?

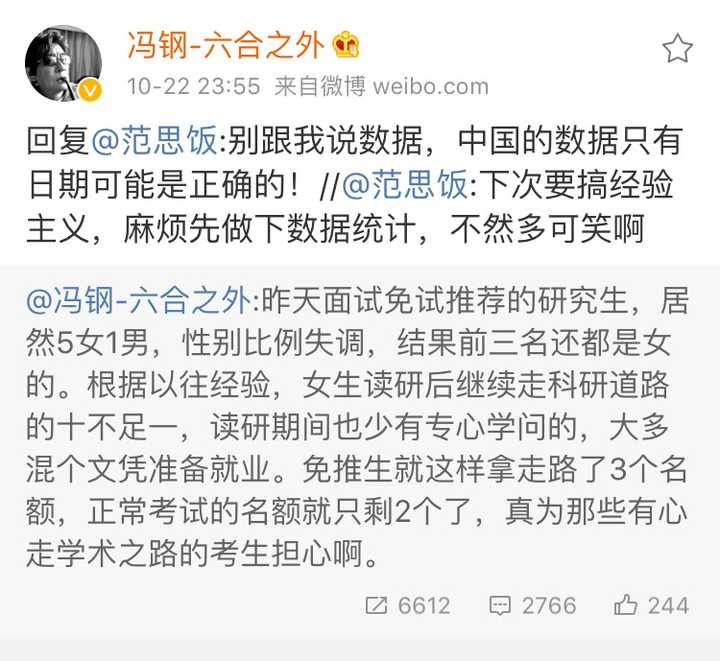

如何拍摄计算机的屏幕截图?您如何在计算机上拍摄屏幕截图? ? 网络不是一片荒野,微博教授不会“发誓”

网络不是一片荒野,微博教授不会“发誓” 如何设置开关的速度限制

如何设置开关的速度限制 主机和虚拟机可以互相ping 通,主机可以上网,但是虚拟机ping不通外网!!!急急急

主机和虚拟机可以互相ping 通,主机可以上网,但是虚拟机ping不通外网!!!急急急

养兵千日用兵一时