基于TMS320F28335的DSP最小系统设计

电脑杂谈 发布时间:2019-06-17 23:10:18 来源:网络整理

由于有铅制程的长期可靠性已经经过多年的认证,现阶段军工电子产品仍然采用有铅焊接,但是由于我国电子芯片制造业的落后,大量芯片特别是球状引脚栅格阵列封装(bga)、四侧引脚扁平封装(qfp)类集成电路几乎都是从国外,而且很难采购到可靠等级高的集成电路,经常只能买到国外工业级集成电路 [7] ,但是国外大部分厂家已停止对这种传统有铅元器件的生产而改为无铅元器件,市面上有铅镀层元器件几乎没有。 d8 w1 |是一种将多接脚集成电路器(ic)的芯片(chip),不再先进行传统封装成为完整的个体,而改用tab载体,直接将未封芯片黏装在板面上.即采"聚亚醯胺"(polyimide)之软质卷带,及所附铜箔蚀成的内外引脚当成载体,让大型芯片先结合在"内引脚"上.经自动测试后再以"外引脚"对电路板面进行结合而完成组装.这种将封装及组装合而为一的新式构装法,即称为tab法。反而是利用多片芯片的整合封装方式,让多片led小芯片在载板上的等距排列,利用打线连接各芯片、搭配光学封装材料的整体封装,形成一光源模组产品,而多片封装可以在进行芯片测试后,利用二次加工整合成一个等效大芯片的光源模组,但却在制作弹性上较单片设计led光源用元件要更具弹性。

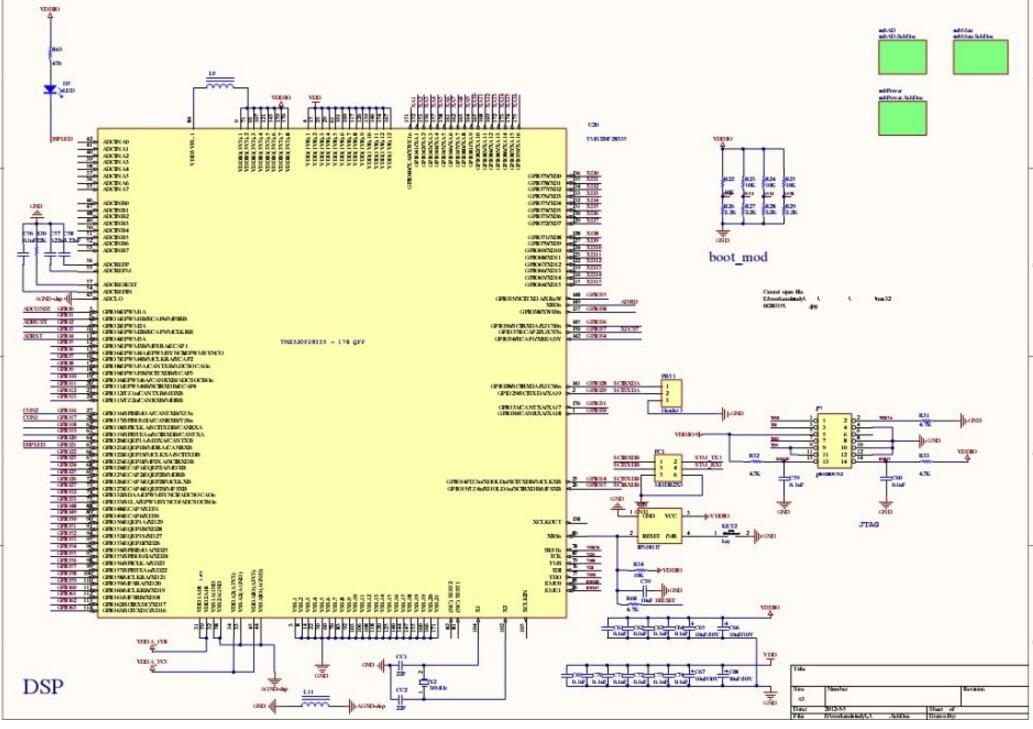

将5V电压转换为3.3V和1.9V,可以使用双输出电源调节方案。TI 公司的 TPS767D301 可以提供一路 3.3V 固定输出电压和一路可调输出电压 (1.5~5.5V)。 如图 所示为TPS767D301 的原理图。其中 取值122kΩ,R 取值233kΩ 时,可以输出 1.9V,如图 所示。芯片采用数字5V供电,如图4 所示,其中D1 起电源指示作用。 图2TPS767D301 原理图 引脚24和25 的电路 另外,DSP 控制芯片中同时含有数字电路和模拟电路,为防止数字电路对模 拟电路干扰,通常将这两种电路分开供电,故F28335 实际需要4 组电源:数字 3.3V、数字1.9V、模拟3.3V 和模拟1.9V。其中,数字3.3V 和数字1.9V 利用上 述方案产生,模拟3.3V 和模拟1.9V 电源可以在相应数字电源基础上,加上电感 和电容进一步滤波得到,数字地和模拟地也要用电感隔离,如图5 和图6,图中 DVDD3.3 AVDD3.3分别表示数字 3.3V 和模拟 3.3V,DVDD1.9 AVDD1.9分别表示数字1.9V 和1.9V。从数字电路产生模拟供电电路比较简单,利用无源 器件像电感来滤除噪声,电感就像一个低通滤波,让直流成分通过tms320f28335最小系统,截止噪声和 高频成分,利用铁氧磁体比标准的电感要好,这种电感具有可以忽略的寄生电容, 电气特性和一般的电感相似。

F28335 为双电源供电,需要考虑上电次序。理想情况下,CPU 内核与 电源应该同时上电,若不能同时上电,CPU内核应该优先于I/O 上电,二者相差 时间不能太长。为了保护DSP 器件tms320f28335最小系统,应在CPU 内核电源与I/O 电源之间加一个 肖特基二极管,如图7 所示。 如图8 所示,电源需要并联电容用于滤波,其中大电容主要是利用电容的充 放电特性使得输出的脉动波形更加平稳;小电容在高频条件下容抗比较小,高频 干扰信号可以通过小电容接地,这样可以减少高频干扰对后面电路的影响。 考虑到 TPS767D301 芯片自身能够产生复位信号,此复位信号可以直接供 DSP 芯片使用,所以可以不用为DSP 设置专门的复位芯片,复位信号与DSP 片的连接如图2中28 引脚所示。另电路 电源滤波电路2.3 复位电路设计 复位电路的作用是在上电或程序运行出错时复位DSP。最简单的复位电路如 所示的RC 复位电路,其中S 为手动复位开关,C57 可以避免高频谐波对电 路的影响,二极管D 复位电路原理图2.4 时钟电路设计 DSP 控制器内部集成了时钟电路,外部时钟的产生有两种方案:一种是利用 片内时钟电路,外加晶振和2 个负载电容;二是禁止片内时钟电路,直接由外部 提供时钟信号。

由于第一种方案电路简单、价格便宜,所以采用方案一进行设计,如图 10 所示。有效的负载电容C LOAD 在振荡电路中是C 并联的等效电容,正确的有效负载电容对于正确的运行频率是非常重要的,对于不同的负载电容值,都有 不同的晶振与其相应。但是,内部的数字控制器振荡器对于太高或太低的负载电 容是没法工作的,可以从晶振的厂商的数据手册得到更多的信息。并联谐振模式 需要的负载电容大概是 12pF,等效电阻是 30~60Ω。由于 PCB 板布局和数字控 制器焊锡的兼容性问题,有效的C 的值一般不大于5pF,布局电路板也是非常重要的方面。如果想要得到准确的频率控制器,那么准确的离散电容值要根 据利用频率计数器测量的电容和频率的准确关系来定。设计时,晶振的典型值可 取30MHz,两引脚的接地电容大小可取24pF。 图10 时钟电路原理图 2.5 JTAG接口电路设计 TMS320F28335 采用 1149.1-1990IEEE标准协议和 IEEE 标准的测试接 口和边界扫描结构的 JTAG 信号接口,以及两个扩展接口(EMU0 EMU1),该接口通过直接访问。扫描仿真消除了传统电路仿真存在的电缆过长引起 的信号失真及仿真插头的可靠性差等问题。

采用扫描仿真,使得仿真成为可 能,给调试带来方便。在实际设计过程中,考虑到JTAG 下载口的抗干扰性,在 与DSP 连接的EMU0、EMU1 端口必须通过上拉电阻连接至电源,TRST 引脚通 过下拉电阻接地,且分别在其引脚上添加旁路电容。JTAG 接口电路连接如图11 所示。 图11 JTAG 接口电路原理图 2.6 外部存储器扩展设计 F28335DSP 控制器片内由 34kW FLASH。在系统开发阶段,当程序代码小于 34kW 时,虽然可以直接烧写进片内 SRAM 运行,但 是调试不方便,此时可外扩RAM。 外扩存储器需要通过外部接口 XINTF 实现。XINTF 具有 20 位地址总线 XA0~XA19 32位数据线 XD0~XD31。IS61LV25616 是一个高速 256k16 的静态RAM,采用独立3.3V供电。使用一片IS61LV25616 为F28335 外扩存储 器,并将其映射到Zone6 区域。其中地址总线XA0~XA18、数据总线 XD0~XD15 分别于DSP 的地址总线XA0~XA18、数据总线XD0~XD15 相连。具体原理图如 图12 所示。 图12 IS61LV25616 与DSP 的接口 2.7 注意事项 为了提高系统的抗干扰性,在设计中应注意以下一些事项: 在连接外部振荡器时,需要注意负载电容的阻值,如果用户使用内部或者 外部振荡器时,把器件放在靠近引脚的地方,目的是缩短线路的长度,引线要短 且粗,应远离发热元件。

vsb---二次击穿电压 vbb---基极(直流)电源电压(外电路参数)vcc---集电极(直流)电源电压(外电路参数) vee---发射极(直流)电源电压(外电路参数)vce(sat)---发射极接地,规定ic、ib条件下的集电极-发射极间饱和压降vbe(sat)---发射极接地,规定ic、ib条件下,基极-发射极饱和压降(前向压降)vagc---正向自动增益控制电压 vn(p-p)---输入端等效噪声电压峰值 vn---噪声电压cj---结(极间)电容, 表示在二极管两端加规定偏压下,锗检波二极管的总电容cjv---偏压结电容 co---零偏压电容 cjo---零偏压结电容 cjo/cjn---结电容变化cs---管壳电容或封装电容 ct---总电容ctv---电压温度系数。i2c模拟读取寄存器值得时候,读回来全是0xff,我自己用导线连高低电平给io口,模拟读取外部引脚都是准确的(接3.3v时,读回来是1,接地读回来是0)。如图:rin为信号输入端,耦合电容c23进入音量电位器,(音量电位器由三个引脚,与c23连接的是输入端,输出端也叫滑动端、另一引脚为接地端),音量后信号进入由r1/c3组成的高音提升电路,此电路可以提升量的高频信号,使声音更加清晰。

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/ruanjian/article-106730-1.html

10月31日每日酷跑免费验证退货号码共享

10月31日每日酷跑免费验证退货号码共享 DCN(北京神州数码云科信息技术)

DCN(北京神州数码云科信息技术) Vanke鼓励员工创业,启动合作伙伴系统以增强外部产品的实力

Vanke鼓励员工创业,启动合作伙伴系统以增强外部产品的实力 cube world联机?逆风笑?steam?《魔方世界CubeWorld》联机方法

cube world联机?逆风笑?steam?《魔方世界CubeWorld》联机方法

谢作诗这厮脑袋进水了吧