并行处理系统结构 LUCT工具主要特性及其使用教程(2)

电脑杂谈 发布时间:2018-02-10 06:29:14 来源:网络整理o 网格生成: 在从布局规划读取数据后,生成障碍模型和电源网格形状模型。从这些模型开始计算一个代表LuCT算法定义的布局布线间距的点集合(网格)。

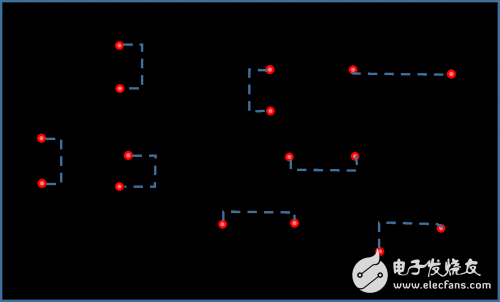

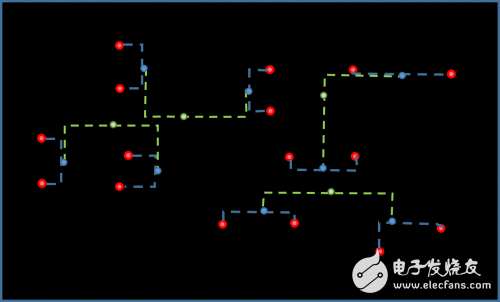

o 构建二进制树:使用意法半导体独有算法将叶子分组,每组一对。通过计算长度均等的包含避障点的路径和合并点(即该路径中间的一点)的方式将每对树叶合并。通过这种方法按照递归方式合并新的叶子(合并点),直到只剩下一个点(树根)为止,详见图4到图6。

o 插入时钟驱动器和布线:插入时钟驱动器和优化布线是采用一个自下向上的方法,分别考虑障碍布局和障碍布线。

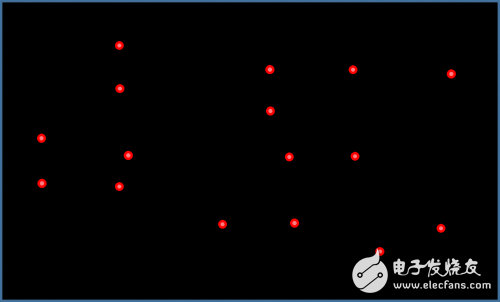

图 4:终点集合

图5:LuCT创建树算法配对决策与合并

图 6:上一级产生的合并点配对合并

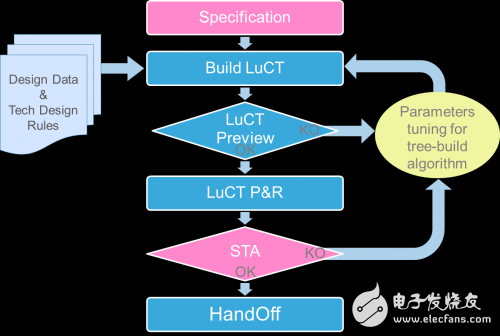

图7 :采用LuCT工具的设计流程

一旦生成时钟树结构,只要在布局布线CAD工具内使用脚本程序即可实现布局。并行处理系统结构对于多个并行时钟驱动器的高性能布线/走线、通孔布局和电源噪声感知布局,取得布局配置需要使用自定义规则。

通过修改几个对二进制树架构和创建有很大影响的参数,可以优调算法。

下面是一些参数示例:

o 叶子对生成:可自动或人工生成

o 路径距离计算:可以是纯Manhattan方式或能够感知障碍

o 弯折最小化:为布线网络选择适合的吸引力

o 通过在每个布线/合并阶段全局重映射中心,吸引合并区向现阶段的中心转移

o 时钟树性能指标:障碍强度、时钟偏差/插入延时性能与障碍的均衡性、时钟拥堵。

LuCT 工具 示例和结果

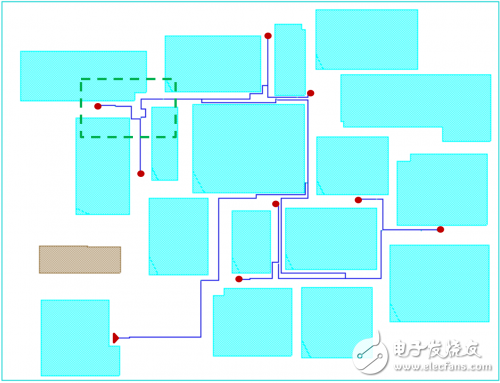

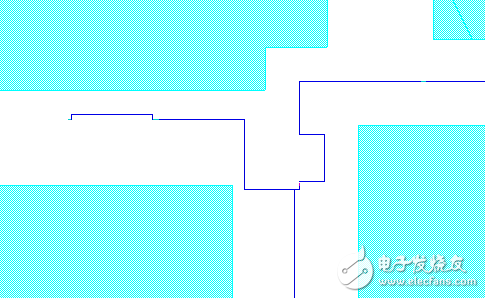

图8所示是按照上面讨论的方法使用LuCTgenKit设计 28FDSOI芯片的时钟树。并行处理系统结构1GHz时钟信号从时钟源分配到8个树叶,避绕障碍,平衡时钟偏差,查觉障碍。图9所示当连接高层叶子对时如何执行等长计算。

图 8

图 9

这个示例的主要结论是,按照基延迟(base delay)计算,时钟偏差是非常有限的,不过,出现大量的不常见路径。

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/jisuanjixue/article-69734-2.html

结果如何我们拭目以待