二进制与格雷码的转换

电脑杂谈 发布时间:2016-05-21 04:03:23 来源:网络整理你是否正在寻找关于格雷码的内容?让我把最权威的东西奉献给你:

FPGA Verilog HDL 系列实例--------二进制与格雷码的转换

【连载】 FPGA Verilog HDL 系列实例

Verilog HDL 之 二进制与格雷码的转换

格雷码的特点:相邻的两个码组之间仅有一位不同。

普通二进制码与格雷码之间可以相互转换。下面将作简要的介绍。

8位二进制码转格雷码

二进制码转换为格雷码:从最右边一位起,一次与左边一位“异或”,作为对应格雷码该位的值,最左边的一位不变(相当于最左边是0),。

1 modele bin2gry(Gry,Bin)

2 parameter length = 8;

3 output [length-1:0] Gry;

4 input [length-1:0] Bin;

5

6 reg [length-1:0] Gry;

7 integer i;

8

9 always @ (Bin)

10 begin

11

for(i=0;i<length-1;i++)

12

Gry[i]=Bin[i]^Bin[i+1];

13

Gry[i]=Bin[i];

14 end

15 endmodule

8位格雷码转二进制码

格雷码转换为二进制码:从左边第二位起,将每一位与左边一位解码后的值“异或”,作为该解码后的值(最左边的一位依然不变)。

1 modele gry2bin(Gry,Bin)

2 parameter length = 8;

3 output [length-1:0] Gry;

4 input [length-1:0] Bin;

5

6 reg [length-1:0] Bin;

7 integer i;

8 always @ (Gry)

9 begin

10

Bin[length-1]=Gry[length-1];

11

for(i=length-2;i>=0;i--)

12

Bin[i]=Bin[i+1]^Gry[i];

13 end

14 endmodule

posted @

以上就是关于格雷码的全部内容,相信你一定会非常满意。

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/jisuanjixue/article-5716-1.html

-

张贝

张贝 -

顾浩然

顾浩然都是纸老虎

-

张南

张南飞机偏离航道会不知道

-

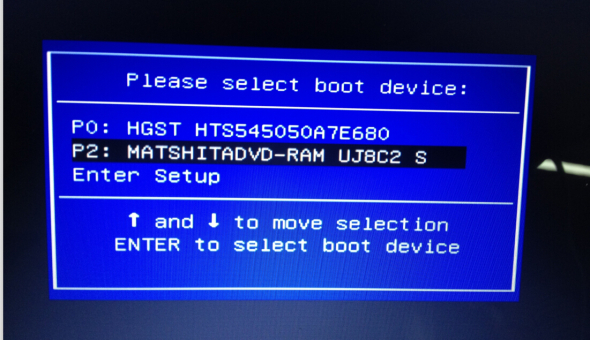

没有怎么怎么重装xp系统光驱记得光驱以前是双盘位

没有怎么怎么重装xp系统光驱记得光驱以前是双盘位 “ R语言数据挖掘”读书笔记: 六,高级聚类算法

“ R语言数据挖掘”读书笔记: 六,高级聚类算法 Win10美丽的焦点锁定屏幕壁纸下载列表(持续更新)

Win10美丽的焦点锁定屏幕壁纸下载列表(持续更新) win8 / 8.1网卡驱动程序通用脱机版本32位/ 64位

win8 / 8.1网卡驱动程序通用脱机版本32位/ 64位