使用FPGA的ASIC原型验证(更新)

电脑杂谈 发布时间:2020-07-03 06:05:37 来源:网络整理

参考:

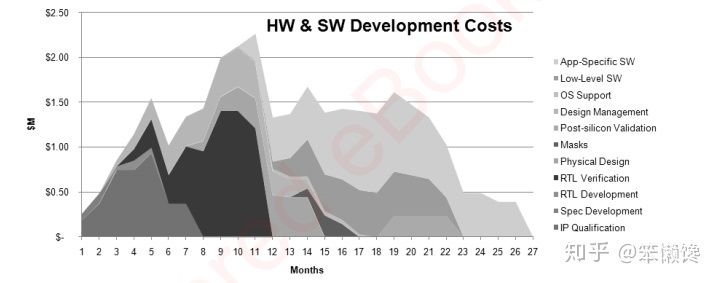

由于芯片设计的复杂性增加,成功设计芯片所涉及的步骤和过程变得越来越复杂,所需的成本也成倍增加. 一个典型的芯片开发项目的周期和成本如下<

可以看出,在芯片制造之前asic验证,RTL代码验证工作将花费大量精力. 此外,与软件相关的开发工作也将在获得芯片之前开始. 这两个方面都需要使用FPGA原型来仿真芯片. 帮助硬件开发人员和软件开发人员一起工作以提高工作效率的行为.

FPGA原型在数字芯片的设计中基本上是必不可少的. 原因很明显. 与使用或进行仿真相比,FPGA的运行速度更接近真实芯片,并且可以与软件开发人员合作. 开发基础软件. 当然,FPGA原型替代芯片也有很多限制,例如规模限制,速度限制,功耗限制,结构限制等. 使用FPGA原型替代芯片时,需要进行相应的修改才能完成. 相应的功能. 甚至某些功能最终都无法涵盖.

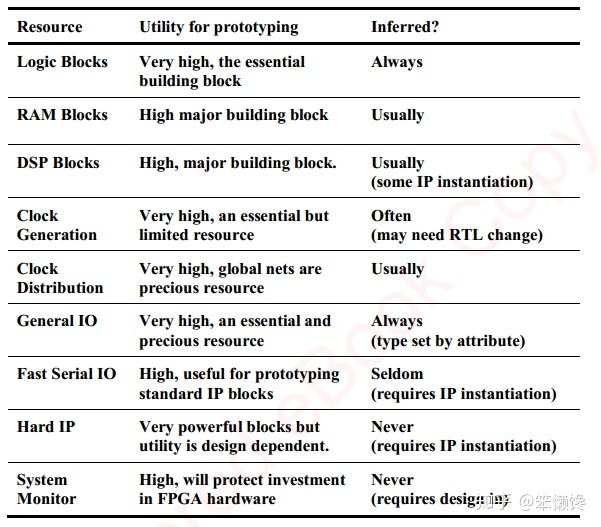

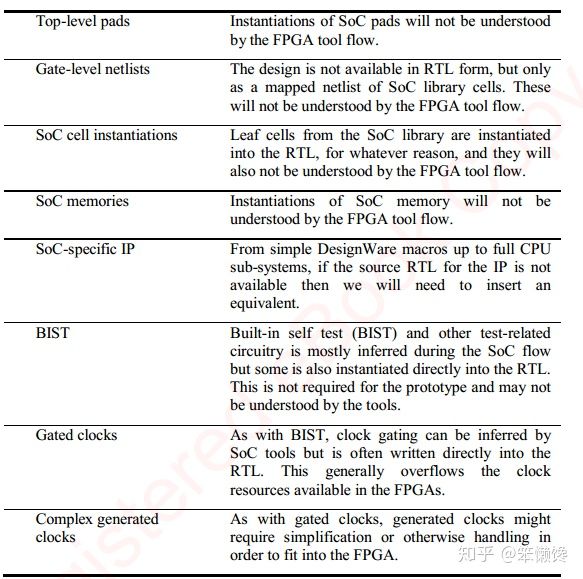

如果我们将可以映射到FPGA中的ASIC的资源一一比较,就会得到这样的表.

上表显示,除了普通的RTL逻辑和基本端口asic验证,其他类似的存储时钟DSP等外,最好手动进行映射,将ASIC设计转换为FPGA更可靠.

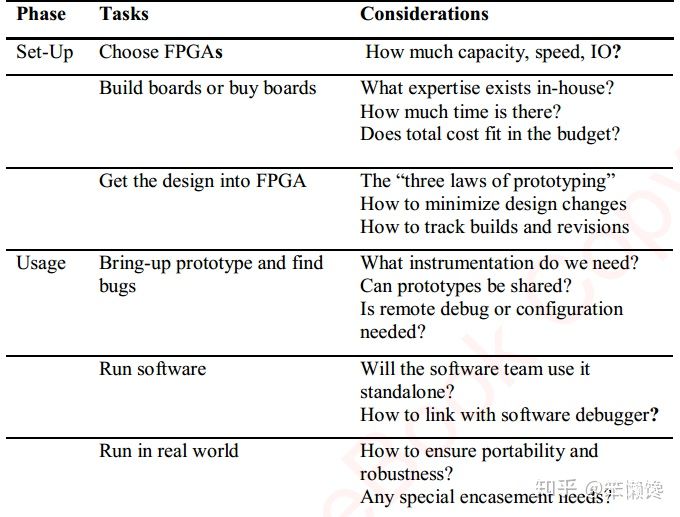

要使用ASIC对FPGA进行原型设计,您需要大致概述步骤,

1个FPGA选择

2制作一个板子或购买一个原型板.

3将ASIC设计转换加载到FPGA

4调试并启动FPGA原型

5加载软件并一起运行

6个软件和硬件系统验证

以下步骤将根据这些步骤一一讨论:

第一个是选择FPGA. 当然,在选择之前,您需要对ASIC的设计有一个总体的了解,包括以下几个方面:

最关心选择的几个维度:

1个容量,其中包括纯逻辑容量,存储容量,dsp单位容量

2具有内置IP的硬核,包括时钟,存储控制,CPU等.

3个接口普通接口和专用高速接口

4速度通常使用资源占用率为50%左右时的速度来评估原型

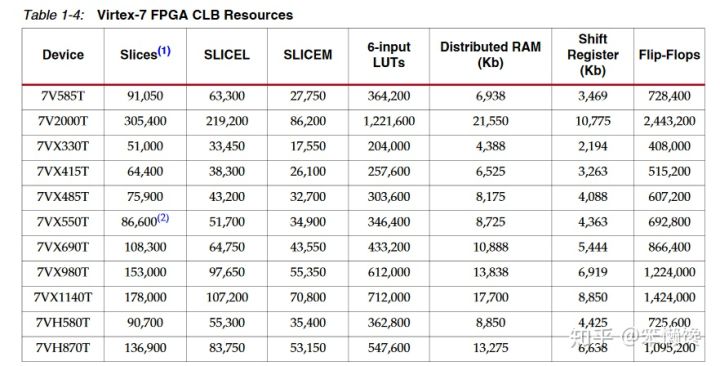

纯逻辑容量,即ASIC中组合电路和触发器的容量,可以直接转换为FPGA中的资源.

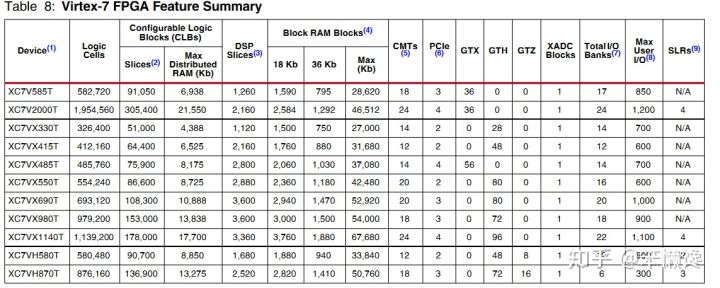

例如,上图中的xilinx V7 2000T具有2.4M FF,大致相当于ASIC的2个输入NAND门10M门. 如果按50%计算利用率,那么放置5M逻辑门可能没问题.

内置存储器可以实现21M的单端口和双端口ram,rom,fifo等. 如果ASIC中使用的存储量更多,还可以使用lut来实现部分存储,而不是block ram.

如果使用更多的乘法加法运算,则还可以在fpga中映射dsp设备实现. 有关各种类型的FPGA中包含的特定数量的器件,您可以参考xilinx文档.

对于内置IP,首先要考虑的是时钟模块MMCM. 通常,FPGA将具有数个到数十个时钟模块. 例如,下表2000T包含24个CMT,即24个PLL和MMCM,每个Group PLL和MMCM可以对时钟域的时钟进行分频和乘法. 通常,一个ASIC将包含多个时钟域,并且每个时钟域至少需要一个CMT来操作时钟,可以相应地选择该FPGA器件.

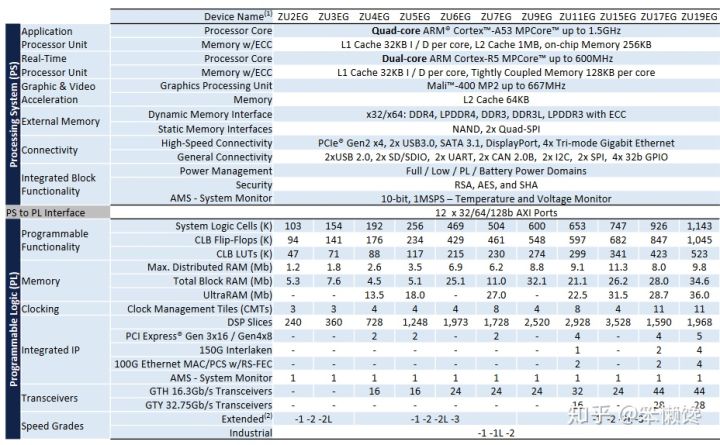

如果要选择具有ARM硬核的FPGA来模拟ASIC中的ARM核,则需要选择zynq系列. 系统中自行开发的逻辑通过AXI挂接到总线上. 当然,这可能无法使FPGA和ASIC中的系统完全一致,但是作为一个圆圈,这也足够了. 以下是一些具有ARM内核的FPGA的容量以及相应的IP情况

由于接口的限制,普通FPGA的普通接口数量足够大,不会成为瓶颈. 主要原因在于ASIC所需的特定接口. 它们可以在FPGA中满足吗?很多时候,这些特定的接口需要外部phy才能完成相应的功能.

许多因素会影响FPGA的最终运行速度,包括代码样式,特定设计,资源占用率,FPGA模型等,因此需要在RTL代码的基本框架为完成,因此作为ASIC原型,请尝试足够快地选择FPGA.

通过上述资格,您基本上可以选择要使用的FPGA模型,但是ASIC资源可能太多,并且都无法安装. 有2个解决方案. 一种是分别验证块. 当然,这非常危险,最终系统无法直接验证.

另一种方法是使用多个FPGA获得原型,这涉及不同FPGA之间的功能划分. 这是一件麻烦和困难的事情. 它具有FPGA电路设计和ASIC到FPGA代码的转换. 不少新问题.

第二步是制作一个板,这在很多方面都需要考虑,例如信号完整性,电源问题,时钟问题,可伸缩性等,我对此没有直接的经验,所以我不能开始. 当然,对于需要多个FPGA的验证板,一个普通实力的团队可能无法获得,因此选择在平安花钱并直接使用HAPS之类的验证系统更为可靠.

第三步是将ASIC设计到FPGA中. 这需要修改最初用于ASIC的代码.

对于一般的纯RTL逻辑,可用的结果可以在ASIC和FPGA中进行综合,但是下表中的设备需要修改

芯片中的焊盘通常是制造厂给定的硬核,具有输入和输出,向上和向下控制等. 转换为FPGA时,通常在实例化中直接用assign替换它,并指定在.XDC或.v

中向下移动

如果您有ASIC门级网表,则可以用verilog行为描述替换基础的ASIC实例设备,该描述可以在FPGA综合中相应地实现. 其他简单的单元格实例化也可以通过这种方式进行转换.

对于存储器,通常可以在FPGA中找到与ASIC具有相同功能的SRAM和ROM. 您可以通过替换ASIC MEM直接包装FPGA MEM来更改端口名称. 小型嵌入式闪存可以用逻辑层仿真FPGA SRAM.

对于其他硬核IP,您可能需要在FPGA中找到相同的功能并相应地修改接口,以有效地与ASIC代码的其他部分连接.

对于BIST,最直接的方法是将其删除,这通常不会影响实际功能.

对于各种门控时钟,倍频和分频等,通常需要手动修改FPGA并使用DCM来完成与芯片中的时钟一致的行为.

以下是对某些修改中将出现的特定问题的详细说明.

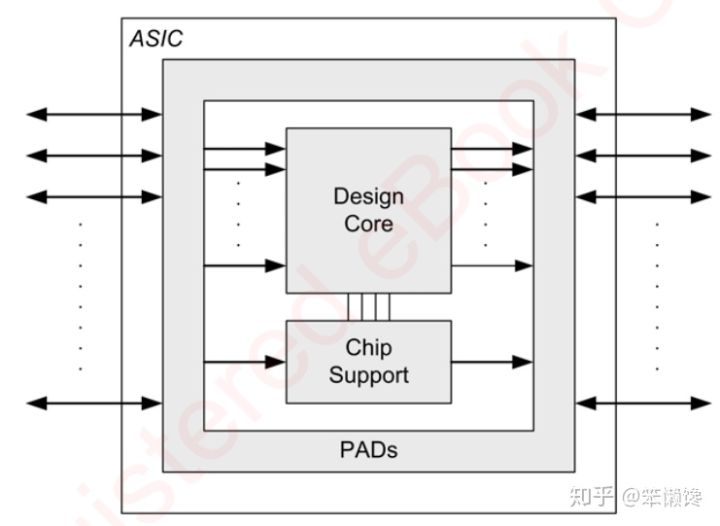

首先,我们得到的ASIC设计的结构基本上如下图所示. 最外面的环是各种焊盘环,内部是芯片的各种辅助功能,包括clk,rst,电源,测试,调试等. 然后还有与芯片的实际功能有关的部分,可能包括一些模拟电路,数字电路包括cpu,mem总线,各种逻辑控制等. 我们需要明确地使用FPGA来验证原型,主要是数字电路中的核心功能,以及芯片核心之外的许多辅助逻辑,其中许多需要修改且无法验证. 此处的填充通常直接实例化一个FPGA PAD等效实例,该实例直接在FPGA中包含多个assign语句. 需要根据特定的上电顺序和时钟资源来调整clk rst. 通常,第一个功能被简化为全局复位,而clk中的分频和关闭功能将在CMT中实现. 在FPGA中通常直接忽略功率控制,因为FPGA几乎无法仿真各种UPF指定的行为. 可以根据实际情况保留或删除调试测试,但是即使维护了调试测试,通常也不会真正使用它. 核心功能中需要更改的通常是各种内部存储器.

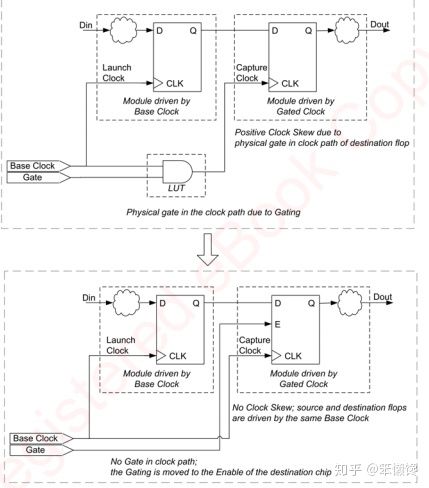

时钟门控时钟门控通常在ASIC中广泛使用,并且通常在clk模块中实例化到由锁存器AND门组成的门控制单元中,以控制某个模块的时钟. 如果将这些门控单元直接实例化为FPGA中相同逻辑的锁存器AND门,则逻辑功能就没有问题. 但是,此时,从“与”门出来的受控时钟不能再在FPGA的专用时钟网络中路由,而是在公共信号网络中路由,因此FPGA可以达到的频率非常差. 为了纠正这种情况,可以将寄存器的门控置于寄存器侧,即在FPGA中选择具有门控的寄存器,例如FDCE. 此过程可以手动完成,但是比较麻烦. 一般来说,专用的FPGA综合工具可以执行此自动转换. 例如,使用(* gated_clock =“ true” *)输入clk_a;在vivado中以校准受控时钟,并在脚本中添加-gated_clock_conversion on综合选项.

当然,如果可控时钟没有太多,即少于FPGA中的BUFGCE数量,则可以直接将栅极控制信号加到BUFGCE控制端子上,输出就是栅极控制信号时钟网络. 如果FPGA器件中存在BUFHCE,则可以选通更多级别的时钟,并且可以获得更多的受控时钟.

有关FPGA门控时钟的更详细说明,请参考

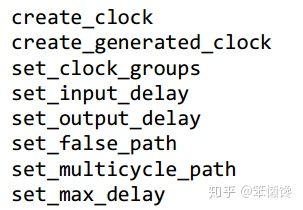

例如,ASIC到FPGA使用的全面限制基本上与SDC和XDC兼容

这些可以直接使用. 当然,在许多情况下,FPGA仍不可能以ASIC速度运行,而必须以降低的速度运行. 此外,您需要在FPGA中增加对引脚位置,类型,驱动强度等的限制,以及一些综合性的选择

以上是ASIC代码更改的主要部分. 在调试FPGA板之前,最好模拟更改后的FPGA代码,以确认功能正常,并减少板上调试的工作量.

第四步是开始调试FPGA原型.

在将修改后的FPGA代码加载到调试中之前,首先需要确保FPGA板本身正常可用. 目前,如果它是购买的开发板或类似于haps的验证系统,则可以节省一些麻烦.

如果这是第一个开发的FPGA板,则需要首先加载最简单的FPGA映像文件,测试FPGA的电源,下载连接是否可用,然后传递多个FPGA文件进行测试. 连接到板上FPGA的其他设备是否正常工作. 通常,该板的第一个设计会遇到各种问题,例如电源问题,引脚连接的差分信号匹配问题,阻抗匹配,电流驱动,信号质量等. 如果该板通过了上述测试,则可以想到电路硬件设计没有问题,您可以加载FPGA原型文件进行测试.

加载修改后的FPGA原型仿真ASIC通常不会成功一次. 可能发生的问题可以分为以下三类:

1个RTL逻辑错误,包括原始ASIC和修改过程中引入的错误.

2接口错误与外部设备的电信号连接不正确,包括电压不匹配和驱动电流不一致.

3软件错误MCU上运行的软件未正确配置相关功能. 这在仿真中通常很难找到,因为仿真很少运行真实的软件系统.

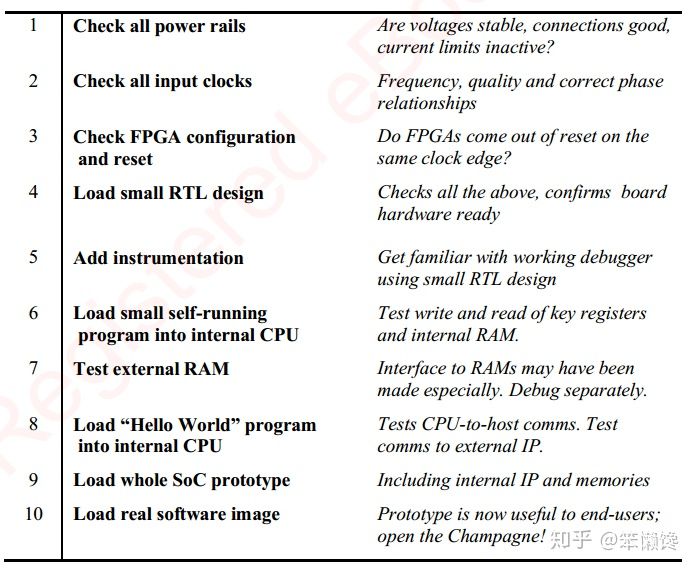

fpga原型的机载调试可以概括为以下步骤.

在加载实际运行的软件之后,通过FPGA原型,您可以像实际芯片中一样测试和修改软件,并完成系统级验证工作. 进入步骤5.6,与普通的嵌入式软件开发大致相同.

对于通过FPGA进行原型验证,有以下设计过程建议,值得参考

以上内容是指xilinx网站的内容以及诸如FPMM之类的书籍.

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/jisuanjixue/article-266625-1.html

-

-

张静娜

张静娜好可爱的笔笔

haiku deck_sunca sf238_iphone7 home键会坏吗

haiku deck_sunca sf238_iphone7 home键会坏吗 ccriticalsection使用_ccriticalsection 嵌套_ccriticalsection

ccriticalsection使用_ccriticalsection 嵌套_ccriticalsection 【360杀毒软件】360杀毒软件(360正式版)新版本下载

【360杀毒软件】360杀毒软件(360正式版)新版本下载 Flash手机!频繁闪烁手机会对内部硬件造成什么损害?

Flash手机!频繁闪烁手机会对内部硬件造成什么损害?

是可以做到底