数字电路——60进制同步加法计数器的设计

电脑杂谈 发布时间:2020-05-27 13:20:13 来源:网络整理

60进制同步加法计数器的设计

尝试使用同步加法计数器74LS161(或74LS160)和两个4输入与非门74LS20在100以内形成任意十进制计数器,并使用LED数字管显示计数十进制. 555定时器用于形成多谐振振荡电路,该电路为同步加法计数器提供时钟输入信号. 例如,图2显示了使用同步加法计数器74LS161构成60进制加法计数器的参考电路.

图2

分析整个电路设计60进制计数器,所需的逻辑功能设计过程可分为三个部分,即加法计数器的设计,由555计时器组成的多谐振荡器的设计以及LED数字管显示系统的设计.

1. 加法计数器的设计(清除方法)

74LS161是一个十六进制的四位二进制加法计数器,可以异步清除并同步设置.

设计一个60位加法计数器,然后使用clear方法. 60以二进制形式表示为00111100,因为它已被异步清除. 当计数器从零开始计数时,可以在达到00111100时异步清除. 要使用两个74LS161,需要使用同步并行级联来级联两个计数器. ET和EP连接到较高级别. 低限位片计数为1100,高限位片计数为0011异步清除,与四个输入与非门相连,输出连接至

结束. 逻辑电路为:

2. 多谐振荡器的设计

给定设备中有两个510K电阻,它们用作多谐振荡器的外部电阻. 电容器是103个电容器,那么多谐振荡器的周期是:

由555形成的多谐振振荡电路为:

3. LED数码管

将两个74LS161的输出端连接到数码管的输入端,以显示计数系统. 电阻器已集成在LED数字管内设计60进制计数器,因此无需在为0

59,即0

3B.

4. 预调零

对整个电路的分析表明,在电路上电之前,74LS161的清除端子可以视为低电平,其清除方法是异步清除,因此可以认为74LS161处于清除状态. 上电前的状态. 因此,使用此方法的电路的初始状态必须为0,因此不需要预先清除.

在Multisim中进行仿真后,使用逻辑分析555定时器的输出和两个74LS161的输出,以获得以下时序图.

整个实验电路图为:

其他设计选项

74LS161设置编号方法

上面显示了74LS161清除方法,也可以使用设置方法.

使用set方法时,由于74LS161是同步设置数字,因此计数系统为60(00111100),因此当计数器从零开始计数到59(00111011)时,它将设置数字00000000并等待下一个时钟上升沿到达后,计数器被清除.

555计时器和LED与第一种方法相同.

计数器逻辑电路是:

此外,您还可以使用其他芯片(例如74LS90)来实现计数功能.

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/jisuanjixue/article-224081-1.html

-

-

朱云青

朱云青中方对此表示强烈不满和坚决反对

系统win10纯净版系统系统补丁更新至2016-01

系统win10纯净版系统系统补丁更新至2016-01 Win10家庭版最终可以暂停更新了

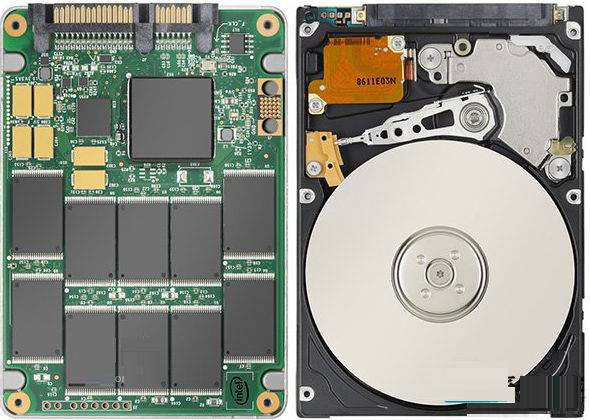

Win10家庭版最终可以暂停更新了 如果计算机硬盘驱动器损坏了,有什么帮助吗?为什么有人买了坏硬盘?注意第四个目的!

如果计算机硬盘驱动器损坏了,有什么帮助吗?为什么有人买了坏硬盘?注意第四个目的! Win7一键重装|计算机系统一键重装win7教程

Win7一键重装|计算机系统一键重装win7教程

比数量