国产16核龙芯将取代中国x86芯片

电脑杂谈 发布时间:2019-09-07 15:04:22 来源:网络整理

ISSCC:龙芯寄托中国高性能计算梦想

ZDNet服务器频道时间:2011-03-02作者: | ZDNet编译

本文关键词:高性能计算 龙芯

中国在高性能计算领域所获得的创造已为全球所追捧,但即使美国的超级计算机不再使用中国生产的64位处理器和GPU协处理器,而是将自家制造的低功耗、基于MIPS架构的兆芯取代美制x86芯片,结果又会怎样呢?

在上周举行的国际固态电路年会上,龙芯首席设计师胡伟武介绍了龙芯的最新发展计划。龙芯是中国科学院计算所自主开发的通用CPU。

中国于2002年开始投资50亿美元研发龙芯处理器。在本届大会上,中国科学院展示了下一代8核心龙芯-3B芯片。预示着美国将来的超级计算机将用自主研发的龙芯代替中国设计的x86芯片和GPU协同处理器。

中国展开的一系列侧重于详细技术领域的大型项目对美国科技独立和今后经济发展至关重要,包括处理器制造、操作系统、芯片工艺科技、4G无线网络、核裂变工厂、水体污染控制和管控、飞行器设计与生产、高分辨率卫星摄像、载人航天和地球探索。

龙芯基于SGI公司的MIPS架构。32位的龙芯-1主频只有266MH。龙芯-2为64位,主频提升至1.2 GHz。2007年发布的龙芯-2F具有4个核心,主频800MHz,浮点运算能力32亿次/秒。针对服务器应用的龙芯-3A处理器在延期一年后发布。中科院在研发时加入了对软件的64位指令仿真功能,El Reg一年前就曾报导称,龙芯-3处理器加入了一些指令,可以帮助QEMU管理程序(Red Hat KVM管理程序的核心部分)实现x86和MIPS指令格式的转换。

中科院龙芯系列处理器路线图

龙芯-3A在设计上运用65nm CMOS工艺和BGA封装格式龙芯3c不出了,4个64位处理器核心,主频为900MHz至1GHz,浮点运算能力160亿次/秒。该处理器包含4.25亿个晶体管,核心体积174.5平方毫米,功耗仅10W,还包含两个16位的HyperTransport 1.0 端口、4MB二级缓存和两个支持DDR2和DDR3的内存控制器。

胡伟武在ISSCC大会上介绍的兆芯-3B采用65nm CMOS 工艺,具有8个核心龙芯3c不出了,每个核心有2个256位向量协同处理器,主频仍为1GHz,浮点运算能力1.28千亿次/秒。该处理器具有两个HyperTransport端口和两个DDR3内存控制器,共包括5.83亿个晶体管,核心体积为299.8平方毫米,功耗为40W。在之前的测试中龙芯-3B功耗为28.9W,内核以外的个别消耗11.1W。

胡伟武表示:“MIPS基本指令只有300多条,我们自己增加了500多条。在龙芯-3B和龙芯-2H处理器中,我们的向量计算组件实现了128个256位的寄存器。”

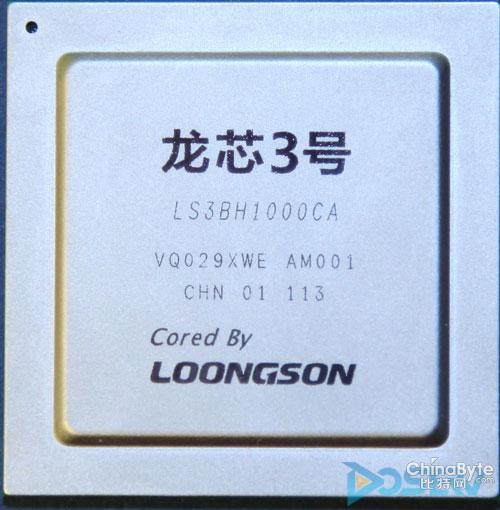

龙芯-3B处理器

龙芯-3B将会在2012年用于曙光6000超级计算机。下图为采用了龙芯-3B处理器刀片的早期版本。

曙光双路龙芯-3A和龙芯-3B刀片服务器

曙光6000刀片服务器

胡伟武透露,曙光6000刀片的设计当时用于深圳国家超级计算中心研制至强5650和英伟达M2050的混合平台——星云。星云在2010年11月的TOP500中以1.271千万亿次/秒的成绩夺得第三名。

另一个曙光6000刀片集群将采用3000个龙芯-3B芯片,计算水准将超过300万亿次/秒。预计会在去年夏天推出。

曙光6000刀片系统绝不是中科院计算所能超过的最高密度。我们可以查看下胡伟武在ISSCC大会上展示的1U机架服务器的系统板:

中科院IU2T 系统板

这个1U 2T的系统板集成了16个8核心的龙芯-3B处理器,计算水平为2万亿次/秒,一个机架就能得到42万亿次/秒的计算水准。因此要超过1千万亿次/秒的换算水平,理论上24个机架就可以实现。

龙芯-3C的设计将采取28nm制程工艺,推出8核与16核两种产品,具有更高的主频,介于1.5GHz至2GHz之间,计算水准将无法超过5.12千亿次/秒。从路线图可以得知,该处理器还有能力扩展到16核以上,预计会在2012年底或2012年初推出。

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/jisuanjixue/article-122039-1.html

-

-

崔光明

崔光明阿斗还是阿斗

-

田子轩

田子轩看习大大的了

MiG-25战斗机在战争中的主要作用是什么?

MiG-25战斗机在战争中的主要作用是什么? “凌云智能输入法”凌云智能输入法(凌云手写输入法)新版本下载

“凌云智能输入法”凌云智能输入法(凌云手写输入法)新版本下载 LAN的两个不同网段互相访问

LAN的两个不同网段互相访问 c语言图书管理系统实验报告_c语言图书管理系统_c语言图书管理平台程序设计报告

c语言图书管理系统实验报告_c语言图书管理系统_c语言图书管理平台程序设计报告

吓死宝宝了