最新网页sdr_sdram_控制器白皮书_中英文对照版本

电脑杂谈 发布时间:2019-08-15 07:06:11 来源:网络整理

SDRSDRAM 控制器白皮书 中英文对照版 SDRSDRAM 控制器白皮书 中英文对照版 翻译:合肥工业大学 检测技术研究所 彭良清(peng6602@hotmail. com) 日期:2004/4/24 原文: Introduction singledata rate (SDR) synchronous dynamic random access memory (SDRAM) controller provides simplifiedinterface industrystandard SDR SDRAM. SDRSDRAM Controller eitherVerilog HDL AlteraAPEX architecture. SDRSDRAM Controller supports followingfeatures: Burstlengths datawords CASlatency clockcycles 16-bitprogrammable refresh counter used automaticrefresh 2-chipselects SDRAMdevices NOP,READA, WRITEA, AUTO_REFRESH, PRECHARGE, ACTIVATE, URST_STOP,and LOAD_MR commands full-pagemode operation Datamask line writeoperations increasesystem performance data-pathwidths 16,32, 64bits Figure system-leveldiagram SDRSDRAM Controller. SDR SDRAM 控制器白皮书 中英文对照版 SDRAMOverview SDRAM high-speeddynamic random access memory (DRAM) synchronousinterface. synchronousinterface fully-pipelinedinternal architecture SDRAMallows extremely fast data rates usedefficiently. Internally, SDRAM devices memory,which column-addressbits banksdepends memory.SDRAM buscommands formedusing combinations RASN,CASN, WENsignals. clockcycle where all three signals associatedcommand operation(NOP). alsoindicated when chipselect asserted.Table standardSDRAM bus commands. SDRAM总线命令 RASNCASN WEN operationNOP ActiveACT ReadRD WriteWR Burstterminate BT PrechargePCH AutorefreshARF Loadmode register LMR SDRAMbanks must openedbefore addressescan readfrom. registeredcoincident ACTcommand. When differentthan currentlyopened. Closing PCHcommand. SDRAM SDR SDRAM 控制器白皮书 中英文对照版 primarycommands used accessSDRAM WR.When WRcommand initialcolumn address dataword registered.When RDcommand initialaddress initialdata appears databus clockcycles later. CASlatency timerequired physicallyread internalDRAM core CASlatency depends memoryclock. morecycles CASlatency required.After initialRD WRcommand, sequential read writescontinue until burstlength BTcommand issued.SDRAM memory devices support burst lengths datacycles. issuedperiodically ensuredata retention. SDRSDRAM Controller user.Functional Description Table SDRSDRAM Controller interface signals. All signals systemclock SDRSDRAM Controller’s outputs. 信号 名称 激活电 描述CLK 时钟 NA Input 系统指针 RESET_N 复位 Low Input 系统复位 ADDR[ASIZE-1:] 存储器地址 NA Input 读如果写时的存储器地址,地址 宽度由ASIZE.增设 CMD[2:] 命令 NA Input 命令请求 CMDACK 命令应答 High Output 命令请求的号召 DATAIN[DSIZE-1:] 输入数据 NA Input 输入数据引脚,间距由DSIZE设 DATAOUT[DSIZE-1:]输出数据 NA Output 数据数据引脚structs控制器,间距由DSIZE设 DM[(DSIZE/8)-1:]数据屏蔽 High Input Masks individual bytes during data write SA[11:] 地址引脚 NA Output SA[11:]信号在ACT命令发出时 锁存到行地址中structs控制器,SA[n:]在 RD/WR命令期间锁存到列地址 中,其中“n”值取决于使用的 SDRAM容量,SA[10]信号在 PCH命令时被采样,该信号决定 是否对所有存储体还是对指定 存储器(由信号BA[1:]决定)进 行预充电。

地址输出在LMR命令 时提供操作码。 BA[1:] 体选地址 NA Output 该信号决定了在ACT, RD, WR, 或PCH 命令时,选择那种储存 LowOutput SDRAM chip selects. SDRAM片选信号, CKE 时钟使能 High Output SDRAM 的CKE信号输入 RAS_N 行地址选通 Low Output SDRAM 命令输入 CAS_N 列地址选通 Low Output SDRAM 命令输入 WE_N LowOutput SDRAM 命令输入 SDR SDRAM 控制器白皮书 中英文对照版 .DQ[DSIZE-1:]数据引脚 NA SDRAM数据引脚 DQM[(DSIZE/8)-1:] 数据屏蔽写 High Output SDRAM 数据屏蔽,在数据写器 件屏蔽单个字符数据 NA: SDR SDRAM 控制器白皮书 中英文对照版 SDRAMController Command Interface SDRSDRAM Controller provides synchronouscommand interface severalcontrol registers. Table commands,which followingsections. followingrules apply Allcommands, except NOP, useronto CMD[2:]; ADDR setappropriately requestedcommand. controllerregisters nextrising clock edge controllerasserts CMDACK oneclock period WRITEAcommands, usershould start receiving writingdata usermust drive NOP onto CMD[2:]by nextrising clock edge after CMDACK 接口命令Command Value Description NOP 000b 空操作 READA 001b 带自动预充电的SDRAM 读操作 WRITEA 010b 带自动预充电的SDRAM 写操作 REFRESH 011b SDRAM 自动刷新 PRECHARGE 100b 对SDRAM 所有存储体预充电 LOAD_MODE 101b SDRAM 模式寄存器装入r. LOAD_REG1 110b 装入控制器配置寄存器 LOAD_REG2 111b 装入控制器刷新周期寄存器 NOP Command NOP operationcommand controller.When NOP followingclock cycle. NOPmust followingclock cycle after controllerhas acknowledged NOPcommand has SDRAMaccesses progress.SDR SDRAM 控制器白皮书 中英文对照版 READACommand READAcommand instructs SDRSDRAM Controller burstread memoryaddress specified SDRSDRAM Controller issues ACTIVATEcommand SDRAMfollowed READAcommand. readburst data first appears DATAOUT(RCD SDRSDRAM Controller asserts CMDACK. During READAcommand usermust keep DM low. When full-pagemode, READAcommand becomes READ (READ without auto-precharge). Figure exampletiming diagram READAcommand. followingsequence describes generaloperation READAcommand: userasserts READA, ADDR SDRSDRAM Controller asserts CMDACK simultaneouslystarts issuing commands SDRAMdevices Oneclock after CMDACK usermust assert NOP CMDACKpresents firstread burst value readbursts follow every clock cycle WRITEA Command WRITEAcommand instructs SDRSDRAM Controller burstwrite memoryaddress specified SDRSDRAM Controller ACTIVATEcommand SDRAMfollowed WRITEAcommand. firstdata value burstsequence must ADDRaddress. hostmust start clocking data along desiredDM values SDRSDRAM Controller (tRCD clocksafter SDRSDRAM Controller has acknowledged WRITEAcommand. See SDRAMdata sheet datamask lines DM/DQM. When SDRSDRAM Controller full-pagemode WRITEA becomes WRITE (write without auto-precharge). Figure exampletiming diagram WRITEAcommand. followingsequence describes generaloperation WRITEAcommand: userasserts WRITEA, ADDR, firstwrite data value desireddata mask value SDRSDRAM Controller asserts CMDACK simultaneouslystarts issuing commands SDRAMdevices Oneclock after CMDACK userasserts NOP userclocks data datamask values SDRSDRAM Controller through DATAIN DMSDR SDRAM 控制器白皮书 中英文对照版 SDRSDRAM 控制器白皮书 中英文对照版 REFRESHCommand REFRESHcommand instructs SDRSDRAM Controller ARFcommand heSDRAM. SDRSDRAM Controller acknowledges REFRESHcommand CMDACK.Figure exampletiming diagram REFRESHcommand. followingsequence describes generaloperation REFRESHcommand: userasserts REFRESH CMDinput SDRSDRAM Controller asserts CMDACK simultaneouslystarts issuing commands SDRAMdevices userasserts NOP CMDSDR SDRAM 控制器白皮书 中英文对照版 PRECHARGECommand PRECHARGEcommand instructs SDRSDRAM Controller PCHcommand SDRSDRAM Controller acknowledges PCHcommand alsoused burststop SDRAM.Using PRECHARGE onlysupported full-pagemode. Note SDRSDRAM Controller adds latencyfrom when hostissues SDRAMsees PRECHARGEcommand full-pageread burst stoppedafter 100 cycles, PRECHARGEcommand must clocksbefore desiredend burst(CL SDRAMdevices). So CASlatency PRECHARGEcommand must issued(100 92clocks burst.Figure exampletiming diagram PRECHARGEcommand. followingsequence describes generaloperation PRECHARGEcommand: userasserts PRECHARGE SDRSDRAM Controller asserts CMDACK simultaneouslystarts issuing commands SDRAMdevices userasserts NOP CMDSDR SDRAM 控制器白皮书 中英文对照版 10 LOAD_MODE Command LOAD_MODEcommand instructs SDRSDRAM Controller LMRcommand SDRAMmode register must LOAD_MODEcommand. mappeddirectly SDRAMpins A11-A when SDRSDRAM Controller issues SDRAM.Figure exampletiming diagram. followingsequence describes generaloperation LOAD_MODEcommand: usersasserts LOAD_MODE SDRSDRAM Controller asserts CMDACK simultaneouslystarts issuing commands SDRAMdevices Oneclock after SDRSDRAM Controller asserts CMDACK, usersasserts NOP CMDLOAD_REG1 Command LOAD_REG1command instructs SDRSDRAM Controller internalconfiguration register REG1. REG1must ADDRinput simultaneously commandLOAD_REG1. Table bitassignments REG1.CL CASlatency SDRAMmemory clockperiods memorydevice speed grade clockfrequency. Consult SDRAMdata sheet appropriatesettings. CL must samevalue SDRAMmemory devices. SDR SDRAM 控制器白皮书 中英文对照版 11 RCD CASdelay clockperiods SDRAMspeed grade clockfrequency. RCD INT(tRCD/clock_period),where tRCD valuefrom SDRAMdata sheet clockperiod SDRSDRAM Controller SDRAMclock. RRD RASdelay clockperiods. RRD SDRAMspeed grade clockfrequency. RRD= INT(tRRD/clock_period), where tRRD valuefrom SDRAMdata sheet clockperiod SDRSDRAM controller SDRAMclock. PM pagemode bit. SDRSDRAM Controller operates non-pagemode. SDRSDRAM Controller operates page-mode.See Section “Full-Page Mode Operation” page14 moreinformation. BL burstlength SDRAMdevices have been configured REG1比特定义 Label ADDR Bits Description CL [1:] CAS latency setting. RCD [3:2] RAS CASdelay clocks.RRD [7:4] REFRESH command duration clocks.PM SDRSDRAM Controller mode, pagemode. BL [12:9] Burst length, valid values LOAD_REG2Command LOAD_REG2command instructs SDRSDRAM Controller internalconfiguration register REG2. REG2 16-bitvalue periodbetween REFRESH commands SDRSDRAM Controller issues. equationint(refresh_period/clock_period). SDRAMdevice connected SDRSDRAM Controller has 64-ms,4096-cycle refresh requirement devicemust have REFRESHcommand issued leastevery 64 ms/4096 15.62509μ SDRSDRAM Controller 100MHz clock, maximumvalue REG2must ADDRinput simultaneously commandLOAD_REG2. SDRAM Device Initialization SDRSDRAM Controller Configuration SDRAMdevices SDRSDRAM Controller must initializedbefore initializationprocess sets burstlength, CAS latency, burst type, operationmode SDRAMdevices. After SDRAMdevices SDRSDRAM Controller’s configuration registers must SDRAMdevices SDRSDRAM Controller, perform followingsteps: PRECHARGEcommand (see “PRECHARGE Command” LOAD_MODEcommand (see “LOAD_MODE Command” SDRSDRAM 控制器白皮书 中英文对照版 12 LOAD_REG2command (see “LOAD_REG2 Command” page10) LOAD_REG1command (see “LOAD_REG1 Command” SDRSDRAM Controller consists fourmain modules: SDRAMcontroller, control interface, command, datapath modules. SDRAMcontroller module top-levelmodule threelower modules wholedesign together. controlinterface module accepts commands relatedmemory addresses from host,decoding commandmodule. commandmodule accepts commands addressesfrom controlinterface module, propercommands datapath module handles datapath operations during WRITEA READAcommands. SDRAMcontroller module also instantiates CLOCK_LOCKmode SDRSDRAM Controller easilyremoved. Figure SDRSDRAM Controller block diagram. SDR SDRAM 控制器白皮书 中英文对照版

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/jisuanjixue/article-119302-1.html

-

-

郎句筵茶

郎句筵茶么么哒小男神

-

甄妮

甄妮事情没调查清楚你就发布这样误导性的信息

Linux和UNIX的关系及区别(详解版)

Linux和UNIX的关系及区别(详解版) 冯凯

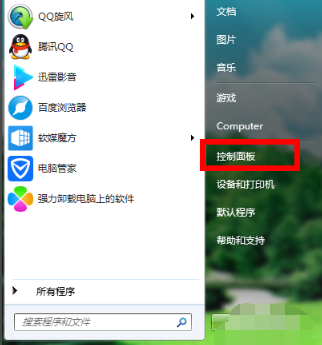

冯凯 屏保界面一些功能的设置方法教你如何设置电脑图解

屏保界面一些功能的设置方法教你如何设置电脑图解

卧槽新歌