不懂就要看哦~~

电脑杂谈 发布时间:2019-06-03 04:11:03 来源:网络整理

具体如下:计数器从0开始上升沿计数,计数达到n-1上升沿时,输出时钟需翻转,由于分频值为n-0.5,所以在时钟翻转后经历 0.5个周期时,计数器输出时钟必须进行再次翻转,即当clk为下降沿时计数器的输入端应为上升沿脉冲,使计数器计数达到n而复位为0重新开始计数同时输出时钟翻转。导读:23、一个电子系统中需要三种时钟,24、一个电子系统中需要三种时钟,设计实验与考核1、设计一个带计数使能、同步复位、带进位输出的增1六位二进制计数器,计数结果由共阴极七段数码管显示。如果要实现占空比为50%的三分频时钟,可以通过待分频时钟下降沿触发计 数,和上升沿同样的方法计数进行三分频,然后下降沿产生的三分频时钟和上升沿产生的时钟进行相或运算,即可得到占空比为50%的三分频时钟。

计数器是一种能够记录脉冲数目的装置,是数字电路中最常用的逻辑部件。计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能。计数器由基本的计数单元和一些控制门所组成,计数单元则由一系列具有存储信息功能的各类触发器构成。计数器在数字系统中应用广泛,如在电子计算机的控制器中对指令地址进行计数。

计数器按进位制不同,分为二进制计数器和十进制计数器;按运算功能不同,分为加法计数器、减法计数器和可逆计数器。下面我们以T触发器构成二进制加法、减法计数器为例介绍计数器的原理。

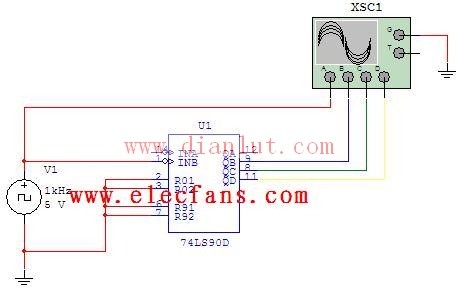

用T触发器构成二进制加法计数器,如下图所示。

3位二进制加法器

如上图所示,是由3个下降沿触发的T触发器组成的3位二进制异步加法器,图中各个触发器的J、K输入端的输入信号均为1,主要由脉冲信号控制其输出信号,计数器从Q2 Q1 Q0 =000状态开始计数计数器电路的分频。

从中可以发现,因为计数器是通过时钟上升沿计数,因此可以在计数为n- 1时对计数触发时钟进行翻转,那么时钟的下降沿变成了上升沿。具体如下:计数器从0开始上升沿计数,计数达到n-1上升沿时,输出时钟需翻转,由于分频值为n-0.5,所以在时钟翻转后经历 0.5个周期时,计数器输出时钟必须进行再次翻转,即当clk为下降沿时计数器的输入端应为上升沿脉冲,使计数器计数达到n而复位为0重新开始计数同时输出时钟翻转。因为计数器是上升沿触发计数,如果在计数值=n-1时把计数器的触发时钟翻转,则时钟的下降沿就变成了上升沿。

74161具有异步清零功能,如图4.6.2所示当计数器接收从秒脉冲计数输出的分信号,输出1111状态(十进制数15)时输出端经过与非门之后产生一个低电平,使74161清零端有效,之后立即返回到0000状态,状态1111仅在瞬间出现一下,这样就构成了15进制计数器。 54/74h538 的功能 1 0 0 x 1 5 稳定状态 1 0 x 1 1 4 下降沿触发 低脉冲 高脉冲 下降沿 0 1 3 上升沿触发 低脉冲 高脉冲 1 上升沿 1 2 复位清零 1 0 x x 0 1 q反 q tr-反 tr+ rd反 功能 输出 输入 序号 2、单稳态触发功能 如序号2、3所列,当tr-=1时,tr+加上升沿触发信号,Q端能输出一个正脉冲信号,Q为负脉冲。 1 0 0 x 1 5 稳定状态 1 0 x 1 1 4 下降沿触发 低脉冲 高脉冲 下降沿 0 1 3 上升沿触发 低脉冲 高脉冲 1 上升沿 1 2 复位清零 1 0 x x 0 1 q反 q tr-反 tr+ rd反 功能 输出 输入 序号 1、清零功能 如序号1所列,当rd=0时,不论其它输入引脚为何种状态,输出端Q立即出0,Q出1,故RD的清零具有最高优先级功能。

如果将T′触发器之间按二进制减法规则连接,就可以得到二进制减法计数器。根据二进制减法计数规则。若低位触发器已经为0,则再输入一个减法计数脉冲后应翻转为1,同时向高位发出借位信号,使高位翻转。

3位二进制减法器

上图就是按上述规则接成的3位二进制减法计数器。图中采用上升动作的D触发器接成的T′触发器,其中所有D触发器的D= Qˉ即成为T′触发器。它的时序图如下图所示计数器电路的分频。

计数器原理介绍完了,下面为大家推荐几篇计数器的

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/jisuanjixue/article-103282-1.html

-

-

零之使魔

零之使魔呵呵三个霉菌的狗

-

王熊

王熊按现有利率算放银行一年死期也就200块钱吧

电脑开机滴滴滴的响,一长两短是怎么回事啊

电脑开机滴滴滴的响,一长两短是怎么回事啊 学校图书馆管理平台分舞计

学校图书馆管理平台分舞计 二叉排序树(查询、插入、删除)

二叉排序树(查询、插入、删除) 聚焦于企业SaaS搜索引擎AI智能云站的推广与发展

聚焦于企业SaaS搜索引擎AI智能云站的推广与发展

不过也不必反应过度