FPGA的基本内部结构是什么

电脑杂谈 发布时间:2020-06-04 16:26:27 来源:网络整理

FPGA的基本组件是: 可编程I / O单元,基本可编程逻辑单元,嵌入式RAM块,丰富的布线资源,底层嵌入式功能单元和嵌入式专用硬核等.

1. 可编程的I \ O单元:

可编程I / O单元可以通过软件适应不同的电气标准和物理特性.

2. 基本的可编程逻辑单元:

基本的可编程逻辑单元是FPGA可编程逻辑的主体. FPGA通常基于SRAM技术. 基本的可编程逻辑单元几乎由一个查找表(LUT,LookUpTable)和一个寄存器(Register)组成. FPGA内部的LUT通常有4个输入,主要用于完成纯组合逻辑功能. 内部寄存器结构非常灵活,可以配置为具有同步,异步复位或设置,时钟使能的触发器(FF,FlipFlop)或锁存器(Latch). FPGA通常依靠寄存器来完成同步顺序逻辑设计.

经典的基本可编程逻辑单元的配置是一个寄存器和一个查找表. 但是,不同厂商的寄存器和查询表的内部结构不同,寄存器和查询表的组合方式也不同.

(1)Alerta的可编程逻辑单元通常称为LE(LogicElement,逻辑单元),它由一个寄存器和一个LUT组成. 大多数Altera FPGA将10个LE结合在一起以形成更大的逻辑功能单元-逻辑阵列模块(LAB,LogicArrayBlock). 除了LE之外,LAB还包含LE之间的进位链,LAB控制信号以及本地Wire和控制资源,例如互连线路资源,LUT级联链和寄存器级联链.

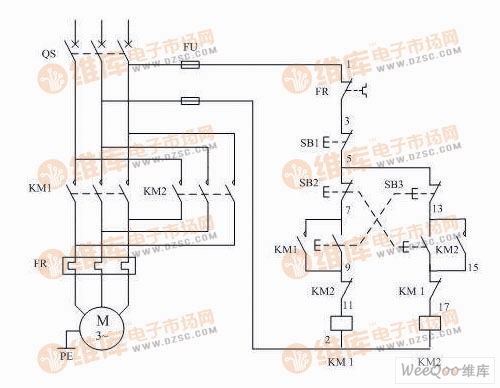

(2)Xilinx的可编程逻辑单元称为Slice逻辑控制电路 互锁,它由两部分组成. 每个部分都由一个寄存器和一个称为LC(LogicCell)的LUT组成,并且两个LC之间存在一些共同的逻辑. 可以完成LC之间的协调和级联.

(3)莱迪思的可编程逻辑单元称为PFU(ProgrammableFunctionUnit,可编程功能单元),它由8个LUT和8-9个寄存器组成.

设备的寄存器和LUT的数量通常用于衡量设备的大小.

3. 嵌入式RAM块:

FPGA的嵌入式RAM块可以灵活配置为单端口RAM(SPRAM,SinglePortRAM),双端口RAM(DPRAM,DoublePortRAM),伪双端口RAM(PseudoDPRAM),CAM(ContentAddressableMemory),FIFO( FirstInputFirstOutput),等等. 内存结构.

FPGA中没有专用的ROM硬件资源. 实现ROM的想法是将初始值分配给RAM并保留初始值.

CAM,内容地址存储器. CAM存储器的每个存储单元都包含一个嵌入式比较逻辑. 将写入CAM的数据与CAM中存储的每个数据进行比较,并返回与端口相同的所有内部数据的地址.

简而言之,RAM是一种根据地址读写数据的存储单元,而CAM返回与端口数据匹配的内部地址.

FPGA中RAM,ROM,CAM,FIFO等的内部存储结构基于嵌入式RAM块,并根据要求自动生成相应的粘合逻辑(GlueLogic),以完成地址等控制逻辑和芯片选择.

Xilinx的常见RAM块大小为4Kbit和18Kbit. 莱迪思常用的RAM块大小为9Kbit. Altera的RAM块是最灵活的. 一些高端设备同时包含两个RAM块结构,分别是M9KRAM(9Kbit)和M-144K(144Kbit).

除RAM外,Altera,Xilinx和Lattice的FPGA还可以灵活地将LUT配置为RAM,ROM和FIFO等存储结构. 该技术称为分布式RAM.

4. 丰富的布线资源

布线资源连接了FPGA内部的所有单元. 连接的长度和过程决定了连接上信号的驱动能力和传输速度. 有以下三种接线资源.

(1)全局专用路由资源: 用于完成设备中全局时钟和全局复位\设置的路由.

(2)长线资源: 在设备组之间完成一些高速信号和一些第二全局时钟信号的接线.

(3)短期资源: 完成基本逻辑单元之间的逻辑互连和布线.

(4)基本逻辑单元中有各种布线资源和控制信号线,例如专用时钟和复位.

5. 底层嵌入式功能单元

高度通用的嵌入式功能模块,例如PLL(PhaseLockedLoop),DLL(DelayLockedLoop),DSP和CPU等.

Altera芯片集成了PLL,Xilinx芯片主要集成了DLL,莱迪思的新型FPGA同时集成了PLL和DLL,以满足不同的需求.

Altera芯片PLL模块分为增强型PLL(EnhancedPLL)和快速PLL(FastPLL).

Xilinx芯片DLL的模块名称是CLKDLL. 在高端FPGA中,CLKDLL的增强模块是DCM(数字时钟管理器,数字时钟管理模块).

6. 嵌入式特殊硬核

嵌入式专用硬核的通用性相对较弱逻辑控制电路 互锁,并非所有FPGA器件都包括硬核.

FPGA内也有两个阵营: 一方面,FPGA用途更广,目标市场非常广泛,价格适中;另一方面,FPGA更具针对性,目标市场明确,价格也更高.

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/dianqi/article-233780-1.html

中国火箭炮_美国火箭炮m270_m207火箭炮

中国火箭炮_美国火箭炮m270_m207火箭炮 西门子 Siemens XQG80-WM12P2609W 使用说明书

西门子 Siemens XQG80-WM12P2609W 使用说明书 载风扇线圈价格规格

载风扇线圈价格规格 tlc固态硬盘寿命 TLCSSD时代是否到来?现在已有7款SSD上市

tlc固态硬盘寿命 TLCSSD时代是否到来?现在已有7款SSD上市

等得太久了