MOS管开关时功率电阻波形的问题?

电脑杂谈 发布时间:2020-01-23 18:02:09 来源:网络整理

多谢邀请,说真心不给出电路图和电阻阻值,仅凭着一张电流电阻波形图很难猜测。不过看小标题既然软开关概念,我认为需要是讲软开关实现原理。我才学能源电子只是两三年,响应老带新,新带萌的口号,我认为我成为一名电力电子新手也能带带萌萌哒的题主,同时分享一下我对软开关(Soft Switching)技术的了解。当然这些简单的普及材料显然有不少谬误,欢迎各位指正。

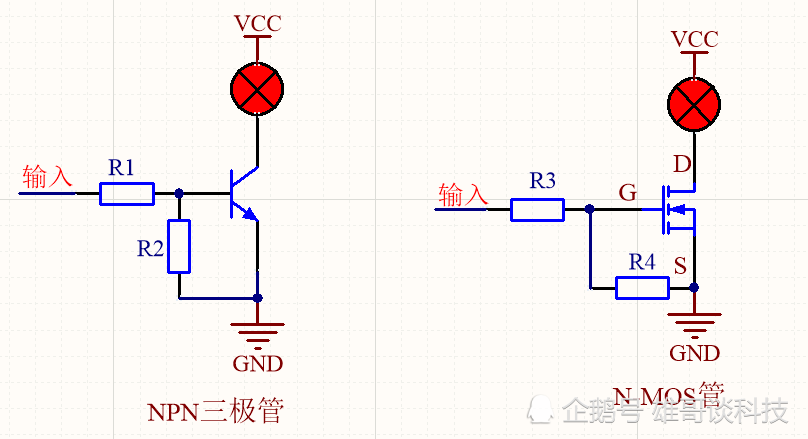

首先我们来解释楼主问题,为什么在Vce下降前ic就开始飙升了呢?

图1

这里就用MOSFET代替BJT了,所以ids = ic,Vds=Vce,Coss也就是Cds代表输出电容。简单来说就是当MOS管一开始导通时输出电阻Coss还保持Vds电压,随着Ids电流越来越大,Vds电压已经维持不住,开始减弱。直到管子完全进入。比较具体的打开过程是由Miller Plateau造成的,这里借用了网上一些解释Miller Plateau的图,如果有不知道的就请见谅了。

阶段1,Vgs < Vth,管子是关断的,所以Ids = 0,Vds=high,ig充电Cgs。

阶段2,Vgs > Vth,管子进入,Ids从0增加至iL被内部电流源电感钳住,Coss(Cds)上电压不能突变,保持Vds。

阶段3,进入Miller plateau,Vgs > Vth,管子依然保持打开,Coss开始discharge,Vds电压开始减弱,于此同时Cgd开始被ig充电。Vg保持不变。

阶段4,Vd下降至接近0点,ig继续给ig充电Cgs和Cgd充电。

阶段5,Vg到达gate driver预定的电压,管子进入过程完成。

关断过程跟开启过程类似,也会有Miller plateau效应。

我们可以发现,如果如果MOS管开启时VDS上有原始电压,那么MOS开启过程中经常有Ids和Vds的重叠,那么会带给Switching Loss。由于Coss上的能量在极短时间内被积聚,电容上能量会代价掉(换算为Loss为0.5*Coss*Vds^2*fs),而且即使是非零电压开启(Non Zero Voltage Switching),会给PCB和MOS的寄生电阻与电感产生的谐振腔(resonant tank)引入非常大的dv/dt或者di/dt激励,引起相当大的ringing,甚至达到管子的额定功率,烧毁管子。

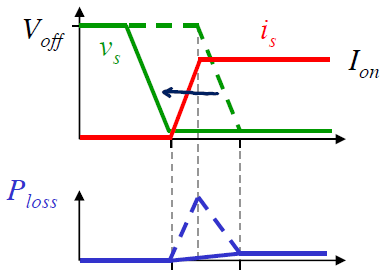

那么我们可以避免这种状况的出现吗?答案是可以的,也就是很提到的Zero Voltage Switching,虽然会付出一定的损失。我们先看怎么可实现软开关开启Zero Voltage Switching Turn on。

图2

实现ZVS turn on很简单,只应该在我们进入管子前,Vds上的电压为零就好,这样Ids和Vds就没有重叠了,turn on switching loss为零,没有high di/dt, dv/dt问题,没有ringing,完美!那么怎样实现ZVS turn on呢?个人认为分两种状况探讨:1为PWM converter,2为resonant converter(谐振变换器)。

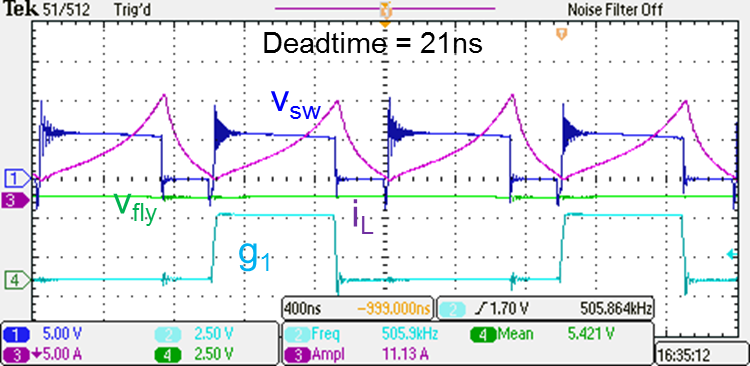

一, 对于PWM converter,就拿更简洁的两个管子的half bridge(其实也就是buck converter)做举例。

图3

对于half bridge 实现ZVS turn on,我们期望当上管Q1开启时电流是流进switching node (vsw)的,也就是图中电感电压为负值,当下管Q2开启时我们期望电流是流出switching node (vsw)的,也就是电感电流为正值。为什么这样就可以实现ZVS turn on了呢?我们就看上管Q1开启过程。如果电感电压iL为负,这时候我们先关闭Q2,这时候Q1还已进入,在这个deadtime中iL会charge Q2的Coss,使Vsw抬高至Vin,当然不能超过Vin,因为Q1的body diode会导通,钳位住Vsw到Vin,这时候Q1的Vds就是Vin-Vsw=0,这时候我们进入Q1就推动ZVS了。同理对于Q2开启时,如果电感电压为正,那么当我们首先关闭Q1管时,Vsw就会被电阻电流拉低到0,因为iL>0, Q2的Coss会discharged到0,然后我们再进入Q2,就可以超过ZVS了。这里我有一张其他Topology的PWM converter的波形图,也跟buck工作原理类似,大概可以看看基本原理,也就是电感电压为负时,Q1可以实现ZVS,让Vsw的ringing比较小。而当电容电压为正时,实现不了ZVS,Vsw的ringing就非常大了。

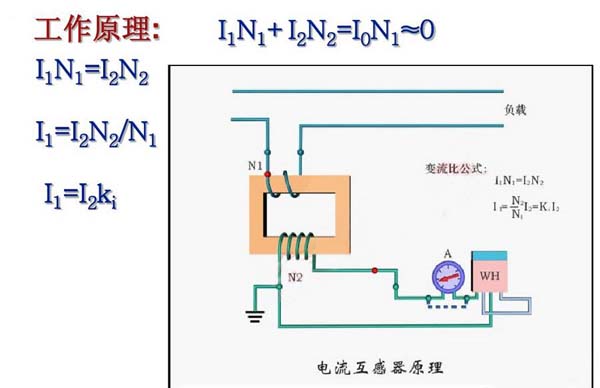

图4

二, 对于resonant converter,其实道理类似,我们也期望在我们进入管子前,Vds上的电压为零。那么针对resonant converter的half bridge,我们希望看到的impedance为inductive,也就是感性的,这样switching node流出的电阻I就会滞后于电流V,现在ZVS turn on。

图5

这是因为如果电阻I是滞后与电流V的,这样在Q1开启之前电流I为负值就会charge Q2的Coss,同时discharge Q1的Coss,让V到Vin,这样Q1就实现ZVS turn on了。Q2开启之前,电流I为正,也会discharge Q2的Coss,和charge Q1的Coss,让V到0,这样Q2就实现ZVS了。

总结起来,要实现ZVS turn on,对于PWM,需要电感电压为负,而且必须足够的deadtime;对于resonant converter,需要impedance为inductive,而且也必须deadtime。那么有人可能应问,对于PWM converter到底电感电压为多负?deadtime至少为多少可以确保ZVS?对于resonant converter, impedance 到底为多少?deadtime为多少可以保证ZVS?

要提问这个定量问题,其实是不这么简单的。对于PWM converter,参考quasi-square-wave

ZVS buck converters,我们是可以画出state plane,然后按照state plane图的几何关系定量分析出来的,但是比较枯燥,常常是七八个三角函数等式求解。所以我个人看法,在设计上,就让开关频率小点,电感值小点,让电容电压ripple足够大,能超过负值就差不多了。对于resonant

converter,倒是可以简单地借助积分方式,算出i与t的积分,让这个it积分大于Coss上的charge就行。比如已知impedance,算出V与I的phase shift,然后换算成时间td,然后在td上对电感电压进行积分,只要这个积分高于等于Coss*Vin就行了。

图6

说了soft switching, ZVS这么多好处,我们说说soft switching的好处。对于PWM converter我们可以提到为了推动ZVS,我们增加了电阻值,让电容电压ripple变大,最终超过负值,实现了ZVS,但是付出的损失就是inductor current的RMS值变大,各个元器件的导通损耗(conduction loss)变大,所以我们是牺牲了conduction loss换取switching loss和小ringing。而且即使输出电流越大,我们必须推动ZVS的难度更大,需要进一步减弱ripple,造成RMS电流进一步减弱,很有也许得不偿失,造成converter整体强度减弱。对于resonant converter,在速率很大的状况下,有时候需要使impedance非常inductive,也就是I滞后于V非常厉害才能有足够的charge q来实现ZVS,这似乎只是变相减少了有功功率的存储,因为V跟I的phase lag比较大,造成了converter的circulating current比较大,RMS电流值增大,也是减小了conduction loss。所以在设计以及考量ZVS等soft switching时必须对平台有个整体loss的把握,在conduction loss和switching loss之间做好trade-offmos管开关电压,这样就能设计出强度最高,最鲁棒的converter。

另外soft switching软开关技术还有ZVS turn offmos管开关电压,Zero Current Switching turn on,Zero Current Switching turn off。这里就简单介绍了ZVS turn on,因为ZVS turn on对于MOSFET跟GaN比较重要,其他softswitching技术这里就不一一描述了。

原创不易,虽然并非soft switching的普及材料介绍,但也期望对一些电路萌新玩家有些帮助。请勿转载,谢谢。

本文来自电脑杂谈,转载请注明本文网址:

http://www.pc-fly.com/a/dianqi/article-137939-1.html

玉林横山LDZ-10 II高精度电流互感器有优惠吗?

玉林横山LDZ-10 II高精度电流互感器有优惠吗? 苏州大金空调售后维修电话(全国联保服务)网点

苏州大金空调售后维修电话(全国联保服务)网点 如果无法在计算机上读取硬盘该怎么办?

如果无法在计算机上读取硬盘该怎么办? 冰箱必须注意这些要点,否则新更换后仍然会损坏

冰箱必须注意这些要点,否则新更换后仍然会损坏

喜欢哈哈